近十年来,随着非易失性存储器概念的发展,解决方案变得越来越复杂,以适应嵌入式系统市场的多种使用模型。

因为技术特性和成本效益的优势,非易失性存储器特别是NAND和NOR两种闪存产品,在不同的应用市场取得空前的成功。此外,为克服技术限制,追随技术进步,NAND闪存控制器架构需要与闪存芯片并行化发展,在存储器芯片上实现高效的数据管理。

为确保存储器的简易移植,降低存储控制器的复杂程度,增加非易失性存储器特性变化的透明度,可管理的存储器概念在很多应用中已变为现实,如汽车、工业、手机和无线通信领域。

可管理的存储器概念的问世来自一个简单的想法:把存储控制器的一些智能转移到存储器上。采用一个可管理的存储器的直接效果包括:闪存技术变化不影响整个存储系统变化;功能差异化;因为重新给存储器分配任务而使得存储器控制器软件负荷减轻。

闪存技术概况

非易失性存储器经历了一个快速发展阶段,并产生了各种独特的技术和架构,能够适应不同的应用领域。

其中,闪存技术非常普及,并取得巨大成功。

闪存技术基本上代表了一类电可擦写非易失性存储器,即使断电或外部控制器关断电源,闪存也不会丢失片内保存的数据。沿两条不同的路线发展进化,闪存产生了两个不同产品家族:NOR和NAND闪存。

闪存采用浮栅技术把微小信息保存在存储单元内,在浮栅技术的发展过程中,光刻技术节点被连续地缩小,使芯片尺寸越变越小,成本效益不断提高。每个存储单元可以存储一个位的信息(单级单元,简称SLC)或多个位的信息(多级单元,简称MLC)。

存储单元排列在一起,构成存储阵列,NOR和NAND拥有不同的存储阵列结构。每个阵列又组成块。NAND闪存的块由页组成。表1所示是NAND和NOR闪存的基本区别,其中考虑到了最新缩小的技术节点。

技术上的差异预示着应用上的差异。NOR闪存的快速读取性能特别适用于实现片内执行代码(XiP)技术,这种非易失性存储器用于系统的执行代码内存或系统启动内存。

NAND的写吞吐量和高密度使其成为大容量存储应用的必选方案,但是NAND的应用范围逐渐扩大到代码存储应用领域,比如NAND闪存用于保证代码(操作系统代码、应用软件)存在,在多片存储解决方案中,代码往往被下载至执行内存内(通常是一个RAM)。

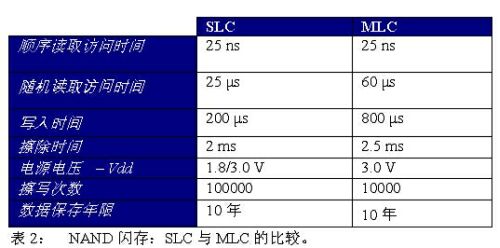

目前大多数可管理的存储器解决方案都基于NAND闪存技术。NAND闪存技术可再分为两种类型:单级单元和多级单元。表2概述了采用相同单元光刻技术的两类存储器的某些差异。

两类存储技术的基本差异表明,SLC可能更适用于存储和下载代码,因为读取性能和耐擦写能力更加优异,而MLC NAND则是所有大容量存储应用的最佳解决方案。

NAND闪存错误管理机制和数据管理

1.擦写粒度不同。一颗NAND闪存芯片必须以页为单位进行读写操作(不过,每个厂商都准许SLC NAND支持数量有限的局部读写操作,并对此进行了详细规定)。擦除操作以块为单位。此外,每页在写数据前必须先进行擦除操作,因此,抽象物理层接口需要一个从逻辑到物理的重新映像策略。

2.擦写循环次数。擦写操作基于一个破坏存储单元的物理原理(采用高压的Fowler-Nordheim隧道技术),因为这种方法冲击存储阵列(位、页或块),所以,擦写循环的次数将受到限制(故称为器件耐擦写能力)。为延长存储器的使用寿命,推荐使用一个均衡使用阵列物理位置的技术(在整个阵列上分配擦写操作)。

3.位修改。在读写操作过程中,某些技术限制可能导致一定数量的位被修改,利用错误检测纠正算法可以使这些位恢复正常,使SLC NAND的擦写循环达到100,000次,MLC NAND的擦写循环达到10,000次。在一次页读取操作过程中,这些算法可以检测和校正一定数量的位错误。校正能力(最大可校正位数量)是一个由厂商定义的参数,因为这个参数与技术的关系非常密切,光刻技术节点缩小可能会改进这个参数。

4.坏块。在完成制造阶段后,某些阵列位置可能会被破坏,导致芯片上出现所谓的坏块。坏块分类如下:

出厂后坏块:因制程而引起的外部应用不能使用的闪存坏块。当产品出厂时,块 ‘0’始终是正常块(例如,用于存储引导代码)。

在使用过程中变成坏块的块:当擦写操作失败时,就会发现这些块是坏块。为保证内容的完整性,必须更改含有内容的块,把内容复制到另一个存储位置。

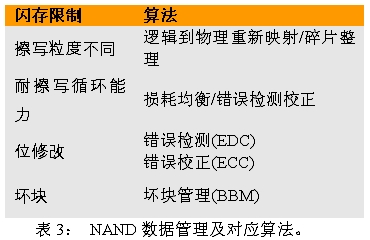

如果系统含有一个存储数据和代码的NAND闪存,设计人员就必须采用一个适合的闪存数据管理机制,以解决所有这些技术限制。数据管理是一套用软件程序或硬件块实现的算法(见表3)。

可管理的存储器概念

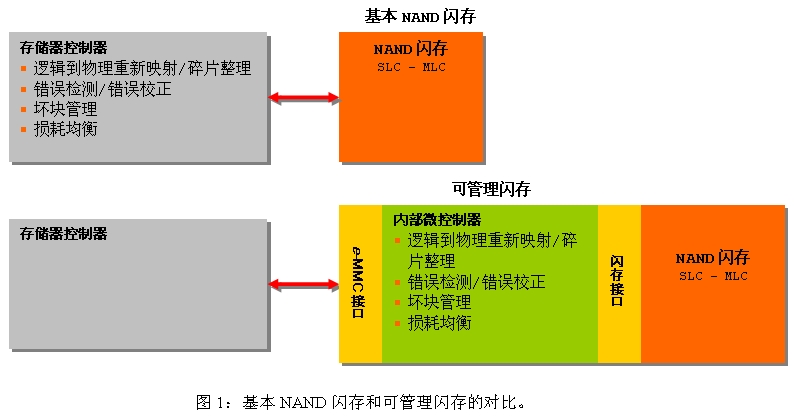

在NAND闪存技术的发展过程中,存储器控制器曾呈现日益复杂化趋势。为解决这个问题,可管理的存储器解决方案近年来在不同的系统中日渐盛行。这种解决方案有以下几个主要特性:内部架构由控制器和闪存芯片组成;闪存数据管理算法嵌入在系统内,由内部控制器执行;标准化接口,可与外部存储器控制器通信,例如,e-MMC(JEDEC组织定义的多媒体卡接口)定义了总线特性和通信协议;附加特性(在写操作过程中发生断电事件时可保护数据完整性的安全算法等)(见图1)。

本文小结

选用可管理的非易失性存储器解决方案具有明显优势和直接效果,体现在:NAND闪存技术变化不影响整个系统;闪存厂商独立共存;移植性;互操作性;存储控制器上软件负荷降低;可扩展性。

概括地说,与非易失性存储器技术变化(光刻节点缩小、更高的查错和纠错要求和存储2位以上信息的多级单元)相关的一些因素,必然导致使用控制器解决所有这些技术问题,因此可管理的存储器概念应运而生。

此外,市场对手机产品和无线通信系统的需求越来越高,例如要求更高的传输带宽、更低的功耗、不同使用模式共存(即代码执行和海量存储)等等。存储器控制器可以满足这些需求,在一个专用架构内,存储器控制器能够适时地管理闪存芯片。