1 引言

嵌入式系统的终端显示倾向选择LCD显示器。但在大屏幕显示情况下,大型工业级LCD液品显示器造价高。选择性少。而为嵌入式系统增加标准VGA接口可很好地解决该问题。支持VGA接口的显示设备众多且价格相对较低,而且显示设备的更换不会对嵌入式系统产生影响。ARM9器件S3C2410在嵌入式系统中应用广泛。这里主要针对该处理器介绍基于CH7004的嵌入式系统VGA接口设计。该设计方案硬件设计和软件实现简单,成本较低,从而为嵌入式设备提供了简单有效的大屏幕图像显示解决方案。

2 VGA接口

VGA(Video Graphics Array)是一个模拟信号接口,是IBM公司推出的一种视频传输标准。该接口具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。

(1)VGA接口引脚表1为15针VGA接口引脚信号的定义列表。

(2)VGA接口时序VGA接口有多种时序,应用时根据具体需要选择不同的时序。图1为640×480在60 Hz模式下的VGA接口时序图。

3 器件介绍

3.1 LCD控制器简介

S3C2410处理器采用16/32位指令的 ARM920T内核,最高工作频率为202 MHz,内部带有丰富的外设资源,低功耗、低价格、高性能的特点使其在嵌入式系统中应用广泛。LCD控制器是S3C2410内部集成外设,具有以下特点:支持STN、TFT两种类型液晶显示屏;支持多种颜色模式,最高支持24位颜色模式;LCD控制时序可由用户根据实际情况需要设置。

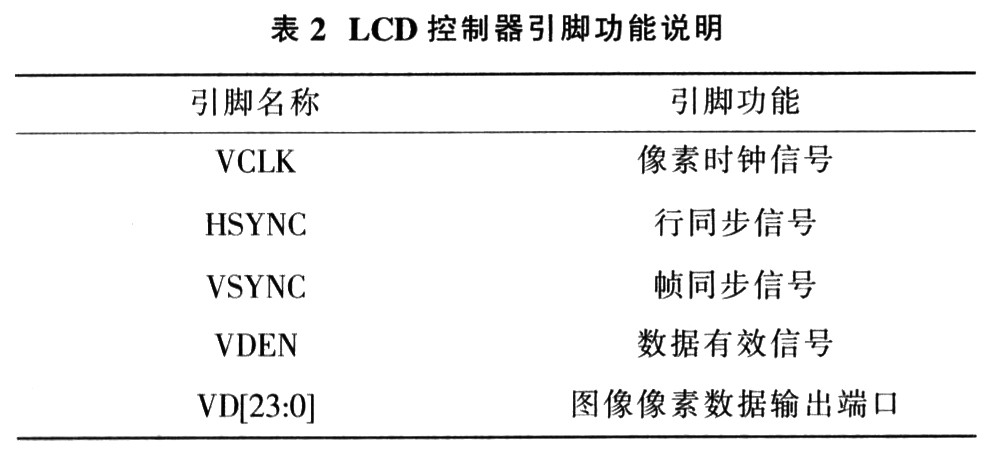

3.1.1 LCD控制器引脚功能

LCD控制器引脚分为时序控制端口和数据端口。与该设计相关的端口具体含义见表2。

3.1.2 LCD控制器内部控制寄存器

LCD控制器内部有5个控制寄存器:LCDCON1~LCD-CON5。LCDCON1控制像素时钟、扫描模式和颜色模式;LCDCON2控制帧同步脉冲宽度、帧有效行数及帧同步前、后的无效行数:LCDCON3主要控制行有效像素点数以及行同步前、后的无效像素点数:LCDCON4主要控制行同步脉冲宽度:LCDCON5主要控制行、场同步脉冲和数据有效信号极性,16位色颜色格式.数据输出与像素时钟跳变关系。

3.2 CH7004器件简介

CH7004是Chrontel公司生产的一款数字转换为模拟的视频编码器,其内部编码器支持NSTL、PAL两种视频制式,通用数字输入接口支持8、 12、15、16和24位数字RGB或者YCrCb格式输入,支持5种图像分辨率,内部集成3路相互独立的高速视频数模转换器,可由用户控制输出模拟 RGB或YUV,提供I2C接口供用户控制器件工作模式。

4 VGA接口设计

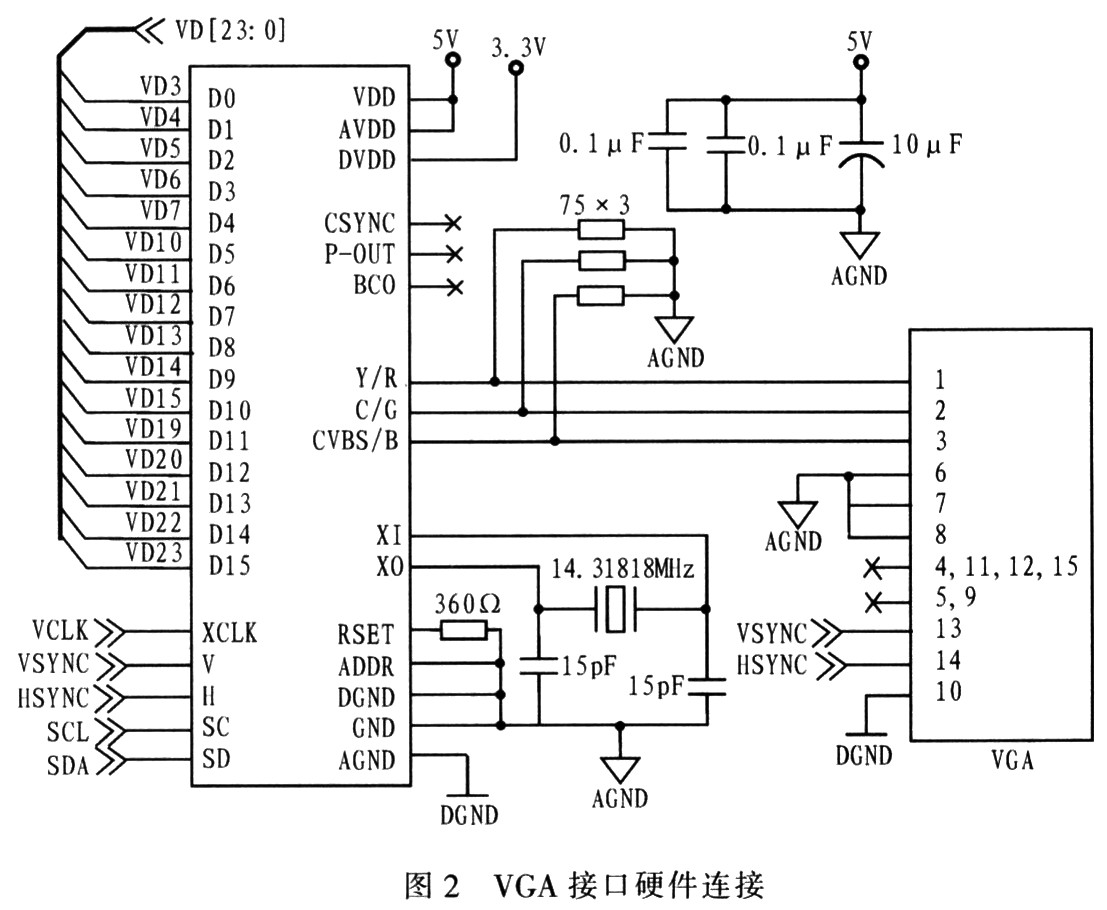

S3C2410处理器的LCD控制器用于产生图像数据、VGA接口时序(640x480,60 Hz)以及配置CH7004的工作模式。CH7004将数字图像数据模拟化,最终产生的模拟图像信号供支持VGA接口的显示器显示。VGA接口的硬件连接见图2。

这里选择(640x480,60 Hz)模式,是由实际需要和硬件特性决定的:(1)嵌入式系统中的图像尺寸大多低于640x480,采用这种VGA模式显示不会丢失任何原始图像信息; (2)VGA的每种显示模式所要求的像素时钟不同,而S3C2410内部LCD控制的像素时钟由器件的主频分频而来,在各种分频后的像素时钟里只有25. 25 MHz(202 MHz主频进行8分频)与VGA模式中的(640x480,60 Hz)模式所要求的像素时钟25.175 MHz最为接近,微小的像素时钟偏差不会影响VGA接口显示;(3)16位色情况下,(640x480,60 Hz)模式数据流带宽为35.2 MB/s,因而不会堵塞S3C2410数据总线,不影响处理器的其他控制、数据处理操作。

CH7004的数据输入端口D0~D15与LCD控制器的相应数据输出端口连接,LCD控制器的像素时钟VCLK通过XCLK端输入CH7004内部, ADDR为低设置CH7004的I2C总线地址,为0x76。CH7004输出端需考虑视频信号阻抗匹配问题,否则会出现图像重影、雪花、或边缘有波纹等问题。

5 LCD控制器和CH7004配置

5.1 LCD控制器的设置流程

将LCD控制器工作模式设置为(640x480,60 Hz),16位色(5:6:5),TFT模式。

(1)将系统主时钟(FCLK)设置为202 MHz,外设时钟(HCLK)设置为101 MHz;

(2)将LCD控制器外部端口设置为TFT作模式;

(3)开辟1块大小为600 KB(640x480x2 Bytes)用于存放数据的连续内存区域;

(4)设置LCD控制器的控制逻辑寄存器LCDCON1~LCD-CON5。其中,LCDCON1:设置像素时钟(VCLK)从系统主频分频的分频系数 CLKVAL=1,VM的触发速率为每帧触发,显示模式TFT,单像素颜色位数16位.禁止LCD控制器数据输出和控制信号产生ENVID=0; LCDCON2:设置帧同步后无效行数VBPD=32,帧有效行数LINEVAL=469;帧同步前无效行数VFPD=9,帧同步宽度VSPW=1; LCDCON3:行同步后无效像素点数HBPD=47,行有效像素点数HOZVAL=639,行同步前无效像素点数HFPD=15;LCDCON4:行同步宽度HSPW=95;LCDCON5:图像在内存的存储方式设置为小端存储BPP24BL=0.16位色图像为5:6:5格式FRM=1,像素时钟 VCLK设置为上升沿传输一个像素数据,行同步脉冲设置为负脉冲有效INVVUNE=1,帧同步脉冲设置为负脉冲有效IN-VFRAME=1,LEND信号极性设置正常模式INVLEND=0,PWREN信号设置有效设置PWREN=1,LEND信号输出为允许ENLEND=1。

(5)允许视频数据输出和时序控制ENVID=1。

5.2 CH7004工作模式配置

CH7004C内部有25个工作模式控制寄存器。与此设计模式相关的寄存器有4个:显示模式寄存器(Display Mode),输入数据模式寄存器(Input Data Format),时钟模式寄存器(Clock Mode),同步信号极性寄存器(Sync Polarity)。通过配置CH7004内部工作模式控制寄存器的使CH7004与LCD控制器工作相对应。

将CH7004 工作模式设置为与国LCD控制器相一致。图像大小为640x480,输入数据为16位5:6:5格式.数据不经制式编码器而直接送人内部D/A转换器。对 CH7004的配置顺序为:(1)Display Mode寄存器设置640x480显示模式,可选择的模式为13~17。(2)Input Data Format寄存器设置为16位色。RGB5:6:5格式,RGB信号旁路。选择旁路模式使得RGB输入图像信号不经视频编码器而直接送入D/A转换器。 (3)Clock Mode寄存器设置为像素时钟上升沿锁存图像信号。(4)Sync Polarity寄存器设置行、场同步负脉冲有效,行、场同步信号由外部处理器产生并南CH7004的V、H端口输入。在实际操作中,系统上电后,处理器只需配置CH7004内部的输入数据模式(Input Data Format)寄存器,其他寄存器直接使用复位默认值。

5.3 CH7004的I2C总线配置时序

S3C241O配置CH7004的I2C总线的步骤:(1)在I2C总线上首先产生CH7004片选地址0x76和读写位(0:写;1:读);(2)产生某一寄存器的片内偏移地址;(3)产生配置数据。PC控制器一个操作步骤结束后,必须等获得CH7004发出正确操作答复,才能继续执行下一步操作。图3 为CH7004的I2C读写时序图。

6 测试与结论

实验证明.色条图像通过VGA接口在显示器上显示效果良好。介绍的VGA接口设计方法使用S3C2410处理器和CH7004视频编码器件,具有硬件设计、软件实现简单,价格低廉的特点。为嵌入式设备提供了简单有效的大屏幕图像显示解决方案。