随着通信技术的发展,传统的模拟对讲机已不能满足人们的需求,对讲机数字化势在必行。信息社会的高速发展使频谱资源变得愈加宝贵,信道利用率成为一项关键因素。如何在有限的信道资源下,通过压缩信源以提高传输效率,已成为当前急需解决的问题之一。DSP数字信号处理器的运算能力越来越强,本设计采用TI公司的通用定点DSP TMS320C5509A作为基带系统的处理器,主要对G.723.1语音压缩编码在频带、DSP资源有限的数字对讲机基带系统中的具体应用进行研究与实现。

1 G.723.1语音压缩编码原理

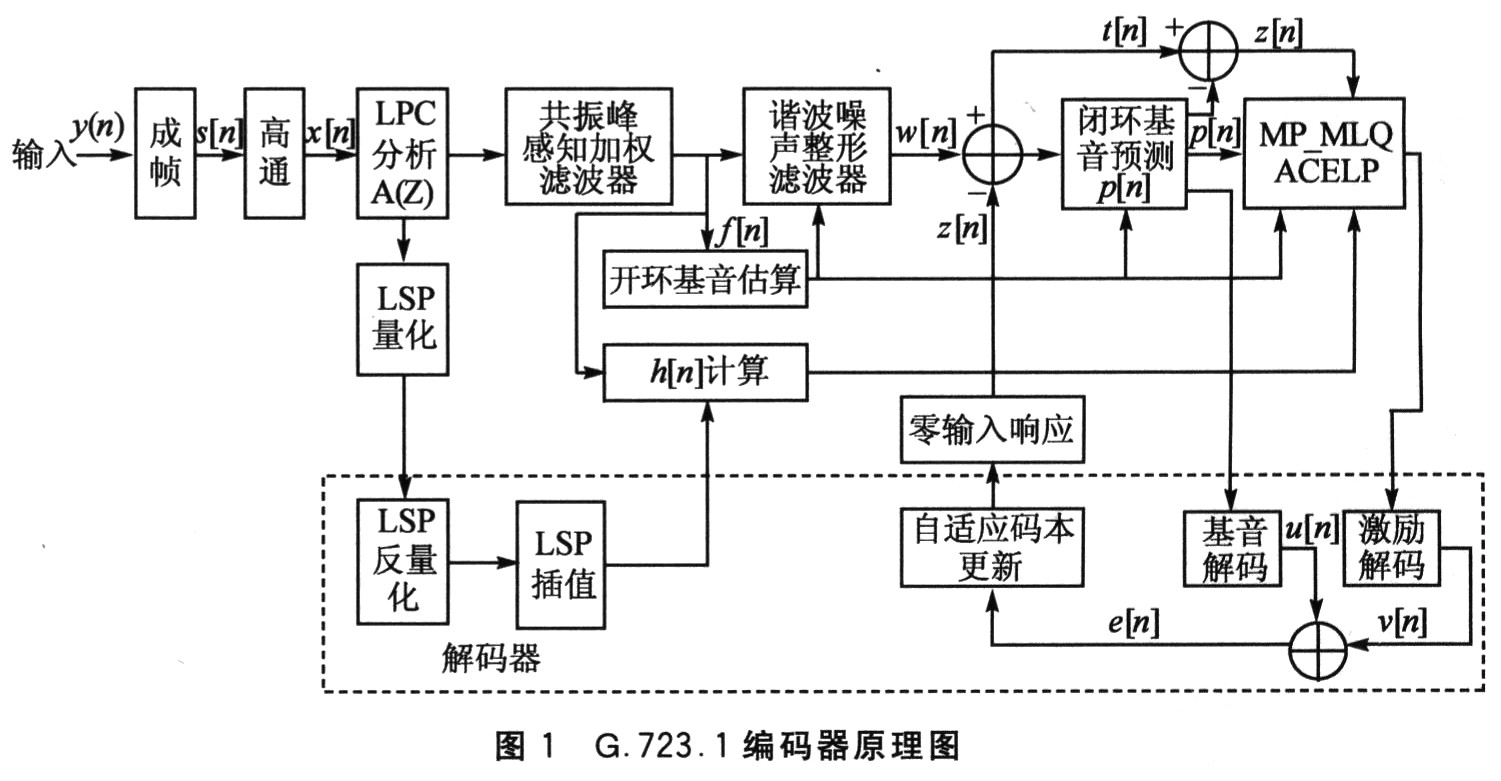

G.723.1标准主要用于对语音及其他多媒体声音信号的压缩。该算法是H.324系列标准的一部分,包含2种工作速率:低速率(5.3 kbps)采用代数码本线性激励预测(ACELP),高速率(6.3 kbps)采用多脉冲激励最大似然量化(MP_MLQ)。2种速率的编码器都以帧为处理单位,帧长为30 ms,加上另需7.5 ms的延时,总共37.5 ms的算法延时。编码器原理如图1所示。

输入的16位线性PC码流分成长度为240样点的语音帧。每帧信号先通过1个高通滤波器,去除低频成分,再分成4个子帧,每个子帧60个样点。对每个子帧进行10阶LPC预测,将最后1个子帧的LPC参数转化成线谱对LSP参数。用预测分裂矢量量化法(PSVQ)进行量化。为了减少合成端合成语音信号的误差,在分析端对LSP系数解码、插值后,再变为LPC系数。由LPC分析后的LPC系数可得到共振峰加权滤波器的系数。用共振峰加权滤波器对经高通滤波后的语音信号进行共振峰加权滤波,可得到共振峰加权滤波后的语音信号f(n)。由f(n)经基音估计可求出开环基音周期,基音周期的搜索范围为18~142 个样点。对每个子帧的语音信号进行谐波噪声整形、冲击响应计算,然后进行闭环基音搜索,求出闭环基音周期及基音增益,再计算出残差信号。然后根据不同的速率进行激励搜索,求出脉冲位置和幅度参数,打包后形成以帧为单位的编码数据流。

2 语音系统的结构及硬件原理图

原始的模拟语音首先要经过模数变换,转化为数字信号之后,通过串口输入到DSP中,再进行语音压缩算法。G.723.1标准计算复杂和数据存储量大的问题使得语音编解码方案的实时实现存在很多困难。为了保证该算法处理的实时性,本系统选用 DSP作为主控芯片,用来实现编解码算法。语音系统整体硬件结构如图2所示。

3 语音系统的硬件设计

本基带系统的核心部件采用CPLD和DSP。DSP负责基带的数字化处理,CPLD用于外围器件的控制。将CPLD和DSP技术相结合,一方面能利用DSP软件控制的灵活性,另一方面又能利用CPLD硬件上的高速、高集成度和可编程性。

本系统选用TMS320C5509A(简称C5509A)负责G.723.1标准的算法及后续基带数字化的处理(信道编译码、交织、加扰、CRC、基带调制解调)。该芯片是TMS320C55X系列DSP中的一款,C55X系列的结构见参考文献[1]。

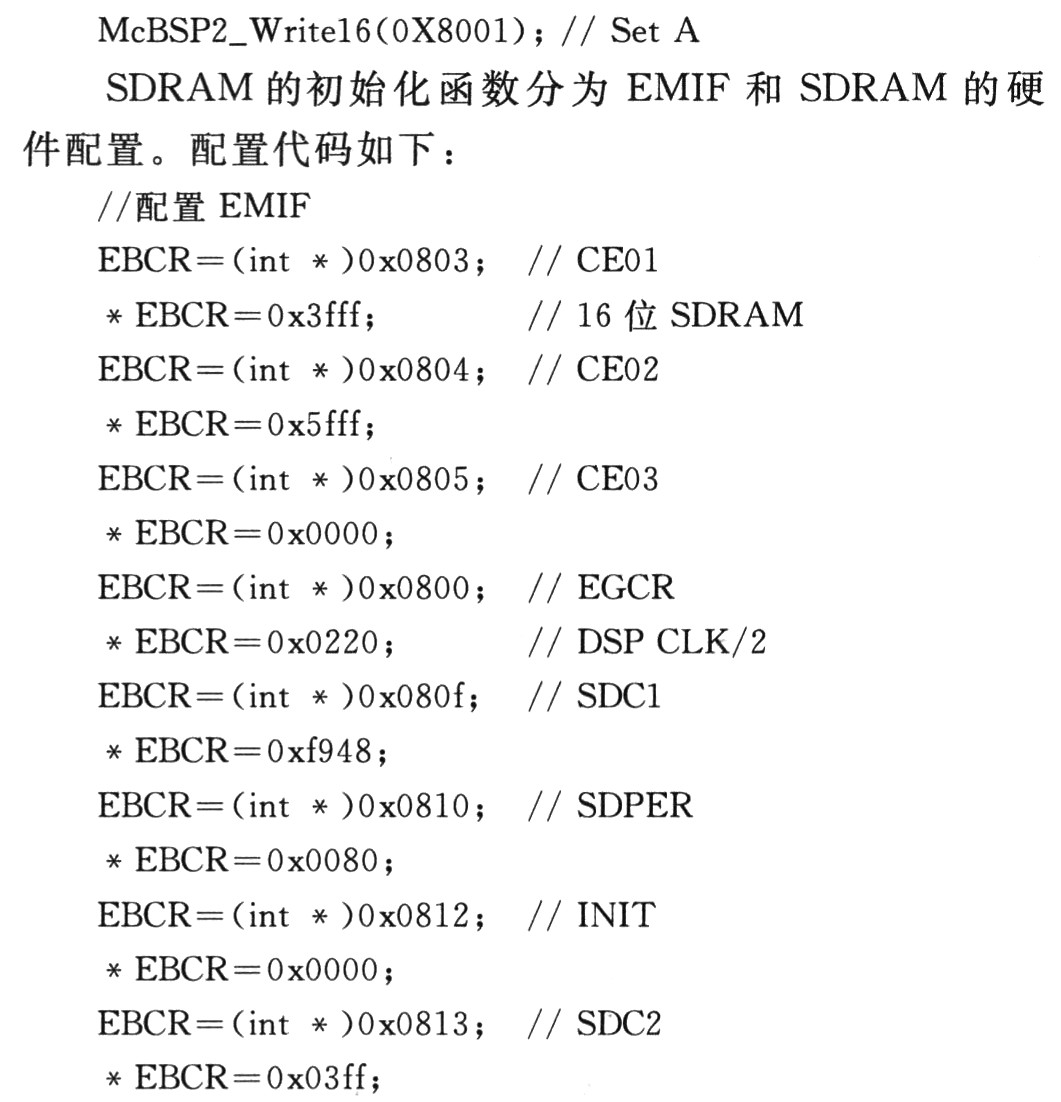

CPLD主要用来扩展DSP的外部地址空间,实现地址译码、时序控制,并给DSP提供所需的逻辑和时序控制信号。本系统选用Altera公司 MAX7000系列中的EPM7128,其与DSP的接口电路如图3(a)所示,其中FSX和FSR帧同步信号端的同步信号相同。原始模拟语音信号必须进行数字化处理后,才能在DSP中进行语音压缩编解码算法。系统选用的是ADI公司推出的低成本、低功耗通用模拟前端AD7311L,其与DSP的接口电路如图3(b)所示。由于G.723.1的算法比较复杂,处理时需要大量的存储空间,本设计采用4Mb×16的SDRAM,芯片为MT48LCM16,通过 EMIF接口映射到C5509A的CEO空间。其与DSP的接口电路如图3(c)所示。Bootloader模块的主要

4 语音系统的软件设计

总体软件流程如图4所示。当DSP处于发送状态时,通过MCBSP1接收来自 AD7311L的数字化语音数据,调用语音压缩编码程序,编完1帧输出数据,然后继续进行后续的相关基带处理。当DSP处于接收状态时,接收来自后续基带处理的数据,调用语音解码程序;解码后的语音数据,再以每帧的数据通过MCBSP1送入AD7311L,最后还原成原始语音。下面主要介绍初始化模块及语音编解码模块。

4.1 初始化模块

系统的初始化是系统运行的基础部分,它涉及系统的整体硬件设计,如引脚的分配及连接、各芯片采用的工作模式等问题。本系统初始化模块划分为3个部分:初始化微处理器、初始化语音处理器、初始化外部寄存器。

DSP初始化函数名为DSP_Init.c,主要是对DSP的时钟(clock),外部存储器接口(EMIF)和多通道串行缓冲串口(McBSP)进行初始化设置。

AD7311L的初始化函数主要是对其的外部引脚配置,该模块分为McBSP1的配置和AD7311L的硬件配置。

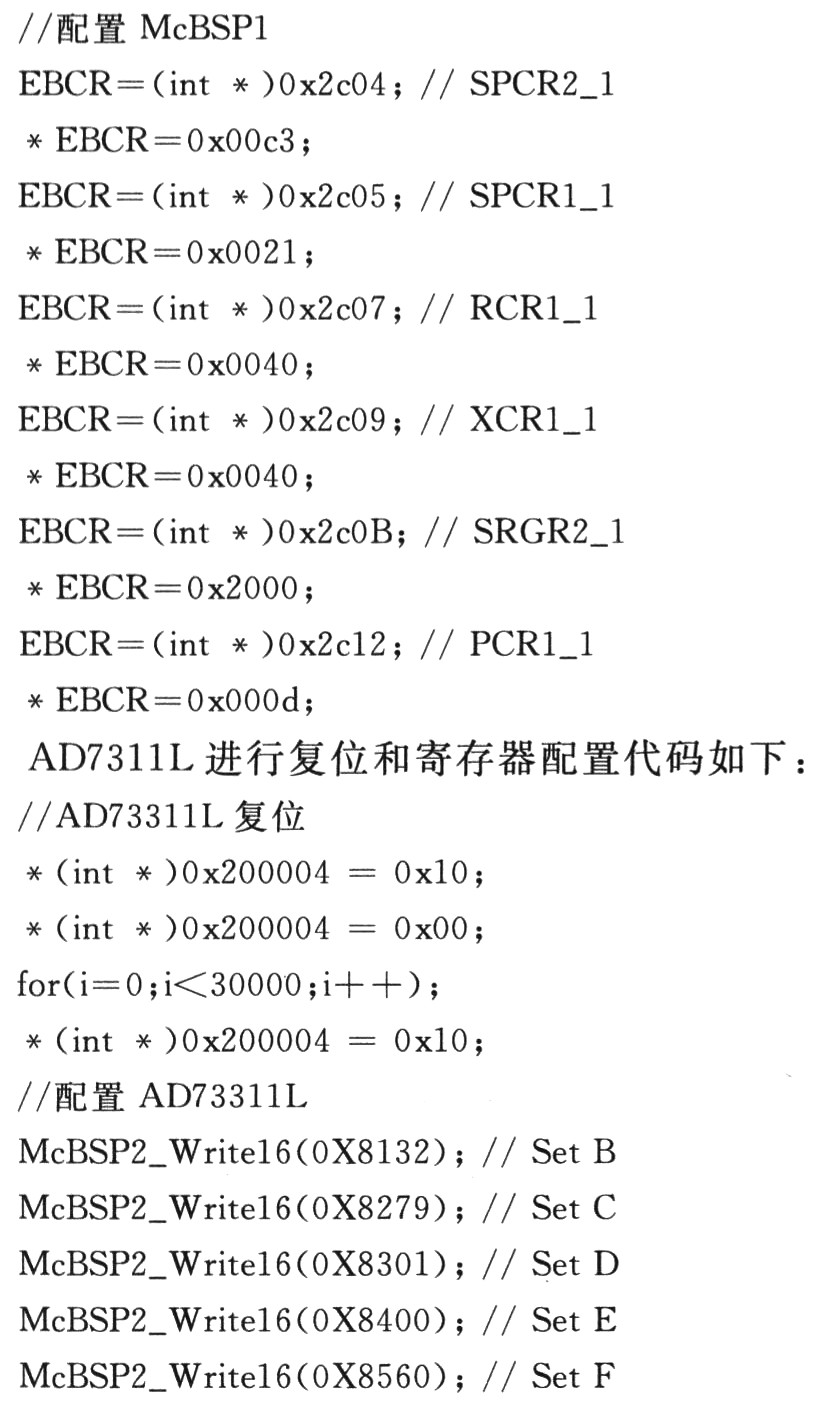

McBSP1的初始化函数如下:

4.2 语音编解码模块

该模块主要是对G.723.1的代码处理。系统若直接使用ITU提供的定点C源代码, C5509A完成1帧的编码需要53 400 912个周期,即使C5509A工作在最高频率200 MHz,也需要267 ms。所以代码必须经过优化,且优化后的代码占用DSP的资源不能过高,这样才能保证DSP有足够的资源对后续的基带数字化进行实时处理。本设计主要从编译器、C语言级、汇编级和算法级4个方面对G.723.1的定点C代码进行优化。本文主要对算法级优化进行介绍。

在对G.723.1算法进行仿真的过程中发现,基音估计、自适应码本搜索、固定码本搜索和代数码本搜索等模块占语音编解码的总时间超过70%,因此优化措施应着重对这几个模块的算法进行优化。

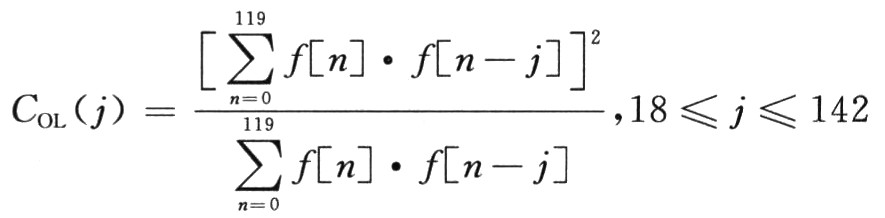

①开环基音估测函数Estim_Pitch()中,计算图1f[n]中的互相关值COL(j):

寻找使得COL(j)max,开环基音周期j的搜索范围18~142。在基音周期较短时,基音频率较大;对语音信号编码质量影响较大,而基音周期较长时,基音频率较小,对语音信号编码质量较小。所以18~58之间基音周期采用逐点计算搜索,而59~142之间以采用隔点计算,可以减少运算量。

②高速率的脉冲激励编码(MP-MLQ)函数Find_Best()中计算预测残差信号![]() 时需要进行卷积码预算,对其进行优化。计算误差信号的均方值时

时需要进行卷积码预算,对其进行优化。计算误差信号的均方值时 ,式中

,式中![]() 先通过加减运算完成,最后做1次增益G的乘法运算即可得到r'[n],这样计算1次残差矢量最多需要60×6=360次加减运算,而优化前的预算量为4×8×(1+2L+58+59)=56 640。由此可见优化减少了大量的运算。

先通过加减运算完成,最后做1次增益G的乘法运算即可得到r'[n],这样计算1次残差矢量最多需要60×6=360次加减运算,而优化前的预算量为4×8×(1+2L+58+59)=56 640。由此可见优化减少了大量的运算。

③基本运算库函数优化。G.723.1代码的基本运算库函数Basop.c中,存在大量数字信号处理功能的函数,而且占据绝大部分运算,如L_mac()、L_mull()、L_add()、sature()等,所以还需在这几个函数上进行一些优化工作。

5 调试结果分析

最终在TMS320C5509A上实时实现G.723.1标准。对于1帧语音在高速率6.3 kbps模式下,编解码算法占用时间7.42 ms,算法复杂度为49.5 MIPS;低速率5.3 kbps模式下,编解码占用时间5.34 ms,算法复杂度35.6 MIPS。

其主要模块代码优化前后占用的时间对比如表1所列。

整个程序优化后,G.723.1算法占用CPU的资源不到20%,即DSP还有足够的资源对后续的基带算法进行处理。

结 语

在工作频率为200 MHz的C5509A自制硬件电路上,实现了对G.723.1标准的实时处理。将2块板子串口相连,收端扬声器可以传出发端传来的实时、连续和清晰的语音。最后优化验证以及整体基带系统的调试结果证明,语音压缩编码方案选用正确,代码优化结果良好,硬件电路设计合理,在频谱带宽、DSP资源有限的条件下,圆满地实现了G.723.1语音压缩编码在对讲机基带数字化系统设计中的应用。从DSP的CPU负载情况看,G.723.1的代码还可进一步优化。若想进一步降低功耗,可采用全汇编实现。