摘 要: 根据USB3.0的发送速率要求和高速串行发送原理,使用Verilog HDL描述语言设计了一种基于多相位技术的USB3.0发送电路。电路各模块在ISE中编译和仿真,给出了电路实现的结构图、模块的接口信号以及部分程序和仿真波形图,并将仿真结果进行比较验证,证明多相位技术设计的电路能满足数据发送的准确性和时序要求。

关键词: USB3.0;多相位技术;Verilog HDL

0 引言

USB(通用串行总线)是一种标准的传输接口[1],从1995年USB1.0版本开始,历经USB1.1、全速USB2.0(FullSpeed)、高速USB2.0(HighSpeed),到USB3.0(SurperSpeed)[2],数据传输速率已经提升至5 Gb/s,相比USB 2.0的480 Mb/s提升了约10倍。从2008年11月首次发布规范以来,USB3.0已经在快速存储、大数据高速传输等领域逐渐展现出强大的竞争力。纵观各个版本的USB硬件设计,USB3.0以其高达5 Gb/s的I/O转换速率给设计者带来了很大的难题,同时,功耗的控制也成为需要考虑的重要环节。本文将介绍多相位技术的一种应用,实现电路复杂度、实用性以及功耗方面的平衡。

1 发送电路的功耗分析

目前,数字集成电路普遍采用CMOS工艺。COMS工艺的功耗估算[3],以反相器为例,设电路的工作频率为f,其中每个周期的一半时间![LE}`RWXT278VNNYMZ)@]NX2.png LE}`RWXT278VNNYMZ)@]NX2.png](http://files.chinaaet.com/images/2016/02/19/6359151089429900001879833.png) 是通过PMOS管对负载电容器充电。若此时的电源电压为Vdd,记电容器上的实时充电电压为V,由于充电电流

是通过PMOS管对负载电容器充电。若此时的电源电压为Vdd,记电容器上的实时充电电压为V,由于充电电流![B51AF@7D7C_4J){)[2G4G]8.jpg B51AF@7D7C_4J){)[2G4G]8.jpg](http://files.chinaaet.com/images/2016/02/19/6359151087365600007855297.jpg) ,那么,这一期间转移到电容器上的能量为:

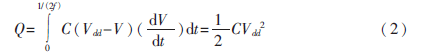

,那么,这一期间转移到电容器上的能量为:![$C]1N[UODA6B00Z3]RT`]}H.jpg $C]1N[UODA6B00Z3]RT`]}H.jpg](http://files.chinaaet.com/images/2016/02/19/6359151088523800002741648.jpg) ,将上式代入得到能量转移为:

,将上式代入得到能量转移为:

这是一个经典的估算公式。同一期间PMOS管能量消耗为:

上述两项是相等的。同样,NMOS管能量消耗与电容器上存储的能量相等。因此,一个反相器平均动态功率消耗大致为:P=CfVdd2。

经过上文的分析可知,降低CMOS电路功耗的三种主要途径为:降低电源电压Vdd、改进工艺减少负载电容C以及降低工作频率f。对于USB3.0高达5 Gb/s的串行输出,在供电电压一定、制造工艺相同的条件下进行电路的优化,有效地降低内部器件的工作频率,成为降低功耗的首要之选。

2 发送电路的结构与实现

2.1 发送电路结构

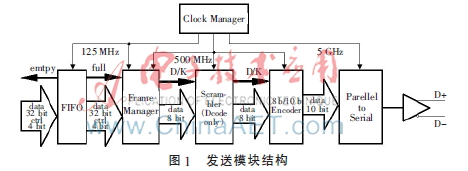

USB3.0发送模块结构如图1所示。

发送电路输入的数据为36 bit位宽,包括32 bit数据和4 bit数据有效控制位;时钟管理模块根据不同的数据位宽,产生不同的时钟,协调各模块的同步运行。

如图1所示,帧管理模块以125 MHz/32 bit的速率从FIFO读取数据并转换成为500 MHz/8 bit数据流传送至扰码模块;扰码模块和8 bit/10 bit编码器模块均采用500 MHz的时钟,对并行8 bit的数据进行处理;经过 8 bit/10 bit编码模块后,数据流变成500 MHz/10 bit,送入并转串模块,最终以差分输出的方式输出串行数据。

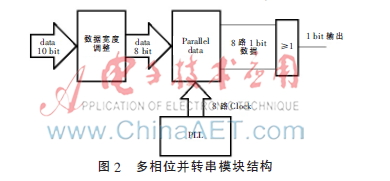

2.2 基于多相位技术的并转串模块结构

并转串模块是结构优化的重点[4]。传统的并转串电路通过移位寄存器实现,在0.15 ?滋m CMOS工艺条件下只能达到3.0 Gb/s的频率,并且所有器件运行在最高工作频率,功耗将非常大。采用多相位技术后,数据位在8个同频不同相的时钟控制下并发处理,电路运行的时钟频率可以降为原先的1/8,显著降低功耗。

并转串模块结构电路如图2所示。

为了适应输入数据的位宽需求,在并转串模块输入端插入一个数据位宽转换模块,将10 bit位宽的数据调整为8 bit位宽,也就是将500 MHz的10 bit并行数据调整为625 MHz的8 bit并行数据流。主要方法为:将500 MHz*10 bit的数据流拼接为125MHz*40 bit的并行数据流,输出则使用625 MHz时钟以8 bit的位宽读出。部分关键代码如下:

reg[39:0] shift_buf40;

always@(posedge clk_500M_i or negedge rstn_i)begin

if(!rstn_i)

shift_buf40<=40′h0;

else//拼接成40 bit

shift_buf40<={shift_buf10,shift_buf40[39:10]};

end

reg stitch_load;//40 bit载入信号

always@(posedge clk_625M_i or negedge rstn_i)begin

if(!rstn_i)

stitch_load<=1′b0;

else if(clk_625M_i)

stitch_load<=~stitch_load;

else

stitch_load<=1′b0;

end

reg[39:0]stitch_buf40;

always@(posedge clk_625M_i or negedge rstn_i)begin

if(!rstn_i)

stitch_buf40<=40′h0;

else if(stitch_load)

stitch_buf40<=shift_buf40;//40 bit载入

else

stitch_buf40<={stitch_buf40[7:0],

stitch_buf40[39:8]};//每个clk移位8 bit

end

assign split_buf8_o=stitch_buf40[7:0];

此段代码实现了不同时钟的数据位宽变换。

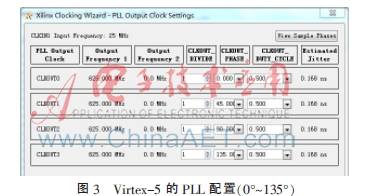

PLL产生8个频率为625 MHz的Clock,相邻时钟间相移为45°,占空比为1:1。通过8输入的或门,在1/8时刻允许8 bit并行数据的某一位数据输出。在此选用Xilinx的Virtex-5系列FPGA进行设计仿真验证,由于单个PLL资源所限,使用2个PLL进行8路多相时钟输出:其中一个PLL产生0°、45°、90°和135°相移,另一个PLL则产生180°、225°、270°和315°的相移,其配置如图3所示。

2.3 并转串模块的电路实现

使用Verilog HDL[5]语言对并转串部分进行描述,部分关键代码如下:

reg sdata_0;

always@(clk_mp045_i or clk_mp090_i)begin

if(clk_mp045_i &!clk_mp090_i)

sdata_0<=pdata_i[0];

else

sdata_0<=1′b0;

end

以上是其中的1/8个数据处理模块,经过ISE综合后得到的RTL电路如图4所示。

电路非常简洁,8个部分结构完全一致,数据发送的精度取决于PLL的相位精度与8个相同结构单元的布线。显然,PLL在625 MHz产生45°的相移间隔可以达到很高的精确度,门电路布线长度的一致性也很容易实现。也就是说该电路布局产生的时延可以做到基本一致,这一点对于高速电路的设计非常有利。

3 仿真及验证

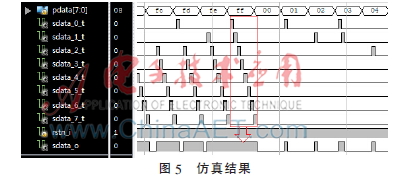

编写test bench,循环发送8′h00~8′hFF数据,在ISim中对设计的多相位发送电路进行仿真验证,仿真波形如图5所示,并转串模块输入的数据为8′hFF,图中矩形框中为经过并转串模块后的8路独立输出,下方箭头指向经过8输入或门处理后的串行输出,结果完全正确,满足USB3.0协议规范要求。

4 结论

多相位技术的应用可以使高速发送电路的大部分器件工作在一个相对较低的频率下,并能在一定程度上降低制作器件的工艺难度。因此,多相位技术对降低功耗、提高性能而言,具有十分重要的现实意义。

参考文献

[1] ANDERSON D, DZATKO D. USB系统体系(第二版)[M].孟文,译.北京:中国电力出版社,2003.

[2] Hewlett-Packard Company, Intel. Universal serial bus 3.0 specification revision1.0[R]. USA: Hewlett-Packard Company, 2008.

[3] 汪小会.集成电路低功耗设计[J].电子工程师,2006(1):9-11.

[4] 亓磊.3.125Gbps高速串行RapidIO数据发送器设计[D].长沙:国防科学技术大学,2010.

[5] 夏字闻.Verilog数字系统设计(第二版)[M].北京:北京航空航天大学出版社,2008.