3nm、5nm制程:复杂且昂贵的争夺战(一)

2020-02-06

来源: EEWORLD

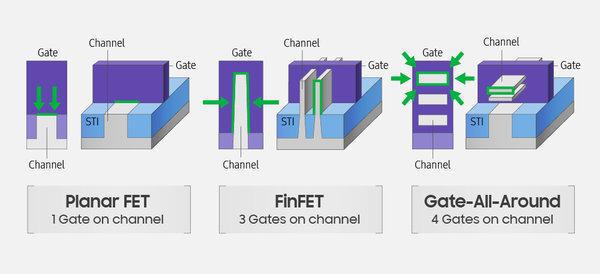

半导体工艺在进入14nm/16nm制程之后,最经常被提到就是鳍式场效应晶体管(FinFET),它的出现满足了7nm至14nm之间的工艺制造。不过在进入更小的5nm、甚至3nm之后,FinFET工艺已经难以满足半导体芯片的制造需求,业界也在对新一代晶体管进行研究。

为此,几大晶圆厂正在市场上加速5nm制程,但现在客户必须决定是围绕当前的晶体管类型设计他们的下一个芯片,还是转移到3nm及以上的不同芯片。

该决策涉及将目前的FinFET扩展到3nm,或在3nm甚至2nm节点上实现一种名为GAA FET的新技术。从FinFET进化而来的环绕闸极可提供更好的性能,但是这些新的晶体管很难制造,价格昂贵,迁移过程可能会很艰难。但有利的一面是,该行业正在开发全新蚀刻、图案和其他技术,这将为这些节点铺平道路。

这些GAA FET的出库时间由各大晶圆厂所决定。三星和台积电都在用FinFET生产7nm制程,他们将在今年晚些时候使用FinFET量产5nm制程,并在5nm左右推出各种半节点产品。这将提高速度和功率。

不过,三星计划在明年或2022年某个时候,在3nm制程上推出一款名为nanosheet FET的GAA晶体管。与此同时,台积电计划首先在3nm制程上引入FinFET。分析师和设备供应商表示,台积电将在3nm或2nm的后期阶段引入全栅结构GAA。

对于新技术而言,台湾知产力专家社群创办人曲建仲介绍,场效电晶体(FET)是最基本的电子元件,是数字信号的最小单位,一个FET代表一个0或一个1,就是电脑里的一个位数。电子流入再流出,由一个闸极开关控制电子导通代表1或不导通代表0,科学家将它制作在硅晶圆上。

“制程节点”代表闸极的“平均长度”,会随制程技术的进步而变小。当晶体管缩小到14nm以下之后,原来的技术不能满足14nm产品的需求,才有了胡正明教授的“鳍式场效电晶体(FinFET)”,但是5nm以下又遇到问题,才出现“环绕闸极场效电晶体”。

然而,台积电(TSMC)仍在评估其3nm制程方案,TSMC将很快披露其3nm计划,计划也可能随时变动。尽管如此,台积电将FinFET扩展至3nm的举措合乎逻辑。转移到新晶体管可能会对客户造成潜在的干扰。但最终,FinFET将会失去它的优势,台积电别无选择,只能全面转向环绕闸极(gate-all-around)。

其他公司也在开发先进制程。英特尔正在加紧10nm和7nm的研发。(英特尔的10nm制程与晶圆厂的7nm制程类似)与此同时,中芯国际正在研发10nm/7nm工艺以此提高16nm/12nm FinFET。

所有的先进工艺都是昂贵的,并不是所有的芯片都需要3nm或其他先进工艺。事实上,不断上涨的成本促使许多人探索其他选择。另一种获得扩展的方法是将高级芯片放入一个封装中,为此一些公司正在开发先进的封装类型。

平面晶体管、场效应晶体管、纳米片场效应晶体管。

缩放比例真的到头了吗?

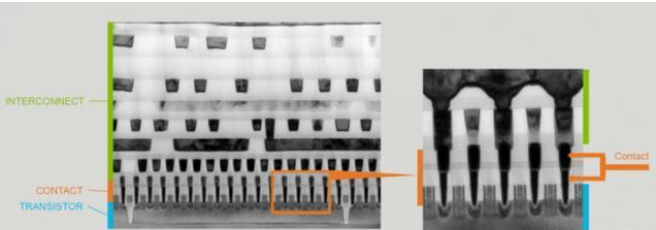

芯片由晶体管、节点和互连线三部分组成。晶体管作为设备开关,如今,先进的芯片有多达350亿个晶体管。

互连线位于晶体管的顶部,由微小的铜线构成,将电信号从一个晶体管传输到另一个晶体管。晶体管和互连线由一层叫做中线(MOL)层连接。中间层使用一系列微小的接触结构连接独立的晶体管和互连件。

传统的集成电路扩展设计方法是缩小每个工艺节点的晶体管规格,并将其封装到一个单芯片上。

为此,芯片制造商每隔18到24个月就会推出一种新工艺技术,其晶体管密度更高。每个进程都有一个数字节点名。最初,节点名与晶体管栅极长度相关。

在每个节点上,芯片制造商将晶体管的规格提高了0.7倍,在同等功率下提高了40%的性能,并减少了50%的面积。所以,芯片缩放使新的电子产品具有更多功能。

当芯片制造商沿着不同的工艺节点前进时,这个公式就起作用了。但在20nm时发生了一个巨大的转折,2D的传统平面晶体管失去了动力。从2011年开始,芯片制造商转向了FinFET,FinFET是类似3D的结构,具有更好的性能和更低的泄漏,使他们能够扩展自己的设备。

然而,FinFET的制造成本更高,导致工艺研发成本飙升。所以现在一个完整的节点的节奏已经从18个月延长到30个月,甚至更长。

在高级节点,英特尔遵循0.7x比例缩小晶体管尺寸的这一趋势,但在16nm、14nm,其他人开始脱离了传统方法和放宽了金属间距。“之前节点名称的使用与被指定的金属间距相关,” “在某些时候,我们开始偏离间距,更着眼于下一个节点和特征尺寸。”

在那时,节点名变得模糊,不再与任何晶体管规格相联系。Gartner分析师Samuel Wang表示:“节点的定义正变得越来越具有误导性和无意义。例如,在5nm或3nm之间,没有单一的几何结构实际上是真正的5纳米或3纳米。另外,供应商之间的流程通用性大大降低。对于同一节点,台积电和三星的表现不同,当然也不同于英特尔。”

高级节点的扩展速度也在减慢。根据IC Knowledge和TEL研究,一般情况下,7nm的代工工艺,它的多晶硅间距CPP在56nm到57nm,金属连线间距在40nm。在5nm处,CPP大约为45nm-50nm,金属间距为26nm。CPP是一个关键的晶体管度量单位,用于测量源极和漏极接触点之间的距离。据悉,三星最近也高调推出了5nm,预计将于2020年上半年量产。与它的7nm相比,三星的5nm FinFET技术,与7nm相比它的速度有25%的增长,功耗降低20%,性能提高10%。

此外,价格/性能优势不再遵循同样的曲线,这促使许多人在怀疑,摩尔定律是否已经走到了尽头。

其实,摩尔定律并不是真正的定律,而是一种观察(observation),它成为一种自我实现的预言,推动半导体行业向前发展。随着多重图案和EUV成本的增加,摩尔定律的经济方面开始衰退。布鲁尔科技公司高级技术专家Douglas Guerrero表示: “计算能力的提高将出现在新的设计和架构中,但这不是可扩展的。这意味着未来的芯片将提高计算能力,但成本不一定会以过去的速度下降。”

对于缩放,它并没有完全消失。人工智能、服务器和智能手机正在推动对高级节点上更快芯片的需求。D2S的首席执行长藤村明(Aki Fujimura)表示,一些人还认为除了新奇的应用程序之外,这个世界已经没有办法处理速度更快的计算了。“今天,对于物联网来说,低成本、足够好的性能和集成胜过更多和更高的计算密度。但我们需要更快的晶体管来制造更高效、更低功耗的,并且能容纳更多晶体管的芯片。”

显然,并非所有的需求都需要高级节点,因为成熟工艺的芯片需求强劲。联华电子联席总裁王季刚(Jason Wang):“这些新产品包括在5G智能手机中使用的RF IC和OLED驱动芯片,以及设计用于计算和固态驱动器应用的电源管理芯片。”

扩展FinFET

与此同时,在芯片扩展方面,芯片制造商多年来一直遵循相同的工艺路线,采用相同的晶体管类型。2011年,英特尔转向了22纳米的FinFET,随后是16 /14纳米的晶圆厂。

在FinFET中,对电流的控制是通过在鳍的三面各安装一个栅极来实现。FinFET有两到四个鳍。每个鳍有不同的宽度、高度和形状。

英特尔的第一代FinFET在22nm处的尾翼间距为60nm,尾翼高度为34nm。然后,在14nm处,英特尔的FinFET的鳍距和高度都是42nm。

因此英特尔将鳍片做得更高更薄,以适应FinFET的规模。林研究大学项目主任Nerissa Draeger在博客中解释: “FinFET缩放减少横向尺寸,以增加单位面积的设备密度,同时增加鳍的高度,以此作为改善设备性能的一种方式。”

在10nm/7nm制程时,芯片制造商采用了相同的方法来扩展FinFET。2018年,台积电推出了首款7nm制程FinFET芯片,三星紧随其后。与此同时,英特尔去年发布了10nm芯片,此前他们曾多次推迟发布。

到2020年,晶圆行业的竞争将更加激烈。三星和台积电正在增加5nm制程和各种半节点制程。3nm正在研发中。

但要记住,所有的过程都很昂贵。据IBS宣称,设计3nm产品的费用约5亿美元到15亿美元,及它的工艺开发费用约40亿美元到50亿美元,而如果要兴建一条生产线的运营成本约150亿美元到200亿美元。IBS的琼斯说:“基于相同的成熟度,3nm的晶体管成本预计将比5nm高出20%到25%。“与5nm FinFET相比,预期性能提高15%,功耗降低25%。

与7nm相比,三星的5nm FinFET技术提供了高达25%的逻辑面积,降低了20%的功耗,可以提高10%的性能。

台积电高级技术总监Geoffrey Yeap在最近的IEDM会议上的一篇论文中表示:相比之下,台积电的5nm FinFET工艺“在同等功率下提供了15%的速度提升,在同等功率下,7nm节点的逻辑密度降低了30%。”

芯片制造商在7nm制程和5nm制程上大做文章。为了使芯片的关键特性定型,这两家公司从传统的193nm光刻技术过渡到EUV光刻技术。由于EUV的波长为13.5nm,简化了这一过程。

EUV并不能解决芯片扩展的所有挑战。应用材料公司图案技术总经理Regina Freed在一篇博客中说:“解决这些挑战需要多种技术,这些技术超越了可扩展的范围,包括新材料的使用、新型嵌入式非易失性存储器和先进的逻辑架构、沉积和蚀刻的新方法,以及包装和芯片设计创新。”

与此同时,三星和台积电正在准备它们的3nm制程。过去,芯片制造商走的是同一条道路,但根据今天的路线图,3nm是供应商们正在分道扬镳的地方。

Garner的Wang表示:" 3nm可能有几种不同的选择,如FinFET和环绕闸极,这为客户提供了成本、密度、功率和性能的不同组合,以满足他们的特殊需求。”

如前所述,三星将在3nm处引入nanosheet FET。台积电也在开发这种芯片,它计划将FinFET扩展到下一代。“台积电将在2021年第三季度推出3nm制程芯片,”IBS的琼斯表示。“台积电的环绕闸极将在2022年或2023年左右推出。”

这就是晶圆代工客户必须权衡各种成本和技术权衡的地方。扩展FinFET似乎是一条更安全的途径。“许多客户认为台积电是一个低风险的供应商。”

然而,环绕闸极在某种程度上提供了更多的性能。Jones表示:“与3nm FinFET相比,3nm 环绕闸极具有更低的阈值电压,并可能降低15%到20%的功耗。”“但性能差异可能在8%以下,因为MOL和BEOL是一样的。”

但要注意,后道(back end of line,BEOL)工艺和MOL是先进芯片的瓶颈。接触电阻是MOL中的一个问题。

BEOL是建立若干层的导电金属线,不同层金属线之间由柱状金属相连。在每个节点上互连变得更加紧密,导致芯片中的电阻-电容(RC)延迟。FinFET和环绕闸极是不同的晶体管类型,但它们很可能在3nm处采用类似的铜互连方案。RC延迟对于两个晶体管来说都是一个问题。

此外还有其他挑战。当鳍片宽度达到5nm时,FinFET将会失去动力。5nm/3nm FinFET正在突破这些限制。

另外,一个3nm的FinFET可能由一个鳍片组成,而其他节点可能有两个或更多的鳍片。Imec的CMOS设备技术总监Naoto Horiguchi:“单鳍必须有足够的操纵灵活性。为了将FinFET扩展到N3,我们需要一种特殊的技术来增强单鳍功率和/或减少后端寄生。”

将FinFET扩展到3nm的一种方法是将锗材料移到p通道。具有高迁移率通道的3nm FinFET将提供性能提升,但存在一些集成挑战。