EDA进入AI设计新纪元:新思科技、Cadence、谷歌和英伟达开始借助AI进行复杂芯片设计

2021-10-09

来源: 电子工程专辑

现今先进的芯片设计可能需要数百名设计工程师,配备最先进的 EDA 设计工具,耗费2-4年时间才能完成。EDA开发厂商和先进AI芯片设计企业开始考虑,让AI来辅助芯片设计是否可以加快设计流程,减少人工和时间等资源的投入?答案是肯定的,如果硬件开发变得更加敏捷和自主,那么昂贵且漫长的芯片设计流程可能会从 2-3 年缩短到 2-3个月。在新一代EDA设计工具中,AI扮演着至关重要的角色。新思科技和Cadence等EDA厂商,以及谷歌和英伟达等AI芯片设计公司已经开始借助AI进行复杂的芯片设计,而且取得了惊人的效果。

芯片设计AI化

去年,新思科技发布DSO.ai(Design Space Optimization AI)软件,可以让IC设计工程师更自主地确定在芯片上排列布局的最佳方式以减少面积和降低功耗,由此开始了EDA设计的人工智能化进程。利用强化学习(reinforcement learning),DSO.ai 可以根据设计目标来评估数十亿个替代方案,并快速产生明显优于优秀工程师的设计方案。DSO.ai能够解决的问题/方案的潜力是巨大的:在芯片上排放各种组件的可能方案数量大约有10的9万次方个(1090,000)。相比之下,谷歌AI在2016 年掌握的围棋走法只有10的360次方个(10360 )。既然利用强化学习的AI下棋可以比世界冠军更好,如果愿意花计算时间去做,AI应该可以设计出比天才工程师更好的芯片来。DSO.ai的试验结果令人印象深刻,实现了18% 的工作频率提高,而且功耗降低了 21%,同时将工程时间从六个月缩短到一个月。

最近谷歌和英伟达也发布了类似的结果。另一家EDA开发厂商Cadence也发布了Cerebrus智能芯片探索器工具,这是一个类似于新思DSO.ai 的AI优化设计平台。在探讨这些最新AI设计趋势之前,让我们先看一下半导体设计空间的变化。

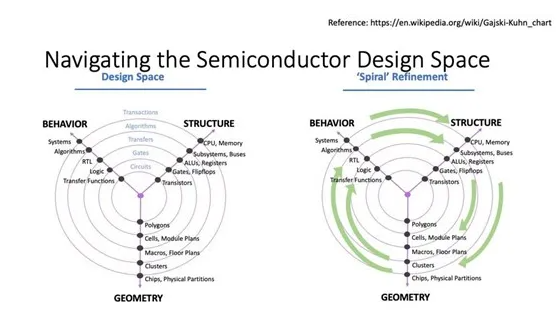

Gajski-Kuhn图是一个很好的起点,它描绘了芯片设计沿三个轴进行的所有步骤:

第一个轴是行为级别(Behavioral),在此轴上架构师定义芯片要做什么,具体包括转移功能、逻辑、RTL、算法和系统。

第二个轴是结构级别(Structural),在此轴上架构师确定芯片如何进行组织安排,包括晶体管、门阵列和反转触发器、ALU和寄存器、子系统和总线、CP和存储器。

第三个轴是几何级别(Geometry),在此轴上工程师定义芯片如何布局,包括多边形、单元和模块规划、宏和平面规划、集群、芯片和物理分割。

所有芯片设计团队都围绕这三个轴上的规范和步骤工作,每一步都是向着中心目标(即交付给晶圆代工厂进行流片),按顺时针方向推进下一阶段的工作。迄今为止,AI的所有应用都是在几何空间或物理设计轴上,以解决摩尔定律的延缓问题。

新思的DSO.ai是第一个将AI应用到物理设计过程的尝试者,它生成的平面规划图功耗更低,运行频率更高,并且占用的空间比经验丰富的设计所能规划的最佳空间还要小。AI对生产力的深远影响值得关注,DSO.ai用户能够在几天内实现过去需要专家团队花费数周才能完成的工作。

谷歌和英伟达的研究团队都发表了利用强化学习进行物理设计的研究论文。谷歌利用AI对其下一代 TPU芯片设计进行平面布局规划,而且正在研究AI在架构优化方面的作用。英伟达同样专注于容易实现的成果:布局规划。他们将会利用其内部拥有的所有GPU计算能力,并使用人工智能来设计更好的AI芯片。

Cerebrus智能芯片探索器

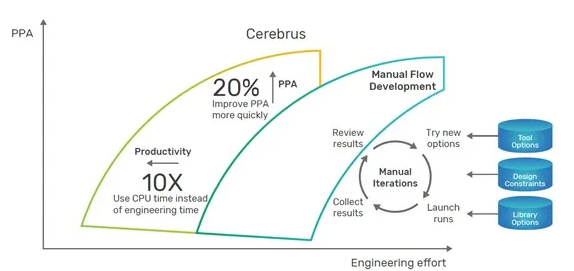

Cadence 最近推出了名为 Cerebrus 的“智能芯片探索器”,通过强化学习来优化物理设计流程。Cerebrus在功能上与新思的DSO.ai 类似,专注于物理设计。虽然谷歌和英伟达可能有足够的资源和知识来开发自己的 AI 以进行芯片设计优化,但他们可能只是为自己所用,而大多数芯片设计公司和项目仍会选择来自EDA 供应商的工具。Cadence Cerebrus的发布似乎进一步验证了强化学习技术作为芯片设计方法论的下一个重大转变。我们相信,随着设计师越来越习惯让机器决定布局,以及竞争压力的增加,AI将逐渐渗透到IC设计流程的各个部分。

图片提高生产力一直是芯片设计历史演进中的主旋律。在芯片设计的初级阶段,每个晶体管都要单独创建,并在完全自定义的布局编辑器中手动连接,这是一个非常耗时的过程。为了提高效率,数字芯片设计开始采用标准单元和原理图网表方法,这使得工程师实现数字逻辑

设计的速度更快,但手动创建原理图网表需要花费大量精力。当桌面Unix工作站出现后,每个工程师都开始拥有更大的计算能力,因此RTL综合变得流行起来。芯片设计人员可以使用 VHDL 和 Verilog 等高级语言捕获数字逻辑功能,并轻松合成包括数百万门的网表。然而,生产力的巨大飞跃带来了另一个问题,即如何布局数百万的标准单元? 因此,继RTL 综合之后,自动布局布线系统被开发出来。现在大型网表也可以迅速实施,EDA又一次显着提高了生产力。

Cadence的Cerebrus建立在大规模计算和机器学习架构之上,并充分利用了完整的 Cadence数字全流程解决方案。Cerebrus借助独特的强化机器学习引擎来提供更好的设计 PPA 结果(性能、功耗和面积)。通过使用完全自动化、机器学习驱动的 RTL-to-GDS 全流程优化技术,Cerebrus 可以比手动调整的流程更快地交付这些更好的 PPA 结果,从而极大提高工程设计团队的生产力。

Cerebrus 使用可扩展分布式计算技术资源,无论是本地还是云端,都可以加速复杂SoC设计的流程。

结语

无论是AI芯片设计企业(NVIDIA 和 Google),还是EDA工具开发商(新思科技和Cadence),都在尝试以AI为主导的芯片设计优化,以改善性能、成本和能耗。毫无疑问,NVIDIA 和谷歌正在集中精力设计开发更好的GPU和Cloud TPU,以提高他们各自的市场竞争优势。但是,AI 优化只是他们用来帮助改进自己产品和服务的工具。

全球EDA的领导者已经开启AI设计的新纪元,新思的DSO.ai和Cadence的Cerebrus平台将率先在物理设计中发挥超越人类工程师的AI优势,加速当今最复杂芯片的设计流程。

在即将于10月12号举行的Cadence Live中国区线上用户大会上,Cadence公司CEO陈立武、Cadence总裁Anirudh Devgan 博士、芯原公司董事长/总裁兼CEO戴伟民博士将为观众带来复杂芯片设计和最新EDA技术趋势的主题演讲,感兴趣的朋友请即报名参会。