芯片商的困境:如何将PCB和IC技术完美融合

2021-10-27

来源:半导体行业观察

表面贴装技术 (SMT) 的发展远远超出了其作为将封装芯片组装到没有通孔的印刷电路板上的方式。它现在正在内部封装,这些封装本身将安装在 PCB 上。

但是用于高级封装的 SMT 与我们已经习惯的 SMT 不同。

Synopsys产品营销总监 Kenneth Larsen 表示:“许多系统包含多个ASIC、大量内存,并且这些都集成在一个非常小的空间内。”这几乎就像你把整个 PCB 压缩成一个非常小的外形。“

高级封装使用中介层或其他基板来安装芯片。这些中介层就像迷你 PCB,虽然由不同的材料制成。但是,金属化再分布层 (RDL) 的尺寸通常比 PCB 上使用的尺寸大得多,即使按照半导体标准它们很大。因此,必须同时从 PCB 端和半导体端提出想法,以确保良好的可制造性。

”有些公司更以 PCB 为中心,从封装 PCB 方面着手,但也有其他更以芯片为中心的公司,他们从芯片方面来看,“产品营销总监 Marc Swinnen 说。Ansys 的半导体。”然而,这两个世界正在拉近,很多公司并没有为此做好准备。“

这导致芯片制造商陷入困境。”你打算使用半导体晶圆厂的现代工具吗?“ 泰瑞达设备接口总经理 Steve Ledford 问道。”或者您打算使用 PCB 和 SMT 制造人员的现代工具吗?“

虽然先进封装并不新鲜,但它仍处于生产周期的早期,应用往往有限。随着成本的下降和更多的应用程序使用这种封装提供的更紧密的集成,更多的公司将能够利用它。因此,退回到较高级别并在原始 SMT 和较新的变体之间获得一些观点可能会有所帮助。

CyberOptics总裁兼首席执行官 Subodh Kulkarni 表示:”在堆叠现象和 SMT 之间,先进封装介于传统前端和传统后端之间。“这就是现在所有创新发生的地方。打开任何现代设备,串在一起的高级封装与 10 年前的电路板看起来大不相同。”

封装内插器的作用与 PCB 相同,可促进安装在其上的组件之间的连接。此外,它们提供最终将连接到凸块和 PCB 的布线。PCB 制造所需的许多概念都在中介层上发挥作用,但只是微型的。包括计算、内存,甚至模拟 I/O 在内的整个系统都可以组装起来,然后作为一个封装安装在 PCB 上。

虽然这听起来像是将 PCB 按比例缩小以安装到元 PCB 上,但这并不是那么容易。任何此类组装过程都需要检查和测试以确保质量,但用于检查和测试 PCB 的工具不一定适用于封装级别。都是SMT,但是根据使用的材料和中介层特征的尺寸不同,需要不同的设备。

用于基板的材料

大批量商用 PCB 通常由 FR-4 制成,FR-4 是一种玻璃纤维/环氧树脂组合,几十年来一直是 PCB 的最爱。虽然它可以缩小用于小型夹层卡和其他小型电路板,但最小线间距以密耳为单位,而不是微米。最小间距通常在 5 或 6 密耳范围内(对于特殊应用会稍微低一些),这意味着超过 100 微米。

图1:由 FR-4 制成的典型 PCB。资料来源:Raimond Spekking / CC BY-SA 4.0(通过维基共享资源)

转换为微米很有用,因为高级封装基板可以支持以微米为单位的尺寸。所以马上就会有一个数量级的立即收缩。它们在微米领域的确切位置也取决于基板材料。

在描述封装内看起来像“迷你 PCB”的东西时,似乎使用了两个词。有时它们被简单地称为基板,而有时它们被称为中介层。似乎没有正式的定义将基板与中介层区分开来,但在此上下文中的常见用法似乎是将基板应用于有机材料,将中介层应用于无机材料。(从技术上讲,中介层是基板。)

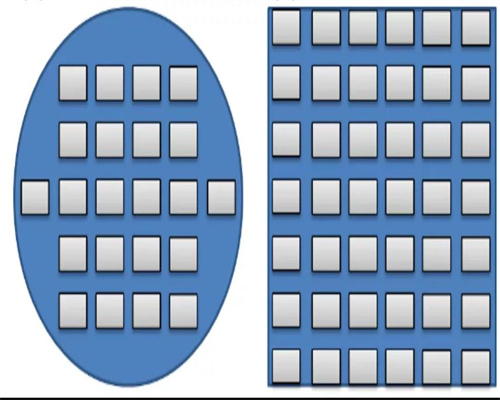

PCB 可能有很多层用于复杂的布线和屏蔽,但基板和中介层往往只有很少的层 - 可能只有一层,通常称为再分布层 (RDL)。有机基板通常用于所谓的面板应用中。这些类似于半导体,因为多个单元在被切割成单个单元之前被制造在一个大块上。最大的区别在于,由于它们的制造方式,面板可以是矩形的,这意味着在切割它们时不会浪费任何东西。该技术主要来源于显示行业。

“为什么方形芯片在圆形晶圆上工作并不是因为晶圆是适合方形物体的理想选择,”Ledford 说。“这是因为这就是拉硅锭的方式。” 因此,矩形中介层最终会从圆形晶圆中分离出来,这意味着边缘会产生浪费。

图 2:晶圆强制将矩形拟合到圆形上,导致一些浪费。面板以矩形开始,以牺牲尺寸为代价更好地利用空间。资料来源:日月光

玻璃是另一个处于开发早期阶段的有前途的候选者。“玻璃既可以是圆形的,也可以是方形的,”莱德福德指出。玻璃基板也常被称为中介层。

这就是 SMT 基板的三种基本变体:PCB、面板和中介层。它们具有显着的成本和尺寸差异。

尺寸和制造

“一切都趋向于类似半导体的尺寸,”Ledford 说。“这只是时间问题。刚毕业的时候,主流的半导体都是1微米线宽。如果你看看现在先进的封装在哪里,它已经非常接近 1 微米的线和空间。它只用了 30 年就达到了这一点。”

任何这些材料所需的尺寸都有两个关键方面。首先,有最小间距。但同样重要的是对这些维度的控制。

“测试和测量都是大约 50 Ω 受控阻抗,”Ledford 说。“这意味着该生产线的制造商需要控制四分之一微米的尺寸。好吧,如果我去我的任何一家 PCB 商店交谈,他们都没有接近这种水平的尺寸控制。”

主要原因是化学:PCB 是使用湿化学制成的,这限制了尺寸和公差。“占主导地位的 PCB 和 [传统] SMT 的湿化学工艺没有您需要的尺寸控制,”Ledford 说。“什么样的工艺可以让你控制四分之一微米的线和空间?干法工艺——溅射、干法蚀刻等等,主要来自半导体领域。”

虽然可以在某种浴槽中同时处理多个 PCB,但面板和晶片必须在它们的反应室中单独处理。这是与较小外形尺寸相关的主要成本之一。

Onto Innovation产品营销经理 Woo Young Han 表示:“半导体制造商转向面板级封装的主要原因是系统级封装 (SiP) 中的大芯片。”包括 CPU、GPU、DSP 和内存在内的多个芯片被封装到一个单一的底座中,其结果比半导体行业中使用的传统芯片尺寸大得多。SiP 芯片尺寸可以大到 100 毫米,因此在制造大型 SiP 芯片时,600 毫米矩形面板比 300 毫米圆形晶圆更好。“

硅中介层受晶圆尺寸的限制,因此它们对于集成具有更有限内存的处理器更有用。小芯片也是集成到这些较小封装中的候选者。

使用面板可以提供更大的芯片,但代价是您可以将线路或芯片放在一起的距离。”面板级封装可能有更大的 GPU 或 CPU,但不一定与小芯片非常接近,“布鲁克白光干涉仪产品线经理 Robert Cid 说。

也就是说,虽然人们可能希望面板成为晶圆级集成的中间地带,但实际上可能会走另一条路。”对于那些想要进行更多集成的公司,我认为面板级封装越来越成为一种可行的解决方案,“Cid 指出。”如果晶圆级封装开始转向更大的基板,则可能进一步降低封装成本。“

PCB 与任何这些其他选项之间的主要功能区别在于可以管理的互连数量。”你不是在谈论几个 40 微米的 I/O 焊盘,“Ledford 说。”你说的是数千个 40-?m I/O 焊盘。“

其他人同意。Synopsys 数字设计部门的硅生命周期管理营销总监 Randy Fish 指出:”你可以有数千个这样的微凸点和非常密集的痕迹,“。”并且能够拥有冗余互连是其中必不可少的一部分。“

检查生产线

PCB 和先进封装之间的主要工艺差异之一在于检查——尤其是在发现缺陷的地方进行返工的能力。

”在典型的 PCB 检测流程中,检测模块对 PCB 进行检测,然后将 PCB 转移到审查站进行操作员审查——然后将其送到维修站修复发现的缺陷,“韩解释说。”在半导体晶圆检测领域,修复单个缺陷在前端和后端半导体工艺中都是不可想象的。“

人类仍然存在于 PCB 检测领域。Ledford 说:”由于 PCB 行业的历史性质,他们仍然看到许多操作员通过显微镜观察的手动检查站。“

CyberOptics 的 Kulkarni 描述了他看到 DIMM 生产线末端时的惊讶。”有 20 人站在那个区域周围,旁边有白灯,“他说。”他们实际上是从传送带上捡起每块内存板,并在将它们放入塑料袋之前目视检查两侧。“

DIMM 进行了最终的 I/O 测试,但插入时是热的。半分钟后,取出时,它们已经明显冷却了,而且它们也没有那么容易拉出来——有时会扰乱板上的记忆。”尽管 I/O 检查看起来不错,但当客户拿到它时,情况并不好,“Kulkarni 解释说。

添加自动最终检查步骤现在允许干预任何需要返工的电路板,而无需人工检查。

用于容纳大型 CPU 或其他此类昂贵芯片的插槽是另一个例子。使用插槽是为了在电路板出现问题时,可以轻松移除高价值芯片并将其移至新电路板,而不是随电路板一起丢弃。

”在一个 3 × 3 英寸的正方形中,你有 10,000 个引脚,“Kulkarni 说。”而这些实际上是毛茸茸的小铜质东西,它们会出来并弯曲,因为必须有某种弹簧。“

这使得人类很难检查它们。可视化工具可以再次使该过程自动化,从而提高结果和吞吐量。因此,PCB 检测已经朝着更高水平的自动化方向发展。

但是在高级封装内移动,信号的尺寸和数量使得手动检查完全不切实际。需要自动化。然而,这些工具的工作方式在 PCB 与面板级和晶圆级组件之间有所不同。

”大芯片尺寸在 PCB 世界中很常见,传统的 PCB 检测工具使用基于 CAD 设计规则的方法,“Han 说。”在半导体领域,检测工具旨在发现高度重复的芯片图案上的小得多的缺陷,因此半导体领域的检测工具使用黄金裸片或相邻裸片比较方法。啜与半导体晶圆相比,裸片之间的裸片差异要大得多,而且 CAD 设计规则方法比黄金/相邻裸片比较方法效果更好。这是传统 PCB 检测工具的优势。与传统 PCB 裸片设计相比,SiP 裸片的设计规则也小得多——小至 2 微米的走线宽度——并且需要亚微米缺陷检测。然而,PCB 使用大于 10 ?m 的走线宽度,而传统的 PCB 检测工具不具备执行亚微米缺陷检测的光学分辨率。这是半导体晶圆检测工具的一个优势。“

面板尺寸比内插器尺寸稍大,但仍有可能使用半导体设备——数字放宽。”如果您的尺寸为 600 x 600 毫米,您需要确保整个面板的特征都在规格范围内,“Cid 说。”这可能是一个挑战。我们已经看到客户寻求加快计量的方法来调查更大的区域,以便在该面板投入生产之前评估该面板的质量。“

尽管如此,假设面板和中介层有类似的检查是错误的。”我们看到晶圆级和面板级封装的要求非常不同,“Cid 说。”我们有专门为面板级封装设计的工具,与我们为晶圆级封装设计的工具有不同的要求。“

也就是说,这部分是面板滞后于中介层的情况。”我们听到的路线图讨论表明,面板级处理要求将变得更加复杂,需要几年后您对晶圆级封装的一些严格计量,“Cid 说。

因此,虽然自动化和 AI 正在进入 PCB 检测领域,但这些技术对于高级封装至关重要。

测试板、基板和中介层

测试汇集了完全不同的理念。传统上,PCB 是使用钉床测试仪进行测试的,这些测试仪可以快速验证板上的所有连接。但是每块板都需要一个定制的夹具,这给测试开发过程增加了摩擦。

JTAG 使这变得更容易一些,提供了一种将电路板上的所有组件链接在一起并测试它们的连接性的方法。这是JTAG最初的目标,后来才扩展了内部芯片测试能力。因此原则上,可以使用单个 JTAG 端口测试连接和功能。

相比之下,IC 使用内部自测以及外部提供的向量,这些向量可能使用专用测试引脚或在测试模式下兼作测试访问引脚的其他引脚。与 PCB 测试的一个关键区别在于,使用 IC 来测试功能。对于 PCB,主要是测试连接。假设 PCB 上的 IC 可以根据它们作为制造流程的一部分进行的个别测试工作。

高级封装介于两者之间,而确切的测试时间将对成本产生巨大影响。那是因为人们正在使用经过测试然后分离的裸片,将它们放置在基板或中介层上,而基板或中介层本身必须经过测试以确保连接正常工作。

但是这些芯片在分离过程中是否被损坏了?基板/中介层组件是否需要单独测试,包括连接性和功能性,以确保一切都在组装过程中幸存下来?是否应该在应用芯片之前测试中介层,然后再测试?如果要测试整个事情,应该在封装之前还是之后进行测试——还是两者兼而有之?

部分挑战是从未连接到外部连接的内部连接数量。”很多这些内部模具并不是用来与现实世界对话的,“Fish 指出。”所有的连接都是死对死的。“

这些问题没有可靠的答案。它会因应用程序和伴随的经济情况而异——更不用说失败的风险了。与那些故障后果仅限于制造商的烦恼或商誉损失的组件相比,安全关键组件需要更多的测试。

”如果有这样的选择,在某些情况下,人们确实希望能够测试复杂封装内的芯片,“Fish 说。”但对于低价或中等价位的产品,我认为您无法再次测试每个芯片。“

如果对模具本身进行测试,也会产生重要的实际影响。”如果您购买已知良好的模具,供应商是否会给您他们的测试序列,以便您可以自己运行?“ 鱼问。

至于实际测试,即使组件看起来像迷你 PCB,由于尺寸的原因,钉床方法是完全不切实际的。此类固定装置中使用的弹簧针太大了。此外,每个芯片的定制夹具给工艺增加了不合理的负担和成本。

JTAG 也可以在这里使用,尽管它的信号速度有限。USB 和 PCIe 也是用于专用测试访问端口的选项,可以加快单个芯片和高级封装组件的测试。事实上,它也可以用于 PCB。

”我们正朝着高速专用 I/O 进行测试,“Fish 说。”您将我们的 IP 插入到您的芯片中,该芯片连接到控制器端的那些 I/O,然后连接到芯片上的测试基础设施。“

结论

总而言之,必须使用主要来自半导体领域的技术来制造、检查和测试高级封装内的表面贴装器件。虽然许多想法可能起源于 PCB,但将 PCB 方法缩小到足够低通常是不切实际的。

由于封装是半导体制造过程的自然组成部分,因此先进封装承载了大部分半导体遗产也就不足为奇了。但是,将元件连接到基板表面的基本原理可以追溯到 PCB 世界。当缩小到接近半导体的尺寸时,它看起来非常不同。