承认吧,摩尔定律已死

2021-11-02

来源:半导体行业观察

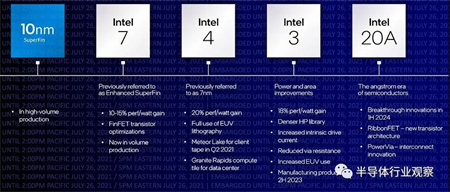

英特尔在 7 月下旬的英特尔加速活动期间宣布其面向未来的半导体工艺节点的新名称时受到了很多抨击。按照英特尔的说法,他们的新节点称为 Intel 7、4、3 和 20A。但业内权威人士抨击该公司将 10 纳米增强型 SuperFin 工艺节点命名为“Intel 7”的做法(英特尔上周在其英特尔创新开发者大会上宣布并展示了使用Intel 7 工艺节点构建的第 12 代 i5、i7 和 i9 酷睿处理器,因此该工艺技术显然掌握得很好)。该公司现在把“Intel 4” 用于之前称为 7nm 的节点。Intel 3 和 Intel 20A 是全新的节点名称。

在笔者看来此次节点重命名一部分源于营销,另一部分只是面对现实。

英特尔已重新命名其即将推出的工艺节点,以符合行业惯例而不是其自身对现实的看法

过去,英特尔曾表示其 10nm 增强型 SuperFin 节点(现更名为Intel 7)在功率和性能上与台积电的 7nm 节点大致相当。这很令人困惑,不是吗?该公司还表示,行业分析师已要求英特尔更新其工艺节点命名法,以反映该公司在半导体工艺领域的真实竞争地位。所有这些都是重命名节点的营销部分。

而现实是这样的:纳米命名法在很长很长一段时间内都不准确。不适用于英特尔,当然也不适用于任何其他硅代工厂。这种情况就像热门喜剧电视节目“这到底是谁的台词?”中的评分系统,分数不重要。

多年前,工艺节点命名是基于晶体管的最小特征尺寸。该命名约定是专门为平面 MOS 晶体管开发的,最小晶体管特征总是晶体管的栅极长度。当 FinFET 取代平面 MOS 晶体管时,这种命名约定就消失了,所有供应商的工艺节点名称都变成了您从等效平面 MOS 晶体管获得的功率和速度的估计等效值。除了他们实际上无法再制造那些平面 MOS 晶体管。平面晶体管技术放弃了。MOS 晶体管在目前的光刻水平上不能很好地工作。这就是我们转向 FinFET 的原因。早在 2011 年,英特尔就在 22 纳米节点上推出了其首个 FinFET 工艺。

RibbonFET 和埃

十年后,晶体管的基本结构即将再次发生变化。

FinFET 栅极从三个侧面驱动。这比平面 MOS 晶体管中驱动的多了两个侧面,它以更复杂的制造技术为代价带来更好的晶体管性能。然而,驱动 FinFET 晶体管栅极的三个侧面不再达到所需的速度和漏电流。我们现在必须驱动栅极的所有四个侧面。这些 4 边栅极驱动结构通常称为“Gate all around”或 GAA。

英特尔称其 GAA 晶体管为“RibbonFET”,目前他们计划在Intel 20A 工艺中推出改技术,该工艺将于 2024 年上半年出现(除非出现延迟)。注意进程名称中的“A”。“A”代表“埃”。英特尔没有像以前的工艺节点那样称这个工艺节点为“intel 2”,而是将单位从纳米切换到埃。一埃是 10 -10 m,或十分之一纳米。我认为我们应该简单地忽略英特尔从更大的工艺节点中删除了“nm”这一事实。

据推测,这种对埃的命名更改允许分数纳米节点命名。这与我们之前使用的单位微米的情况类似。回到黑暗时代,我们有 3、2.5、2、1.5、1.3、1.2 和 1 微米的工艺步骤,然后是 0.8、0.75、0.7、0.5,一直到 0.25 微米左右。在那个点附近的某个地方,我们从微米跳到了纳米。根据我的记忆,命名法的变化发生在 0.18 微米处,通常称为 180 纳米。那是什么时候?大约 1998 年,这发生在二十多年前。

这意味着在纳米工艺节点尺将被使用近四分之一个世纪以后,埃时代正式到来。Intel Angstrom 命名法允许公司拥有名为 Intel 18A、Intel 17A、Intel 16A 等的工艺节点。这听起来比 Intel 1.8、Intel 1.7、Intel 1.6 等等好多了,不是吗?看起来他们也能通过这种方式取得了更大的进步,对吗?

然而,我们必须承认,从一个节点到下一个节点的进度不像以前那么大了。从上图中,您可以看到从一个英特尔工艺节点到下一个节点的性能/瓦特提高了 10% 到 20%,并且该图像甚至没有讨论密度改进。

摩尔定律在坟墓中腐烂了

基于以上所有内容,我有一个非常悲伤的消息要告诉你,摩尔定律已经死了。即使英特尔首席执行官帕特·盖辛格 (Pat Gelsinger) 上周在英特尔创新活动期间做出了在未来 10 年内每年都满足或击败摩尔定律的大胆而热情的承诺。然而通过从一代到下一代削减几埃来扩展工艺节点并不能实现晶体管密度的两倍,而这正是摩尔定律的真正本质。

从我的角度来看,围绕摩尔定律存在很多困惑。

首先,摩尔定律长期以来一直与 Dennard Scaling 紧密交织和混淆,Dennard Scaling 表示平面 MOSFET 的速度和功率随着晶体管密度的增加而按比例降低。在半导体的早期,当一种新的工艺技术将晶体管面积缩小 50% 时,晶体管的速度会增加一倍,而功率则会减半。每隔几年,我们就获得了一半大小的晶体管,其速度是每个新工艺节点的一半,而运行速度则是一半。那时确实是非常好的时代,摩尔定律正在全面发挥作用。然而,Dennard Scaling 是一个专门针对平面 MOS 晶体管的观察结果,我们已经有十年没有使用最先进的新工艺节点制造这种晶体管了。

摩尔定律不涉及晶体管功率或速度。摩尔定律说,芯片上的晶体管数量大约每两年翻一番。这就是它所说的。喜欢的可以查一下。Gordon Moore 于 1965 年 4 月 19 日在《电子》杂志上发表的原始文章,文章标题是“将更多元件塞进集成电路上”。它方便地发布在英特尔的网站上供您阅读。这篇文章发表于摩尔和鲍勃诺伊斯创立英特尔的三年前,当时摩尔和诺伊斯都还在飞兆半导体工作。

摩尔在他开创性的文章中进行了令人难以置信的预测壮举。半导体行业最终接受了他的预测并将其转化为基于极少数数据点的自我实现预言。第一个数据点是单个晶体管。第二个数据点是最早的商用集成电路之一,称为 Fairchild μLogic Type G RTL 芯片的 3 输入 NOR 门。

根据大卫帕特森博士的说法,摩尔定律一直持续到 2015 年,因为它耗尽了气力。帕特森怎么会说摩尔定律在 2015 年消亡,而英特尔的高管们一致让您相信摩尔定律在今天仍然存在并且很好?这是因为摩尔 1965 年论文第 2 页上的一句话。那句话是:“……在单个半导体衬底上生产越来越大的电路功能。” (重点是我的。)摩尔定律是关于单片集成电路的,而这不是半导体行业现在的发展方向。

事实上,在2003年举办的第50届国际固态电路会议上,在一个题为“No Exponential is Forever”的议题中,戈登·摩尔本人断然指出:“没有任何的物理事物可以持续成倍改变。” 摩尔定律在将近 20 年前就已经消亡,而摩尔亲眼目睹了这一点。

目前标志着摩尔定律终结的典型代表是英特尔自己的 Ponte Vecchio GPU。英特尔正在使用 47 个有源“tiles”(英特尔对多芯片封装中的小芯片或芯片的名称)组装这种集成设备,由来自五个不同半导体工艺节点的多家半导体供应商制造,所有这些都使用 2.5D 和 3D 组装组合在一个封装中技术来生产具有超过 1000 亿个晶体管的集成产品。

有人声称摩尔在他的文章中预见到了多芯片封装。他们引用了这句话:

“事实证明,用较小的功能构建大型系统可能更经济……”

但他们似乎省略了这句话的后半部分:

“……它们是分开封装和互连的。”

在这里,摩尔清楚地讨论了在一块板上使用多个单独封装的芯片,这是自 1960 年代集成电路首次出现以来板级设计的主要内容。

在我看来,摩尔显然不是在用这句话来预测今天的多芯片封装。事实上,他的文章讨论了在 10 年内(即 1975 年)出现每个 IC 具有 65,000 个元件的单片 IC 的可能性,这比 1965 年摩尔的文章出现时任何单个印刷电路板所能容纳的分立元件都要多。

谁可能需要超过 65,000 个组件?如果摩尔当时考虑过,而且他可能确实考虑过,那么他一定已经看到,直到很远很远的将来才会需要多芯片封装技术。嗯,那个未来已经到来。

英特尔的 Ponte Vecchio GPU 整合了来自五个不同工艺节点的 47 个tiles,将 1000 亿个晶体管塞进一个封装中。(图片来源:英特尔)

多芯片封装之所以有意义,只是因为不同的工艺节点提供不同的成本/性能/能力权衡,因为我们处于当前芯片制造设备的光罩极限,并且因为 2.5D 和 3D 封装技术现在足够实用和经济这种方法在商业上有效。假设您拥有可靠且经济地组装所有这些tile或小芯片所需的制造工艺,为什么不应该使用最高效的半导体工艺节点制造模块和子系统?Ponte Vecchio无疑是一个工程奇迹,但它绝对不是单片芯片,因此它不是原始摩尔定律实际应用的例子。

除了摩尔定律的大量神话基础之外,对于我们大多数人来说,英特尔如何将 1000 亿个晶体管塞进 Ponte Vecchio 封装实际上并不重要。对于在设计中使用 Ponte Vecchio GPU 的系统工程师来说,这并不重要。对于使用在 Ponte Vecchio GPU 上运行的图形软件或计算机游戏的人来说,这并不重要。设备的性能、功率和价格(所有工程设计的三个基本“P”)对于我们这些不熟悉封装的人来说非常重要。

英特尔计划以类似的方式构建公司下一代至强处理器的代号 Sapphire Rapids。英特尔将使用基于公司 EMIB(嵌入式多芯片互连桥接)技术的 4 个 CPU 块和 2.5D 组件制造 Sapphire Rapids。Sapphire Rapids 处理器的多个版本还将在同一封装中集成多个 HBM2(高带宽内存 2)DRAM 堆栈。

英特尔的 Sapphire Rapids 是下一代至强 CPU,将包含由四个 EMIB 桥连接的四个 CPU 块。(图片来源:英特尔)

多芯片封装并非英特尔独有。AMD、Nvidia 和 Xilinx 都生产集成芯片,这些芯片在外部看起来像单片集成电路,但在内部是多芯片设备——相互连接的tile或小芯片的集合。

例如,赛灵思在 2011 年推出了 Virtex-7 2000T FPGA。它基于多芯片封装,将四个 FPGA 管芯放在一个硅中介层之上。台积电为赛灵思制造该器件。大约在同一时间,多芯片封装使赛灵思能够在其 Virtex-7 580T FPGA 中集成 28 Gbps 收发器,然后才能将这些收发器直接构建到 CMOS FPGA 芯片中。赛灵思在每一代新 FPGA 中都扩大了多芯片封装的使用范围。这很好地表明多芯片封装运作良好,至少对于 IC 市场的高端而言是这样。

总而言之,欢迎来到埃时代。这是一个“超越摩尔”的时代。现在摆脱了将所有东西都放在一个芯片上的情感和经济需求,这个半导体制造的新时代已经生产出比以往任何时候都更大、更好的集成设备。仅仅依靠单片 IC 和摩尔定律是无法提供这些好处的。

摩尔定律可能已死,但摩尔定律的精神永存。