嵌入式微控制器MC68HC912B32背景调试模式设计及实现

2008-04-28

作者:徐 清,王宜怀

摘 要: 介绍了以MC68HC908JB8为主控芯片的Freescale 16位MCU MC68HC912B32的BDM调试模式,给出了BDM通信协议及编程原理、硬件电路图。

关键词: BDM MC68HC912B32 BKGD

随着Flash技术在微处理器上的广泛应用,使单片机在开发和应用手段上有了革命性的变化,从传统的仿真器(ICE)到目前流行的JTAG,设计人员在不断寻找一种移植性更高、更易操作、费用更低的开发手段。使用传统的仿真器进行嵌入式开发时,通常调试工具会受价格和烦琐的操作所限制,但是随着微处理器制造工艺的提高及Flash技术的发展,一些高端微处理器(如CPU12/16/32、PowerPC、ColdFire等)内部已经包含了用于调试的微代码,并可以通过背景调试模式BDM(Background Debug Mode)进行调试。由于这种方法省去了仿真器,因此避免了高频操作、交直流电不匹配等问题。随着BDM标准的不断规范和普及,用BDM调试模式进行嵌入式开发已经成为一种首选。

MC68HC912B32(以下简称B32)是由Freescale公司推出的一款基于CPU12核心的16位嵌入式MCU。它具有体积小、功耗小、功能多等优点,主要用于汽车电子、工业控制、医疗设备等领域。它是Freescale公司较早提供的一款背景调试模式的16位MCU。背景调试模式是Freescale公司自定义的片上调试规范。

1 背景调试模式介绍

BDM是由Freescale半导体公司推出的一种单线(Single Wire)调试方式,是目前单片机普遍采用的调试方式之一。其他公司的嵌入式处理器也有类似的调试方式,如AMD公司的X86μP系列微处理器提供的AMDebug调试方式等。

BDM调试方式为开发人员提供了底层的调试手段,开发人员可以通过它初次向目标板下载程序,同时也可以通过BDM调试器" title="调试器">调试器对目标板MCU的Flash进行写入、擦除等操作。用户也可以通过它进行应用程序的下载和在线更新、在线动态调试和编程、读取CPU各个寄存器的内容、单片机内部资源的配置与修复、程序的加密处理等操作。而这些仅需要向CPU发送几个简单的指令就可以实现,从而使调试软件的编写变得非常简单,通常自己就可以编写。BDM硬件调试插头的设计也非常简单,关键是要满足通信时序关系和电平转换要求。

目前常用的标准BDM调试插头如图1所示,各个引脚信号的定义如表1所示。

2 BDM调试原理

2.1 总体概述

以CPU12为内核的MCU的运行模式有单片方式(Single chip)和扩展方式(Expanded Mode)两种。运行模式主要由BKGD、MODB和MODA引脚的状态决定,各个模式与引脚状态间的关系见表2。单片模式又分普通单片模式(Normal Single Chip)和特殊单片模式(Special Single Chip)两种,而只有在特殊模式下BDM才能被激活,因此特殊单片模式又称BDM模式。图2为PC机通过BDM插头与目标机相连。

2.2 BDM指令介绍

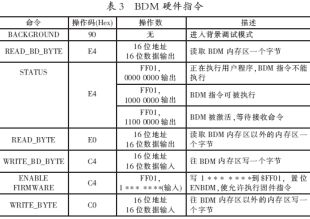

BDM有两类指令。一类是在一般运行模式下可以直接执行的,被称为硬件指令(Hardware Command);另一类则是只能在BDM模式下执行的程序,这些程序在进入BDM模式后被固化在地址为$FF00~$FFFF的ROM中,被称为固件" title="固件">固件指令(Firmware Command)。

因为BDM控制模块不在CPU中,所以BDM硬件指令可以在CPU正常运行时被并行执行,其他BDM指令是基于固件的,必须在CPU处于BDM模式下才能执行。硬件指令允许读写目标系统内(包括片内RAM、EEPROM、I/O和控制寄存器等)的所有内存。硬件指令可以不在BDM模式下执行,表3列出了BDM模块常用的硬件指令。

固件指令必须在HC12单片机的BDM ROM中执行,且CPU必须在BDM模式下才能执行,通常使用硬件指令BACKGROUND使CPU进入BDM模式。当BDM被激活时,BDM ROM就被分配到地址空间:$FF20~$FFFF,同时7个BDM寄存器被分配到地址空间:$FF00~$FF06,此时CPU就可以通过执行ROM中的代码完成相应的固件指令操作。表4列出了BDM的7个寄存器,表5介绍了常用的3个固件指令。

2.3 进入BDM模式

下面介绍使目标机进入BDM模式的两种常用方法。

方法1:将目标机的BKGD引脚拉低,然后给目标机的RESET引脚加低电平,即给目标机复位,复位脉冲要足够宽,至少要大于目标机的512个时钟周期" title="时钟周期">时钟周期。本文采用Freescale公司的8位微处理器MC68HC908JB8(简称JB8)制作BDM调试头,用其PTA0和PTA1口控制目标机的RESET和BKGD引脚。此方法通过软件编程的方式进入BDM模式。

方法2:通过硬件跳线的方式将BKGD置低电平,在目标机复位后再将BKGD置高电平" title="高电平">高电平,以进入目标机的BDM模式。进入BDM模式后,带有BDM程序的片内专用ROM将Flash的$FF00~$FFFF替换。此空间在普通单片方式下存放中断向量。该方法仅通过硬件跳线的方式进入BDM模式。

3 B32的BDM调试系统设计

3.1 BDM调试器系统硬件设计

该BDM调试器的BKGD和RESET信号分别由JB8单片机的I/O口PTA1、PTA0提供。双方通信引脚使用漏极开路驱动(或称线或)的方式,平时靠上拉电阻维持高电平。Flash编程电源VFP由MAX662提供,MAX662是一款专门提供12V Flash编程电压的芯片。MAX662外围电路原理图如图3,BDM调试插头电路原理图如图4。

3.2 BDM调试器系统软件设计

CPU12的BDM通信协议也称为单线通信协议。下面按照该协议,以JB8作为主控制芯片详细介绍B32的BDM调试系统的软件设计。在程序开始前,需要宏定义一些常量以方便下面程序的调用。具体的宏定义有:

#define DisableInt() asm(″sei″) /*关闭中断*/

#define EnableInt() asm(″cli″) /*开放中断*/

#define PTA *(volatile unsigned char*)0x00

/*A口数据寄存器*/

#define DDRA *(volatile unsigned char*)0x04

/*A口方向寄存器*/

3.2.1 调用读写汇编子程序

通过调用读写汇编子程序" title="子程序">子程序,可以读取和发送一个字节,具体函数如下:

INT8U BDMDATA;

void SendOneByte(INT8U c)

{

DisableInt();//关中断

BDMDATA=c;//赋值需要发送的值

_WRITEBYTE();//调用写字节汇编子程序

EnableInt();//开中断

}

INT8U RecOneByte()

{

DisableInt();//关中断

_READBYTE();//调用读取字节汇编子程序

EnableInt();//开中断

return BDMDATA;//返回读取的字节

}

调用写子程序的输入参数是需要被写的一个字节;调用读子程序的返回参数是读取到的一个字节。

3.2.2 读写汇编子程序

主机方以下降沿通知目标机方的BKGD端,位通信开始,每一位传输至少需要16个时钟周期。具体过程如下:

主机首先拉低BKGD引脚,并使低电平维持时间不短于512个时钟周期,目标机探测到下降沿信号后清命令寄存器,同时等待接收主机的BDM命令。

主机写位0到目标机BKGD端的操作为:主机拉低目标机的BKGD端不少于12个时钟周期,目标机在探测到低电平以后的第10个周期对BKGD采样,读入该位的0。

主机写位1到目标机BKGD端的操作为:主机拉低目标机的BKGD端2~4个时钟周期后释放BKGD端,使之为高电平,目标机在探测到低电平以后的第10个周期对BKGD采样,读入该位的1。

下面是写一个字节的汇编代码:

__WRITEBYTE∷

LDA #$8

_NEXTBIT:

LSL*_BDMDATA //左移待发送的8位数据

BCC_WRITE0 //判断发送位

BCLR #1,PTA //PTA.1置低电平

NOP

BSET #1,DDRA //PTA.1定义为输出

_NEXTBIT1:

BCLR #1,DDRA //PTA.1定义为输入

NOP

DBNZA _NEXTBIT //判断字节是否发送完毕

_WAIT10:

RTS //返回主程序

_WRITE0: //发送位“0”

BCLR #1,PTA //PTA1置低电平

NOP

BSET #1,DDRA //PTA1定义为输出

NOP //空操作,用于控制时序

NOP

NOP

NOP

NOP

NOP

NOP

BRA_NEXTBIT1 //发送下一位

主机读目标机BKGD端的信息时,主机拉低目标机BKGD端2~4个周期后释放BKGD端,然后定义该引脚为输入状态,读取BKGD端的电平。如果目标机输出为0电平,则继续拉低BKGD端,从探测到主机拉低BKGD端起持续13个时钟周期。所以主机的读操作应在从拉低BKGD线算起的13个时钟周期内完成。对于目标机输出为1的情况,无需目标机输出高电平,因为BKGD端已用电阻上拉,只需定义该引脚为输入,则自然会使之为1。

下面是读取一个字节的汇编代码:

__READBYTE∷

LDA #8

_NEXTBITR:

PSHA //A进栈

LDA #01

BCLR #1,PTA //PTA.1置低电平

BSET #1,DDRA //PTA.1定义为输出

BCLR #1,DDRA //PTA.1定义为输入

NOP

LDA PTA //读取BKGD引脚状态

NOP

NOP

NOP

LSRA //将读取位移入标志位C

LSRA

ROL *BDMDATA //将读取的位存入变量

PULA

DECA

BNE _NEXTBITR //判断字节是否读取完毕

RTS //返回主程序

对于硬件命令,命令之间间隔要大于150个时钟周期;对于固件命令,送出读命令到读取数据之间要延迟32个时钟周期;写命令后面可紧跟需要写的数据,但与下一条命令之间要间隔32个时钟周期。

3.2.3 测试程序

为了测试以上程序的正确性,特用VC6.0编写了一个计算机端的测试程序。该程序通过串口与JB8通信,以完成对B32 Flash的读写和擦除。由于源代码较长,限于篇幅不在此列出。

参考文献

1 Freescale.M68HC12B Family Data sheet.Rev.9,2004

2 Freescale.CPU12 Reference Manual.Rev.3,2002

3 Freescale.A Serial Bootloader for Reprogramming the MC68HC912B32 Flash.E2PROM,1997

4 Freescale.MC68HC90908JB8/D.Rev.1.0,2000