宽带C类功率放大器(PA)在某些通信频带中是有用的。虽然现已被集成进Agilent-EEsof (www.agilent.com)的先进设计系统(ADS)仿真软件中,Touchstone曾一度是用于开发和优化这种功率放大器阻抗匹配网络的强有力工具。随后的是一种展示如何为选定RF晶体管提取优化输入和输出大信号阻抗、用单端口网络建模其行为然后在整个要求频带内开发工作于50欧姆系统阻抗网络的设计方法。为确认该方法的有效性,设计了一个从225到 400 MHz间功率增益是10dB的10W功率放大器。

设计宽带微波PA是一项充满挑战性工作。RF功率器件参数随信号电平及频率的改变而变化,这使得获得优化的阻抗匹配很困难。可使用多种技术以表征功率器件行为。表征得越完整完善,所用的模型通常就越复杂。

大信号充电控制晶体管模型和改进的Ebers-Moll模型是早期使用的为RF功率晶体管建模的模型。在一个近似的PA设计中,还应用了大信号S参数。但因测量这些大信号S参数很困难,该技术用处有限。采用数值分析的计算机模拟也被用于预测C类功率放大器的行为。虽然该方法能得出精确结果,但采用该方法设计C类功率放大器是个冗长而晦涩的过程。幸运地是,在1970年代中期发展起来的谐波均衡设计方法极大简化了非线性电路和大信号功率放大器的设计。该技术的一个基本限制是其复杂性及解决电路问题所需的需用专业数学方法完成的大量数学运算。

源于RF功率晶体管的非线性特征,一个完整的双端口器件模型并非设计输入和输出匹配网络的上佳选择。在本文中,采用的是单端口阻抗模型以表征优化负载及该功率器件的源终止。在RF器件数据手册中,一般在RF功率晶体管工作频段内的几个频点上给出优化负载和大信号源阻抗8。RF器件的有效输入和输出阻抗可被表述为这些优化终止的共轭变化。

可借助负载牵引(load-pull)调谐器通过测量该器件在整个相关频带内的优化负载和源阻抗对RF功率晶体管特性进行表征。如图1所示,它要求一个单端口表述以预测这些阻抗从低频带端(FL)到高频带端(fH)间的复杂共轭变化。在此例中,Zout = Z*OL ,Zin = Z*s;其中,ZOL是优化负载阻抗,Zs是源负载阻抗。图2表示了该建模后的阻抗网络的两种可能拓扑结构。全部损耗集中于一个电阻,该电阻终止了一个电感-电容(LC)两端口网络。

|

|

可利用一个解析综合程式来实现能与在高低频两端测试到的阻抗数据相匹适的单端口网络。但可通过如下方法代替此冗乏枯涩的工作——可利用类似Touchstone(现ADS)等模拟软件以优化建模网络的电路元素以预测相关全频带范围内的性能。

若晶体管在一个宽的频率范围内以共轭方式匹配,则随着频率的增加,可获得的最大增益将以6dB/倍频的负斜率滚降。用于补偿晶体管的功率增益随频率变异的技术之一是有选择地反射功率增益相对较高的频带低端的一些功率。但该技术导致的受控失匹毕竟会削弱低频带输入的电压驻波比(VSWR)。RF晶体管的近似功率增益由下式给出:

|

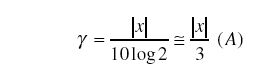

其中:fmax=最大振荡频率;γ=一个与增益变化相关的常数,由下式表示:

|

其中:x =以dB/倍频表示的斜率。由输入反射引起的匹配网络发射损耗由下式给出:

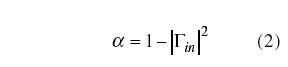

|

其中:Γin=输入端的反射系数。

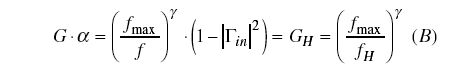

为得到一款在整个相关频带具有常数Gα的产品,

|

其中:GH =高频带侧fH的增益。

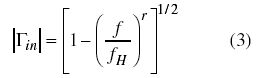

|

利用Touchstone的优化能力,可根据模型方程3设计输入匹配网络。

推荐的宽带C类 PA计算机设计方法可被归纳为如下的系统步骤:

- 为得到所需的输出功率、增益和电源电压,从器件数据手册中在要求的频带内选用大信号输入和输出阻抗(Zin和Z*OL)。

- 利用数值内插和外推技术扩展阻抗数据采样点。当确定器件在频率fL、fo和fH的终端阻抗时,这是一项有用技术。

- 选用合适的单端口网络拓扑在整个频段为上述终端阻抗建模,并用Touchstone优化其要素值。

- 在设计好建模电路后,分别在建模电路和源及50欧姆负载终端间插入输入和输出匹配网络。通过一个大致的图形设计程式,可对匹配网络的元素进行初始估值。

- 对输入和输出匹配网络实施优化以实现期望的输入和输出匹配。输出匹配网络设计成可实现共轭匹配并能在整个频带为晶体管输出提供阻抗ZOL。另一方面,输入匹配网络设计成能在fL 到 fH间得到平坦的增益。通过选择性地在较低频率实施误配,可达到上述结果。将不同采样频率带入方程3可对输入反射系数进行估算并将其存储在外部数据文件中。然后对输入匹配网络进行优化以在整个频带对计算出的输入反射系数进行建模。

- 在保持所要求频率响应的前提下,基于实际情况,用Touchstone的调谐器窗对匹配网络的元素进行调制。