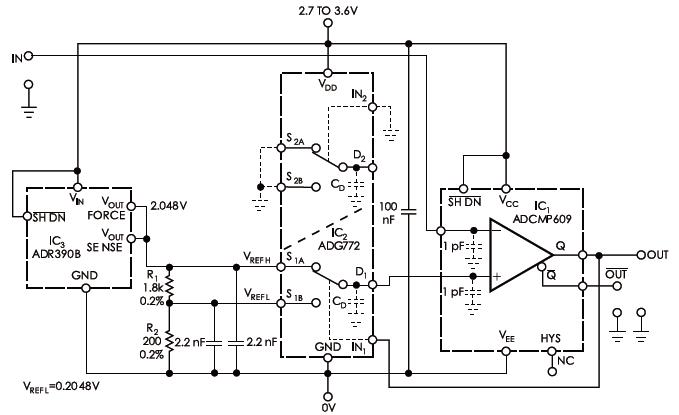

在先进的IC比较器中,可编程滞后量消除了以0V为中心的差分输入电压噪声(参考文献1),并且如果比较器的差分输入电压很低,或者随时间变化的速度很慢,则可以改善它的响应。例如,Analog Devices公司的ADCMP609比较器使你能用一个电阻把它的滞后量设定在0至160 mV之间,该电阻连在HYS(即“滞后量”)引脚和地之间。但上述电压范围对于某些应用也许太窄。凭借图1中的电路,你可以利用两个施加给非逆变输入端的基准电压来加宽滞后量范围。该电路用IC3(Analog Devices公司的ADR390B)来产生高基准电压VREFH,大小为2.048V。分阻器R1/R2产生低基准电压VREFL,大小为0.2048V。即1.8432V的压差。因此,滞后量等于高基准电压减去低基准电压。IC2(Analog Devices公司的ADG772双SPDT开关)把这些电压传输到比较器的非逆变输入端(参考文献2)。

图1,模拟开关改变了比较器的基准电压,由此增加了滞后量。

当比较器逆变输入端的输入电压超过高基准电压时,输出变成逻辑低。这一作用迫使S1B把低基准电压连至比较器的非逆变输入端。电路保持在这个状态,直到输入电压降至低基准电压之下。此时,开关把高基准电压连回比较器。对于输入端的快速上升波形,滞后量会由于IC1和IC2内部的信号传播延时而增加。ADCM609中的35ns传播延时出现在输入过驱的大约10 mV处,并且过驱实际上会增加一倍左右,使滞后电压增加大约1%。

由于ADCMP60x比较器是轨到轨I/O器件,因此低基准电压可能为0V。但在此情形下,0.2048V的值使比较器与依靠相同电源电压的其它轨到轨I/O IC合作。这些IC的输出可能会在0V至电源电压之间摆动,裕量为数毫伏至数十毫伏,这取决于负载。ADR390B提供基准电压(参考文献3)。在Q输出端的电压瞬态期间,2.2 nF解耦电容抑制这些电压的变化。由于从开关的控制输入端IN1到各自通道的源极的寄生电荷转移量通常为0.5 pC,因此上述值适用。解耦后的基准电压的短期变化量小于250 µV。

参考文献:

1. “ADCMP609 Rail-to-Rail, Fast, Low-Power 2.5 V to 5.5 V, Single-Supply TTL/CMOS Comparator,” Analog Devices, 2007 to 2008.

2. “ADG772 CMOS Low Power Dual 2:1 Mux/Demux USB 2.0 (480 Mbps)/USB 1.1 (12 Mbps),” Analog Devices, 2007 to 2008.

3. “ADR390/ADR301/ADR392/ADR395 Micropower, Low Noise Precision Voltage References with Shutdown.”