基于FPGA的实时心电监护系统设计

2008-07-07

作者:杨永明, 韦建敏, 刘俊刚, 黄

摘 要: 介绍了一种基于现场可编程门阵列(FPGA)的实时心电" title="心电">心电监护系统。该系统采用FPGA为中央数字处理器,采用硬件描述语言(VHDL)进行结构化设计,实现了心电信号(ECG)的实时采集、处理和传送。同时还在芯片内集成了数字滤波和数据压缩存储算法,实现心电信号的实时处理和压缩。

关键词: FPGA 心电信号 实时监护

近年来随着数字信号处理技术的发展,心电监护系统得到了较快的发展。但是现有的监护系统多采用单片机作为中央处理器,不但处理速度慢,而且功耗和体积大,实时性差。针对便携式心电监护系统需满足的处理速度快、功耗低和微型化等要求,本系统选择了FGPA为中央处理器,进行心电数据的采集和处理,使系统具有实时采集、处理、存储以及发送心电数据等功能。

1 系统硬件组成

系统的硬件部分以XILINX的低成本型SpartanTM-3器件XC3S400-4TQ144C[1]为核心,主要包括ECG信号滤波放大电路、QRS波检测电路、FPGA控制系统等。其硬件构成如图1所示。

1.1 滤波放大电路

滤波放大电路的作用是从噪声中提取心电信号,并把它放大到合适的电平以提供给A/D" title="A/D">A/D转换电路。

前置放大电路选用仪表放大器AD620,放大倍数为11。主放大电路和后置放大电路放大倍数分别设计为50、1~3。整个电路放大倍数为550~1650连续可调。

高通滤波器采用无源RC滤波器;采用运放TLC2254设计了由4个二阶压控电压源(VCVS)低通滤波器级联构成的八阶低通滤波器。

1.2 A/D转换电路

本系统对心电信号进行数字化处理的分辨率为12位。FPGA拥有丰富的I/O口,所以选择转换方式为并行,采样频率为1kHz。本系统对A/D的速度、精度都没有特殊要求,需考虑的主要是体积、低供电电压和功耗。经比较最终选用了MAXIM公司的并行接口A/D转换器MAX1297。将其并行接口以及控制信号" title="控制信号">控制信号与FPGA相连,由FPGA提供芯片所要求的转换时钟以及控制信号。

1.3 R波检测电路

R波的检测分为硬件和软件检测。相对于软件实现来说,采用硬件实现R波检测具有速度快、实时性好、结构简单的优点。系统中,R波检测电路由跟随器、QRS滤波器、整波电路、峰值保持电路和比较器组成[2]。预处理后的心电信号经R波检测电路被转换为方波信号,再输入FPGA进行处理。

2 FPGA实现的主要功能

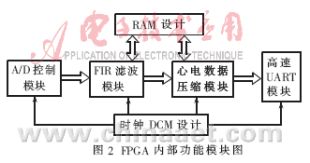

如图2所示,FPGA 内部主要有A/D控制模块、SRAM控制模块、FIR滤波模块、心电数据压缩模块、时钟产生模块和串口通信模块。

2.1 A/D控制

由于选用的A/D芯片为双通道,所以内部模块也按照两通道来设计,分别为outdata1和outdata2,数据为12位,CLK端口接外部时钟接口,该模块内部嵌入了时钟产生模块,输入50MHz信号,输出ad_clk信号为400kHz,占空比为50%。在本模块中每400个周期对CH0和CH1通道分别取一个点,输出到outdata1和outdata2,采样率为400kHz/400=1kHz。该模块的顶层图和功能仿真如图3所示。

2.2 数字滤波

为了进一步滤除因前置处理电路而加重的工频干扰,本系统集成了分布式FIR数字滤波器[3]。

2.3 SRAM 控制

系统中配置的是256K×16bit的SRAM、18位地址线、16位数据线,CS、OE和WE分别作为SRAM的片选信号、读使能和写使能信号,这三个信号均为低电平有效,由UB和LB分别控制每次读写的是高字节还是低字节。本文依据该芯片的功能在FPGA内部设计了SRAM控制模块,其顶层图如图4所示。

该模块中的控制信号有ram_ce、ram_full、ram_lb、ram_oe、ram_ub、ram_we。其中ram_ce用于给SRAM芯片提供片选信号,ram_full用于标示SRAM存储器中的空间,ram_oe信号用于给外部SRAM芯片输出使能信号;ram_we用于给外部SRAM芯片读写控制信号;外部SRAM芯片的I/O0-I/O15为16位数据线,模块中用两个信号ram_ub和ram_lb分别控制其高字节和低字节。

该模块中用到的时钟信号有两个,一个是SRAM写时钟ram_wclk,一个是SRAM读时钟ram_rclk,这两个时钟均由时钟产生模块生成。因为SRAM的写入数据是A/D转换后的数据,所以ram_wclk写时钟应该与AD的数据频率一致为1kHz。从SRAM读数据时,是读给后面的心电数据压缩模块处理,系统中的心电数据处理模块的时钟为50MHz,所以读数据时,采用50MHz,这样可以最大限度地提高系统的实时性。

模块中有两个地址信号: dsp_addr<17:0>和ram_addr<17:0>。dsp_addr<17:0>来自心电数据压缩模块,ram_addr<17:0>是用于给外部SRAM芯片地址信号。

该模块的数据信号有三个:ad_wdata<11:0>、dsp_rdata<11:0>和ram_data<11:0>。这三个数据信号分别与前面的AD转换模块、后面的心电数据压缩模块及FPGA外部的SRAM芯片连接。

2.4 心电数据的压缩和通信

为了能实时存储和传送足够长的有用信号,对采集的ECG信号必须采取一定的压缩处理,为此该系统还集成了LADT数据压缩算法模块[3]。LADT模块的输入端口有三个,分别为数据输入端口dsp_data_in<11:0>、系统时钟端口dsp_clk和全局停止信号rst;输出端口有两个:数据输出端口dsp_data_out<11:0>和送给SRAM的地址信号dsp_addr<17:0>。该模块的顶层图和仿真结果如图5所示。

依据UART的通信原理在FPGA内部设计了异步通信模块,用于最终将实时压缩处理后的数据上传给上位机处理。异步通信模块的帧格式是8位数据位,一个起止位,一个停止位。其中波特率为可调,由时钟发生模块给予时钟信号。

发送模块" title="发送模块">发送模块中,din<7:0>为并行数据输入;clk16×为时钟信号,由时钟产生模块给予,在时钟发送模块中该时钟信号可调;rst为复位信号(复位信号“1”);wrn为数据传输控制信号(信号为下降沿时,读入数据);sdo为串行数据" title="串行数据">串行数据输出。并串转换后,在传送之前加一位起止位、停止位后,再通过对发送模块其他一些控制信号的编写,就完成了整个发送模块的设计。该模块的顶层图和仿真结果如图6所示。

当系统接收到上位机通过串行通信接口发送来的串行数据时,要将其转化为FPGA内部使用的并行数据,所以接收模块的主要作用是用于串-并转换。接收模块中,clk16×为时钟控制信号;rst为复位信号(当rst为“1”时,所有工作信号复位);rxd为串口发送来的串行数据;dout<7:0>为经接收模块进行转换后输出的并行数据;framing_error为帧错误信号。程序的主体思想是:首先将接收到的串行数据逐位地放入移位寄存器rsr中,当8位数据放满后输出给缓存rbr,并暂时保存在那里;当收到发送信号时再将8位的并行信号输出(这个过程实际上是发送模块的逆过程,是将串行数据变为并行数据,实现串并转换);再通过对接收模块其他一些控制信号的编写,就完成了整个接收模块的设计。该模块的顶层图和仿真结果如图7所示。

一个完整的串口通信应该有其协议,也就是说往往是上位机应先给下位机发送一个控制信号后,发送模块才工作,即两个模块应该协同工作,所以本文将这两个模块连接到了一起,并加入一些控制信号,从而设计出串口通信模块。模块中的rxd用来接收上位机的数据,并判断数据是“AA”或者“55”,“AA”表示开始接收数据,“55”表示停止接收数据。

2.5 时钟模块

时钟模块产生其他所有模块工作所需的时钟,时钟脉冲是控制信号以及系统能协调工作的基础。根据前面几个模块的时钟需求,设计了时钟产生模块。模块输入时钟为clk,其频率为50MHz,由外部有源晶振连接FPGA的全局时钟管脚GCLK0提供。其余输出时钟为提供给几个模块的时钟信号,其中ad_clk是送给A/D转换模块的时钟,da_clk送给D/A转换模块,ram_rclk和ram_wclk分别为SRAM模块提供读时钟和写时钟,dsp_clk为LADT模块的工作时钟,rxclk和txclk分别为UART模块的接收时钟和发送时钟。该模块的项层图和仿真结果如图8所示。 通过对FPGA芯片程序的下载,将6个功能模块集成于芯片XC3S400中,该芯片内部有40万门,最终顶层模块程序的资源占用情况如表1所示。从中可以看出,资源占用率很低,仅为8%,还留有大量的剩余资源,为系统的进一步完善和增添其他功能模块提供了可靠的保证,例如可以在FPGA芯片中增加心电数据分析模块和无线通信模块等。

本文设计了基于FPGA的集心电信号采集、存储、处理和发送等功能于一体的实时心电传感系统。 该系统在一片FPGA中完成了大部分实时监护功能,并可以用修改软件的方法来改进或增加其功能,与现有的便携式心电监护仪相比,更具智能性。

参考文献

[1] XILINX Corporation. Spartan-3 FPGA Family: Complete Data Sheet. DS099 March 4,2004

[2] 费保蔚,庄天戈,程敬之,等.一种心电图QRS波检测方法. 北京生物医学工程,1997,16(1):11-13.

[3] 韦建敏,杨永明,郭巧惠.基于FPGA的实时心电信号处理系统设计.电子器件, 2005,28(3):581-583.