数据采集系统是通过采样电路将输入的模拟信号转换成离散信号,并送入CPU、MCU或DSP进行处理。现在流行的基于PCI总线设计的采集卡是数据采集系统的主流,其优点是可以利用PCI总线的研究成果快速的开发系统软件,整体运行速度快,能够实现实时采集实时处理。但在一些工业测控现场检测大型设备时,从现场到机房有一定的距离,模拟信号传到安装在PC内的PCI数据采集卡会有不同程度的衰减,且易受工业环境的干扰。而单纯用由微控制器(MCU)为核心的数据采集系统时,把数据采集器置于被监测的设备处,虽然可以避免模拟信号的衰减和被干扰,但在这种数据采集系统中,A/D转换器的启动、读取数据并存入到存储器的整个过程由MCU来参与控制,由于受MCU执行指令时间的限制,采集的速率较低,难以适应高速信号采集的需要。本文利用ARM微处理器和CPLD器件组成的现场数据采集系统,然后通过以太网接口于上位机相连,就可以有效解决上述问题。

系统的设计方案

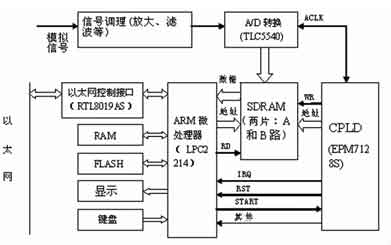

整个数据采集系统如图1所示。数据采集系统首先对采集的信号进行前端处理,如信号放大、滤波等预处理。采用的CPLD器件实现整个系统的控制逻辑,它控制着采集通道的切换、A/D转换的起/停、转换后的数据存放在存储单元的地址发生器、产生中断请求以通知ARM读取存放在存储器中的数据,由ARM微处理器进行快速的处理和传输。

图1 数据采集系统框图

1 信号调理模块

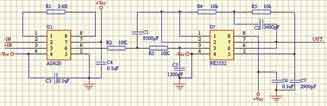

在信号进行数模转换前,在保证被采集信号不失真的前提下,对输入的信号进行放大、滤波等预处理。高速数据采集系统的输入信号通常为高频信号,需要进行阻抗匹配和前置放大,可以选用高速低噪声信号前置放大器和信号变压器。信号前置放大器的优势是:放大系数可变,信号输入的动态范围大,还可以配置成有源滤波器。但放大器的最高工作频率和工作宽带必须满足系统设计的需要,避免信号失真,同时应该考虑放大器引入的噪声损失,为避免对A/D转换器性能的不利影响,前置放大器的信噪比应远大于A/D转换器的信噪比。当频率远远大于100MHz时,尽可能采用信号变压器,其性能指标(如最高工作频率和工作带宽)优于信号放大器,而且信号失真很小,但信号放大系数固定,输入信号的幅度受到限制。该设计中采用前置放大器,其前端的信号调理电路如图2所示。

图2 信号调理电路

2 A/D转换模块

将连续信号转换成离散信号进而转换成数字信号以适用于处理的重要芯片是A/D转换器。一般的逐次逼进型A/D转换芯片的转换速度最多在每秒钟几万次,不能满足高速采样的要求。该设计中选择TI公司的TLC5540高速模数转换芯片,其具有8位分辨率,内置采样和保持电路,该芯片采用一种改进的半闪结构、CMOS工艺制造,因而大大减少了器件中比较器的数量,而且在高速转换的同时,能够保持低功耗,转换速率可达40Mb/s。

TLC5540以流水线的工作方式进行工作,在每一个CLK周期均启动一次采样,完成一次采样,每次启动采样是在CLK的下降沿进行,第n次采样的数据经过3个时钟周期的延迟之后,送到内部数据总线上,所以系统刚启动时读取的3个数据是无效数据,在软件设计时,必须抛弃系统启动时读取的前3个数据。

3 CPLD模块

该设计中采用ALTERA公司的EPM7128S, 它实现整个系统的控制逻辑。主要有下面几个控制模块电路构成:

- 时钟控制电路,提供A/D转换器的时钟信号(ACLK),该信号同时提供了给存储器的WR,以控制整个系统的采样频率。

- 地址产生电路,生成SRAM的地址控制信号,每写完一次SRAM, 地址自动加1。

- 地址总线切换电路,对内部地址发生器和LPC2214产生的两组地址进行切换,提供给存储器。当处于写存储器时,存储器的地址由内部地址发生器发生;当处于LPC2214读存储器时,存储器的地址由LPC2214的地址总线提供。

- 数据总线切换电路,对A/D的数据线和LPC2214的数据总线进行切换,当写数据时,使数据从A/D输出到存储器,读数据时,使数据从存储器读到LPC2214的数据总线。

- 地址译码及逻辑控制电路,完成对系统地址总线的译码,产生各种必须的控制信号。

4 MCU模块

该设计中采用Philips公司的LPC2214的微处理器,用它来对采集到的数据进行存储、显示、处理操作,并作为系统与上位机沟通的桥梁。LPC2214是基于ARM7TDMI核的RISC微处理器,ARM7TDMI为低功耗、高性能的16/32位核,最适合对价格及功耗敏感的场合。LPC2214在ARM7TDMI核的基础上扩展了一系列通用外围器件,使其特别适用于工业控制、医疗系统、访问控制,由于内置了宽范围的串行通信接口,使其也非常适用于通信网关、协议转换器、嵌入式软MODEM以及其他类型的应用。

5 ARM与网卡芯片接口设计

为使采集到的数据或处理后的数据传送到上位机,需在系统中增加以太网接口,通常有两种方法:(1)ARM微处理器+网络控制器,这种方法对处理器没有特殊的要求,只要把以太网芯片连接到处理器的总线上即可,此方法的通用性较强,不受处理器的限制;(2)采用带以太网接口的ARM微处理器,但通常这种处理器往往是面向网络应用而设计的,不是特别适用于工业领域。故该设计中选用第一种方法。

网路控制器RTL8019AS是目前比较常用的10Mb/s嵌入式以太网控制芯片,在芯片内部集成了DMA控制器,ISA总线控制器和16KB SRAM,网路PHY收发器。用户可以通过DMA方式把需要发送的数据写入片内SRAM中,让芯片自动将数据发送出去;而芯片在接受到数据后,用户也可以通过DMA方式将其读出。

系统基本工作原理

数据采集器置于被监控的设备处,对传送过来的模拟信号进行信号调理,LPC2214启动系统数据采集,CPLD控制器输出一个脉冲给A/D转换器的CLK端,使其开始第n次A/D转换,同时将CPLD内部地址发生电路产生的地址信号经地址选择器直接送到存储器,A/D转换器所采集到的第n-3次的数据经数据总线直接输入到存储器中保存。

由于采样频率高,用CPLD将采样数据存储到两路同步动态存储器(SDRAM)中。CPLD先把采集到的数据以DMA的方式存储到A路SDRAM中。 等数据写满A路SDRAM后,由CPLD器件引起LPC2214外部中断,LPC2214进入中断处理程序,读取SDRAM中的数据,并进行处理,同时CPLD将接下来采集到的数据以DMA的方式存储到B路SDRAM中, 等存储器B数据装满后,CPLD器件引起LPC2214外部中断,LPC2214进入中断处理程序,读取B路SDRAM中的数据,并进行处理,如此循环下去,完成数据的接收和传输并行。

可以看到ARM微处理器只控制数据采集的启动和对采集到的数据进行快速处理和传输,在数据采集的过程中,ARM微处理器不对采集通道进行任何控制,完全由硬件自动实现数据采集的全过程,实现了高速数据采集的目的。

系统软件设计

软件部分要分别编写LPC2214的处理模块程序和CPLD的控制模块程序,LPC2214的程序包括嵌入式操作系统μC/OS-II和各应用程序的编写,CPLD控制模块程序用VHDL语言来实现。

在编写处理器的处理程序时,如采用单任务顺序机制,系统的安全性差,这对于稳定性、实时性要求高的数据采集系统是不允许的,因此根据整个装置实现的功能和对它的要求进行系统任务的分割,并分配优先级,由操作系统来进行管理调度。本设计选用μC/OS-II操作系统,μC/OS-II V2.52已通过美国航空航天管理局(FAA)的安全认证,其采用优先级调度算法完成任务间的调度,支持抢占式调度,具有执行效率高、占有空间小、实时性能优良和扩展性强等特点,其内核还提供信号量、消息邮箱、消息队列、内存管理等系统服务。程序架构如图3所示。

图3 程序架构图

根据应用,本系统分为以下几个任务:软复位任务(程序对系统初始状态进行重新设定),对SDRAM的读取、与上位机的TCP/IP通信、显示任务、键盘管理任务和数据处理任务,任务间的通信通过消息队列来完成。系统中的每个任务包括应用程序、任务堆栈和任务控制块三部分。任务控制块是一个数据结构,当任务的CPU使用权被剥夺时,μC/OS-II用它来保存该任务的状态,当任务重新获得CPU的使用权时,任务控制块能确保任务从被中断的那一点执行下去,操作系统可以通过查询任务控制块的内容从而对任务进行调度管理。

在用μC/OS-II作为内核来编写数据采集系统系统的应用软件之前,必须完成μC/OS-II在微处理器的移植工作,由于μC/OS-II在设计之初就充分考虑了在不同处理器上的移植问题,其结构化设计把与处理器相关的部分分离出来,因此在任何处理器上的移植 μC/OS-II都只需要关心三个文件:头文件OS_CPU.H、文件OS_CPU_C.C和汇编文件OS_CPU_A.ASM。

为了满足系统与以太网直接交换信息的需要,本设计在μC/OS-II中移植了LWIP(Light Weight IP轻型IP协议)协议栈。LWIP是瑞士计算机科学院Adam Dunkels等开发的一套用于嵌入式系统的开放源代码TCP/IP协议栈。LWIP可以移植到操作系统上,也可以在无操作系统的情况下运行,LWIP实现的重点是在保持TCP协议主要功能的基础上减少对RAM的占用,一般它只需要几十字节的RAM和40Kb左右的ROM就可以了。

LWIP可以很容易地在μC/OS-II的调度下,为系统增加网络通信和网络管理功能。LWIP把所有与硬件、操作系统、编译器相关的部分独立出来,放在/src/arch目录下,因此LWIP在 μC/OS-II上的移植修改这个目录下的文件即可。

结论

在ARM微处理器中移入嵌入式实时操作系统μC/OS-II,使系统的稳定性、实时性得到保证,实时操作系统将应用分解成多任务,简化了应用系统软件的设计;采用CPLD器件集成了电路的全部控制功能,摆脱了单纯用由微控制器为核心的数据采集系统时的速度瓶颈,极大提高了数据采集速度。整个系统具有速度高、实时性好、抗干扰能力强、性价比高等特点。