1 引言

激光陀螺的工作原理是Sagnac效应,与传统的机械陀螺相比,激光陀螺具有精度高、耐环境性能好、动态性能好、启动时间短、寿命长及数字式输出等特点,是捷联式惯性导航系统的理想元件。目前激光陀螺已逐渐取代传统的机械陀螺,广泛应用于军用飞机、水面舰艇、战术导弹、民用航空、陆用车辆和定位定向系统等领域。

二频机抖陀螺工作电路包括高压电源、抖动驱动与噪声注入、稳频和信号解调等部分。系统设计以软核处理器为核心.实时控制稳频、抖动驱动与噪声注入和高压电源等单元,并实现陀螺读取信号的鉴相解调与数字滤波。

Nios II是Altera开发的嵌入式软核处理器,采用RISC精简指令集,具有外设可定制、可裁剪性等优点,可方便嵌入Cvclone及Stratix系列 FPGA。陀螺信号处理系统中需要多种定制化的外设,而一般处理器无法满足这种要求,因此NiosⅡ软核处理器是处理激光陀螺陀螺信号的理想选择。

2 系统结构设计

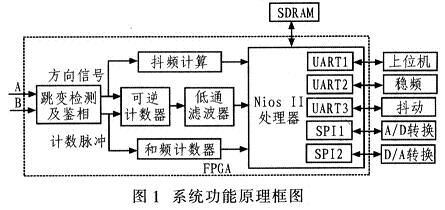

图1为系统的功能原理框图。图中A、B为光电转换器接收的拍频信号过零比较后产生的方波信号,这两路方波信号经跳变检测和鉴相后产生跳变脉冲和方向信号。可逆计数器根据方向信号对脉冲进行可逆计数,而和频计数器仍对脉冲进行正向计数。低通滤波器对可逆计数器的计数值进行滤波,并将滤波值输入到处理器。UART1和上位机通讯,而UART2和UART3分别与稳频和抖动电路通讯,以控制稳频和抖动参数。2个SPI接口分别控制A/D转换和D/A转换的部分。

考虑到系统资源要求,FPGA采用Altera公司生产的EP2C200240C8,它属于Cyclone II系列,其内部资源主要有:多达两万个逻辑处理单元(LE);52个M4K模块,总共26 KB的片内RAM;26个18×18硬件乘法器;4个全局时钟锁相环;多达142个外部引脚。系统选用快速型Nios II处理器,处理器占用3 000多个逻辑处理单元,工作时钟为100 MHz。由于系统处理器程序运行在SDRAM中,所以在构建系统时要添加SDRAM控制器,SDRAM使用HY57V283220,其存储空间为16 M字节,完全能够满足处理器实际需求。处理器程序固件和FPGA的配置信息存储在EPCS串行配置器件中,这样可减少一片外置Flash。因为程序从 EPCS启动,所以在SoPC设计时添加外设EPCS控制器以引导程序的初始运行。

3 信号滤波实现

激光陀螺的读取信号是由两个光电管经光电转换后产生的,工艺上要保证两个光电管的拍频相位相差90°,这样便于在信号处理时进行相位检测。为了尽量减小锁区带来的误差,一般在陀螺中加入一个正负交变的正弦偏频信号:

根据Sagnac效应,若外界的角速度为Ω转,则激光陀螺输出差频为:

![]()

式中,A为环形激光器的面积,L为激光腔的总长。

对式(2)积分可得:

![]()

为了有效提取信号,通常是对可逆计数器的计数值(即式(3)的积分值)进行滤波。

这里采用FIR数字低通滤波器,如果FIR滤波器的系数对称,则具有精确、严格的线性相位,这正是实际导航应用所要求的。为了兼顾实时性和防止信号产生混迭,设定采样率为2 kHz,采用高阶FIR滤波器。

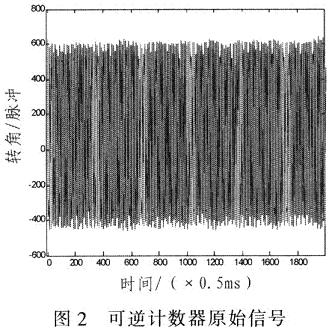

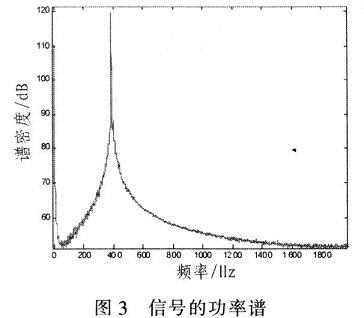

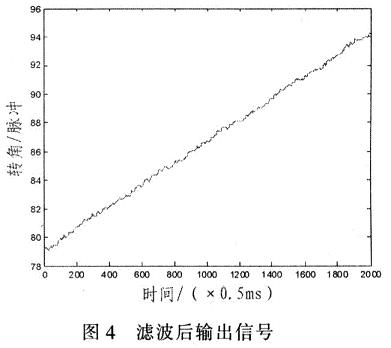

图2为1 s内采集的可逆计数器的输出信号,从图中可看出:有用信号已被抖动信号和量化噪声完全覆盖。图3为信号的功率谱,从图中可看到,抖动信号在功率谱中占很大分量(功率谱的最大值处的频率对应抖动频率),还原出被测量信号必须对可逆计数器的输出信号进行低通滤波,以滤除抖动及其他杂散信号。图4为滤波后的脉冲输出,不同于图2,从图4中可清楚地看出:在2 000点(即1 s时间内)恒定地球转速下累计约15个信号脉冲。

可编程逻辑器件为FIR滤波器的设计提供高灵活性,可采取多种结构,例如并行流水线结构、串行结构等。考虑到采样率相对不是很高,为节约系统资源,这里采用自行设计的串行结构滤波。