前言

随着通用移动通信系统(UMTS)网络在日本和欧洲实现商用,市场对多频段宽带码分多址(W-CDMA)收发器芯片的要求更加苛刻——除了缩小芯片面积和主板占用空间、减少组件数量、降低材料成本外,还要求芯片具备足够的灵活性,不仅要支持工作频段I,还要支持其他多个频段。考虑到UMTS的全双工性质,再加上支持所有频段要求在面积更小的芯片上集成多个发射和接收通道,如何最大限度降低这些通道之间的串扰,就成为一个非常具有挑战性的任务。第一颗采用0.13微米CMOS工艺制造的单芯片直接转换收发器于2003年2月面世;第一颗采用0.35微米SiGe BiCMOS工艺制造的单芯片 UMTS收发器于2004年正式推出。最新发布的直接变换设计包括一个采用0.35微米SiGe BiCMOS工艺制造的适用于WCDMA/HSDPA网络的三频段单芯片收发器。

本文介绍了一种适用于频分复用(FDD)网络的低功耗、多频段、全集成化单芯片UMTS W-CDMA/HSDPA直接转换型收发器。它采用 0.13微米CMOS工艺制造而成。该设计包括三条零中频接收(RX)通道,三条直接转换型发射(TX)通道,两个分数型频率合成器。它们都由一个多标准编程接口控制。图1显示了该芯片的完整框图。

接收器包括差分输入端口、第二低噪放大器级(2nd LNA)、两个下变频器(带CMOS Gilbert型混频器以及紧随其后的低噪缓冲放大器)、一个经过校准的模拟有源六阶基带(BB)滤波器,并且伴随一个附加的二阶可编程陷波滤波器(2.7 MHz)。所有直流偏置由内部电路补偿。

该收发器包括一个Butterworth型三阶模拟有源基带滤波器,以及三个直接上变频器、可变增益放大器(VGA)级(每条通道的增益控制范围超过85dB)、高功率输出驱动级(典型输出功率为11dBm)。VGA级的自适应偏置,可确保整个输出功率范围内功耗最低。

混频器包括全集成式压控振荡器(VCO),后者集成了片上调谐电路、自动上电校准和环路滤波器等功能。

所有功能均由一个基于三线制总线设计的灵活的多标准编程接口控制,这不仅实现了后向兼容,而且可支持DigRF标准所规定的全部读/写存取操作。

该器件的工作电压范围为2.7 -3 V,工作环境温度范围为-30℃至+85℃,可配置成不同的参考振荡频率以及不同的基带接口参数(例如 I/Q共模电压),从而实现最佳兼容性。多种节电模式可确保各类操作情景下的功耗最低。接收通道的最大功耗为通道的最大功耗为35mA(打开陷波滤波器时为37mA),而发射器的功耗始终低于80mA。如果发射和接收功能都没有启动,一个被称为“睡眠模式”的特殊操作模式将被激活。在这种模式下,器件的典型功耗一般为2mA。如果移动终端(UE)未被用于无线信号收发(例如,正在使用高级移动终端都具有的个人数字助理(PDA)功能),这对于延长电池工作时间非常有用。在睡眠操作模式下,所有的寄存器设置都保存在一个特殊的随机存取存储器(RAM)中,这样,在下次被唤醒时,集成电路就能取回所有的设置。

如果被用于多模环境,该收发器可作为功耗最低的前端控制中心,以及活动的备用收发器(例如GSM收发器)。其实现方式是:激活一个特殊的工作模式,该模式可关闭发射和接收功能,从而实现功耗最小化,并且对所有6个前端控制输出引脚进行仲裁设置。

该芯片采用非常袖珍的无引脚封装技术—PG-WFSGA-81-1 (超细间距半球珊阵列),面积仅为5×5毫米,最大高度为0.8毫米。球珊间距为0.5毫米。

分数型频率合成器

接收器和发射器都集成了参考频率为26MHz的分数型频率合成器,同时搭载了参考电阻器。较低的带内相噪,为使用更宽的PLL环路带宽(目的是全面集成环路滤波器)创造了条件,因此可最大限度减少外部组件的数量。要覆盖所有的工作频段(包括附加的频率容限),在4GHz频段工作的差分VCO有一个很宽的调谐范围,它被划分为256个VCO频段。可以通过在VCO RF输出端口激活一个附加的二分频器以支持UMTS频段V和频段VI。相应的VCO频段由内部的标定算法进行选择,该算法将在PLL被启动或者一个新的频点被设定时被触发。同时,进一步的校准可最大限度降低PLL的偏变,例如环路滤波器拐角频率的离散等。

图2显示了混频器相噪模拟量。

超低带内相噪是实现接收器和发射器误差向量幅度(EVM)最小化的重要基础。

零中频接收器

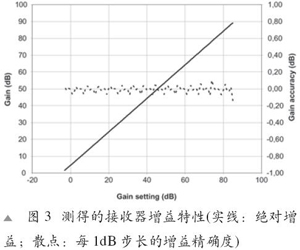

根据过去发布的一个设计,每条接收通道由一个0o/90o I/Q主-从二分频器驱动,后者可产生为直接将差分射频输入信号混频至基带滤波器的异常精确的正交信号。可编程增益放大器(PGA)的增益范围为89dB,每dB步长的步长精度大约为0.1dB,整个增益范围的步长精度为2dB。

主要针对增益步长采用R-2R网络即可实现上述精确度。在解调器的后面,采用一个六阶Chebychev型跳耦结构滤波器(带面向I/Q基带接口的差分信号)进行抗锯齿失真和信道隔离处理。可通过软件编程方式激活附加的2.7MHz陷波器,从而满足UMTS频段II和III的要求。整个滤波器得到了优化,最大振幅误差为±0.5 dB,相位畸变不超过±3o。在接收器初始化期间,滤波器的2.275MHz的拐角频率被校准,结果使整个采样和温度范围的偏差仅为5%。基带滤波器特性的模拟量参见图4,其中,实线代表随频率变化的正常滤波器衰减,虚线对应的是被激活陷波器级的特性。

为了最小化增益转换时的DC瞬变,接收链中的所有运算放大器的偏差均被校准为零。一个拐角频率为3.75KHz的附加DC环路可清除所有的残余DC偏差。因此,在增益变化时,瞬态DC偏差不会超过±50 mV。

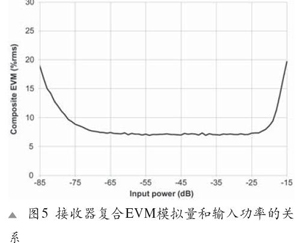

接收器的最小三阶交调截取点(IIP3)为-6 dB,二阶交调截取点(IIP2)大于35 dBm。高增益范围的噪声系数优于12dB。最大 EVM为12.5%(有效值),使得接收器能够被用于高速下行分组接入(HSDPA)7/8类网络。典型采样的EVM大约为8%(有效值),如图5所示。

低功耗射频前端设计

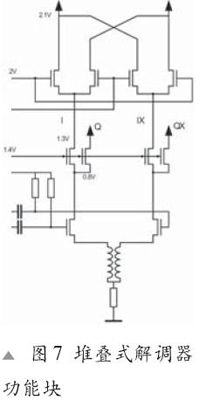

尤其对于CMOS设计而言,最重要的是最大限度降低电路功耗,从而克服该项工艺的固有缺陷。由于接收器的功耗是一个重要的预算参数,我们选择了一个先进的射频前端。依据有关文献中所发布的一个设计,VCO分频器和解调器分别直接位于VCO缓存器和LNA之上。因此,两个功能块共用一个输入电源,从而显著降低了器件功耗。具体工作原理如图6所示。

图7显示了LNA -解调器功能块。

直接上变频发射器

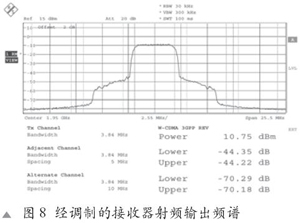

发射器内含一个完全差分化可编程输入缓冲器,以处理不同的基带输入信号。一个附加的三阶Butterworth型基带滤波器(校准角频为 4.4MHz)能够消除各类有害的信号内容(譬如基带DAC的杂散辐射等),同时不会对有用的信号产生过大的干扰。此外,精度高于±0.2 dB的可调 -1 dB和-2 dB增益步长,能够处理各类HSDPA信号群的较高波峰因子。通过提高以下所述的增益控制输入引脚的电压可以补偿衰减,并且形成一个 “高线性度”模式,以符合线性度规范要求。基带滤波器输出信号可驱动直接变换式调制器(每条发射通道一个)中集成的Gilbert型混频器的输入级。由于布局高度对称并且完美匹配,再加上在发射器初始化时采用了一个校准程序,DC偏差始终保持在很低的水平(在高输出功率范围内通常为-40dBc)。射频输入由来自集成化VCO(高频段和中频段通道为二分频器,低频段通道为四分频器)的0o/90o信号驱动。混频器的输出信号然后被缓存,并被发送至射频差分输出引脚。总增益一般超过95 dB,分布在基带和射频模块。通过在不同级上分配增益(按照优化的加权因子),可实现VGA的近似对数线性特征。通过在增益控制引脚(TXGC)上施加适当的电压(0.5-2.2 V),-77dBm至+7dBm的保证输出功率范围(取决于所采用的UMTS频段和发射通道)可达到控制。最大功耗(通常为80mA)可随输出功率的下降快速下降,在低增益范围内可降低至26mA。当输出功率最大时,在相应的接收频段,发射通道一般可实现-152 dBc/Hz的本底噪声,同时保持-43dBc的ACLR(有余量)和3%的EVM(典型值)。图8显示的是中心频率为1950MHz 时的典型调制输出频率。

芯片接口

串行控制总线

该集成电路由两个独立的串行三线制总线控制。其中一条总线负责控制常规配置,另一条独立的总线用于设置接收增益。编程接口可后向兼容前代产品并可根据DigRF标准处理相关命令。最大总线时钟频率等于参考时钟频率(15.36 MHz至38.4 MHz)。也可通过主用三线制总线(负责配置的总线)对接收增益进行设置。在本例中,备用总线引脚可被用作GPO(通用输出)引脚。

前端控制

由于多频段和多模操作所导致的前端复杂度的加大,要求我们对外部组件(例如LNA、PA和转换器等)进行有效控制。因此,该集成电路包含非常灵活的软件编程前端控制功能模块,它可通过以事件触发方式转换6个专用输出引脚满足外部组件控制要求。为了确保兼容未来的前端组件(例如三增益LNA),可选择一个电压级别可变的附加逻辑“高”信号。

操作测试功能

可通过启动一个特殊的测试模式和读回测试图形对集成电路功能进行检查,例如检查是否有所有输入电压等。这有助于查明生产过程中的焊接问题。在操作过程中,锁定检测引脚逻辑状态可跟踪接收器和发射器PLL的锁定状态。利用这些信息,信道转换防护间隔可被最小化。

芯片布局

图9显示的是该集成电路的缩微图。接收器射频通道位于右侧,左上角是调制器和基带滤波器。接收器VCO位于芯片中央。发射器基带滤波器位于芯片左下角,在发射器PLL环路滤波器和发射器VCO的下方。发射调制器和射频输出通道位于芯片下缘。

结语

支持UMTS FDD标准所规定的所有工作频段的单芯片全集成化3G UMTS/W-CDMA收发器已经推出。该集成电路采用标准化0.13微米 CMOS工艺制造而成。该设计包括两个分数型频率合成器(搭载全集成化VCO、片上调谐和PLL)、零中频接收通道和直接转换型发射器通道。接收器和发射器都具备出色的性能,为创建满足UMTS最低性能规范(带容限)的平台解决方案创造了条件。该器件的工作电压为2.7-3 V,接收模式下功耗为 35 mA,在发射器活动时的最大功耗为80 mA。这些结果表明了本文所述收发器的竞争优势,因为它可同时满足BiCMOS工艺产品的功耗和性能要求。该芯片采用非常袖珍的无引脚封装,面积仅为5×5毫米,高度仅为0.8毫米,完全符合ARIB WCDMA和UMTS标准。