引言

近些年来,随着集成电路制造工艺和制造技术的发展,SRAM存储芯片在整个SoC芯片面积中所占比例越来越大,而SRAM的功耗也成为整个SoC芯片的主要部分。同时,CPU的工作频率逐年提高,从1999年的1.2 GHz增长到2010年的3.4 GHz。而且,这一趋势还在进一步加强。CPU工作频率的增加对SRAM的工作频率提出很高的要求。

针对以上,提出位线循环充电(CRSRAM)SRAM结构,它主要是通过降低位线电压的摆幅来降低功耗。采用双模式自定时电路(DMST)则主要是根据读写周期的不同来产生不同的时序信号,从而提高读写速度。基于不同SRAM存储阵列结构,虽然这种技术能有效地改善SRAM的功耗和速度,但它们却从来没有被有效地结合在一起。

本文的主要内容就是设计并仿真基于位线循环充电SRAM结构的双模式自定时电路(DMST CRSRAM),并将其仿真结果与传统结构相比较,由此可以看出这两种结构在速度和功耗方面的优势。

1 多级位线位SRAM结构及工作原理

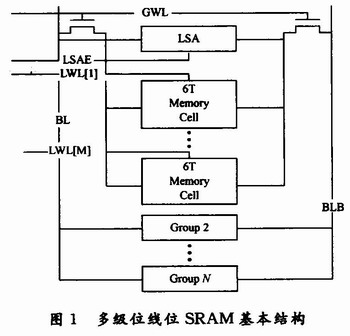

如图1所示,多级位线SRAM(HBLSA-SRAM)的主要原理是利用两级位线和局部灵敏放大器来使主位线写入周期中的,BL和BLB上的电压摆幅是一个很小值,而通过局部灵敏放大器将这个电压放大为VDD到0的大摆幅信号输入到局部位线上。这样,位线的电压摆幅减少,而且VDD到O的大摆幅写入保证了足够的写裕度。

HBLSA-SRAM不仅可以降低位线的电压摆幅,还可以有效地减小位线的电容负载。位线的负载电容很大程度上取决于位线上连接的MOS管数量。如图1所示,在每一个Group中有M个存储单元,而一共有N个Group,所以总共有M×N个存储单元。对于一个传统的SRAM结构有如此的容量,那么其位线上一共会接M×N个MOS管。但对于HBLSA-SRAM来说,将连接到主位线和局部位线的MOS管加在一起也不过N+M+5个。其中,对于主位线一共连接N个MOS管,而局部位线一共连接M+5个MOS管,M为M个存储单元的传输管,有1个来自与主位线连接的MOS管,另外4个来自局部的灵敏放大器。所以,不但位线摆幅显著下降,而且位线电容负载也下降了。

HBLSA-SRAM的读写功耗与传统的SRAM比较如下:

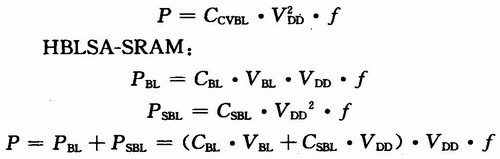

(1)对于写入功耗

传统的SRAM:

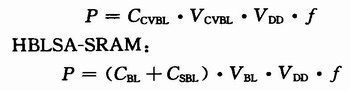

式中:PBL代表主位线上的功耗;PSBL代表局部位线上的功耗;CBL代表局部位线的电容负载;CSBL代表主位线的电容负载;CCVBL代表传统结构位线的电容负载;VBL代表局部位线的电压摆幅。通过之前的分析,有(CBL+CSBL)

传统的SRAM:

式中:VCVBL代表读出传统结构的位线电压摆幅。可以认为,VCVBL和VBL近似相等,所以HBLSA-SRAM的读出功耗也小于传统的SRAM。

2 基于位线循环充电SRAM模式的自定时电路设计

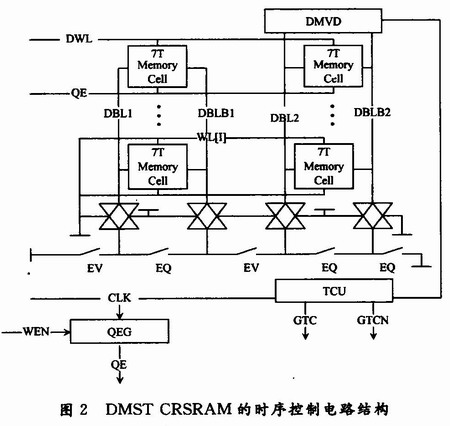

将位线循环充电SRAM的结构与双模式自定时电路相结合,为了进一步减小CRSRAM的功耗和优化器读写延时,提出基于位线循环充电SRAM的双模式自定时电路结构(DMST CRSRAM)。其时序控制电路如图2所示。

为了使CRSRAM和双模式自定时电路更有效地结合起来,对CRSRAM的基本结构做了三个主要的改变。

(1)传统CRSRAM结构中,位线电压在每次读操作之前都要被预充到VDD。这样有两个缺点:一是增加了额外的读写操作转换的控制电路,以及将位线电压预充到不同电压的电路。二是预充电到VDD增加了额外的位线摆幅。如果读写操作交替出现的话,那么预充电会消耗很大的功耗。

这里设计的电路结构中,不论读操作还是写操作都是以同样的位线电压开始的。这样做会导致在读操作中,从存储单元到位线的充放电电流会使位线上的电压出现浮动,位线上的电荷会有无法完全预计的损失或增加,由于没有了预充电电路,位线的电荷不可完全预计的变化会对电路的读写能力产生影响。但是,由于位线的电容负载较大,而存储管的驱动能力较小,所以读操作对位线的电荷的影响不会使电路功能出现问题。

(2)为了使控制电路变得简洁,把求值模式放在平衡模式的前面。这样,时序控制时只要控制求值模式的时间长度,而将时钟周期的剩余时间直接作为平衡模式的时间长度。因为,平衡模式与求值模式不同,过长的平衡模式时间不会增加额外的功耗。

(3)由于写入时CRSRAM的位线电压是小摆幅,所以为了确保写入操作的正确和提高写入的速度,用7管结构的存储单元代替传统的6管单元结构的存储单元。7管结构的存储单元的结构如图2所示。其工作原理:每次在读操作中,先是QE=1,将存储单元的存储数据消掉,再将Q0和Q1的点位拉到同一值。这样,小的位线电压摆幅可以顺利写入。

如图2所示,DMST CRSRAM的时序控制电路包括四个部分:复制阵列、双模式电压监测器(DMVD)、时序控制单元(TCU)和QE信号产生电路(QEG)。

在复制列上,原本的Exchanger被化简成DIN均为1时的情况,而且复制列上所有的虚拟存储管的Q0被强制为0,Q1被强制为1。所以在求值模式中,DBL的电压被上拉,而DBLB的电压被下拉。那么Q0的逻辑0会提供给DBL一个下拉电流,以减缓其电压的上升,同样Q1的逻辑1会提供给DBLB一个上拉电流,以减缓其电压的下降。所以,这样就在虚拟位线上模拟了位线电压在最慢情况下的变化过程,即可以确保真实位线上的电压在DMVD触发前就已经达到了操作所需的电压值。

DMVD由两个参考电压不同的比较器以及由读写使能信号WEN控制的两个传输管组成。灵敏放大器用来监测DBL和DBLB上的电压差,一旦达到了预定的参考电压值便被触发,而WEN控制的传输管负载分别在读周期和写周期,使其对应的灵敏放大器被触发后,其输出作为信号P输入到时序控制单元TCU。

TCU本质是一个异步电平触发电路,其工作情况如下:当CLK上升沿到来后,GTC也随之上升;而当P信号上升沿到来,GTC信号则回落到低电平。GTCN为GTC的反向信号。QE信号产生电路(QEG),当只有CLK上升沿时,由于延时单元的作用,QEN信号为高电平,脉宽为延时时间。而WEN控制QEN信号只有在WEN=1时(写周期)才输出QE信号。接下来,可以利用GTC和GTCN去控制整个电路。其中,A[i]代表行译码;A[j]代表列译码。在写周期之中,CLK上升输入到TCU之中,GTC变为高电平,同时GTCN变为低电平;随后EQ变为低电平,平衡模式结束。对于列选中的位线,EV和WL变为高电平,进入求值模式。写周期EV信号也作用在虚拟位线上,使其产生电压差,当虚拟位线上的电压差到达足以写入数据时,DMVD被触发产生P信号,P信号输入到TCU之中,使GTC再次变为低电平,GTCN变回高电平;随即,EV和WL变为低电平,EQ变回高电平,电路从求值模式转变为平衡模式。在平衡模式中,所有的位线包括虚拟位线的电压都被充放电回到初始值。这次写操作结束,电路对下一次的操作做好准备。

在读操作中,这个过程是类似的。CLK上升输入到TCU之中,GTC变为高电平,同时GTCN变为低电平;随后EQ变为低电平,平衡模式结束。不同的是,读周期中,EV信号一直为低电平,所以只有WL上升到高电平,才进入求值模式。此时,DWL信号也上升到高电平,使虚拟存储单元下拉DBL上的电压,当DBL上的电压足够低时,DMVD被触发产生P信号,信号输入到TCU中,使GTC再次变为低电平,GTCN变回高电平;随后,D-WL和WL变为低电平,EQ变回高电平,电路从求值模式转变为平衡模式。在平衡模式中,所有的位线包括虚拟位线的电压都被充放电回到初始值。这次读操作结束,电路对下一次的操作做好准备。

3 结语

双模式自定时技术分别针对读写周期产生不同的时序信号,并借此来改善SRAM的时钟周期和功耗。双模式自定时技术考虑了位线上的寄生电容和电阻,存储单元不同的写入响应时间,以及依赖于存储数据的位线的漏电流。仿真结果说明,这种双模式自定时技术使时钟周期降低了16%~30.7%,写入功耗降低了15%~22.7%。