面向高分辨率面阵CCD的新型信号采集系统设计

2008-10-23

作者:李 旻 赵群飞 杨汝清 贺

摘 要: 设计了一种新型高分辨率面阵CCD信号采集系统。该系统采用集成了时序发生器" title="时序发生器">时序发生器和模拟前端" title="模拟前端">模拟前端电路功能的模块AD9995驱动面阵CCD,经高速A/D" title="A/D">A/D转换后的各像素数字信号在DSP中的DMA控制器管理下通过DSP的PPI接口直接传输至片外SDRAM存储器。该系统结构紧凑,噪音干扰小,可用于高性能数码相机和实时图像采集与处理等场合。

关键词: 电荷耦合器件 数字信号处理器 直接存储器访问 并行外部接口 信号采集 模拟前端

电荷耦合器件CCD(Charge Coupled Device)是一种金属-氧化物-半导体结构的新型图像传感器器件。它能存储由光产生的信号电荷,当对它施加特定的时序信号时,其存储的信号电荷便可在CCD内部作定向传输而实现自扫描。由于它具有几何精度高、稳定性好、噪音小等优点,因而在遥感遥测、天文测量、非接触工业测量、光学图像处理等领域得到了广泛应用。近年来随着大面阵CCD生产工艺水平的提高和价格的下降,极大地促进了数码相机、数码摄像机等新兴消费类电子产品的发展,并迅速形成惊人的市场规模。本文主要讨论面向高分辨率面阵CCD的一种新型信号采集系统的软硬件设计和实现。该系统可用于数码相机以及对分辨率要求较高的图像处理场合。

1 系统设计

系统的原理框图如图1所示,被观测物经过光学镜头映射在CCD图像传感器的光敏阵列上,通过CCD内部将光信号转化为电信号。当时序发生器对其施加特定时序的脉冲时,每个像素的电荷信号将被依次移出CCD并经放大变成电压幅度不等的模拟信号。这些信号将会被送到外部独立的模拟前端(AFE)电路并转换为数字信号,这些数字信号就是传感器捕捉到的原始图像信息。在本系统中,采用AD公司新近推出的AD9995芯片,它集成了时序发生器、模拟前端以及A/D转换器的功能。AD9995中的时序发生器(Time Generator)产生CCD的驱动脉冲(V1~V6,H1~H4),CCD在驱动脉冲的作用下输出像素电压信号给AD9995,由AD9995内部的模拟前端电路调理后经A/D转换器产生数字信号并行输出;之后这些数字信号通过DSP的PPI接口,在DSP中的DMA控制器控制下,高速存储到DSP的外部存储器SDRAM中,以待进一步的图像处理。

2系统硬件组成及实现

2.1 CCD芯片

本系统采用的ICX432DQF是SONY公司生产的一款3.24M有效像素的行间传送面阵CCD(如图2所示),它具有高感光度,暗电流非常小,并带有电子快门功能,要求的水平驱动时钟频率为24.3MHz,需要六相垂直驱动脉冲和两相水平驱动脉冲来驱动。V1~V6为垂直脉冲输入引脚,H1、H2为水平脉冲输入引脚。在CCD曝光成像之后,首先会在驱动脉冲的作用下将每一列成像势阱中的电荷移送到旁边的垂直寄存器(掩膜阱)中,在垂直驱动脉冲的作用下,垂直寄存器组" title="寄存器组">寄存器组中所有像素电荷向下移动一行,此时最下边一行的像素电荷便被移送到水平寄存器中;之后在水平驱动脉冲的作用下,水平寄存器中电荷被依次移出,经放大形成电压信号由VOUT引脚输出,水平寄存器被移空后,所有余下的电荷又被下移一行,然后水平寄存器中的电荷再依次被移出。重复这个过程直至所有像素电荷被移出。

根据此款CCD的要求给其提供不同的垂直驱动脉冲组合,CCD可以按三种不同的方式输出图像:帧输出模式、高速输出模式和聚焦输出模式。帧输出模式下,CCD的所有有效像素电荷全部输出,图像具有最高的分辨率,在输出的过程中整帧图像分成三个场分别输出,之后再重组成一幅图像,此时的输出速度可达5帧/秒;高速输出模式下图像的输出速度可达30帧/秒,在此模式下并不是将全部像素电荷输出,相当于每六行输出一行,高速输出模式可以满足数码相机的预览功能;还有一种是为了实现图像快速聚焦功能的聚焦输出模式,此种模式下只将CCD中心区域的像素电荷输出,输出速度可达60帧/秒。

2.2 时钟驱动和模拟前端模块

AD9995是一种面向数码相机和便携式录像机开发的高度集成的CCD信号处理器。它由带A/D转换器的模拟前端(AFE)和一个可编程的时钟发生器两大功能模块组成。由于AD9995把时序发生器和AFE集成在一块芯片上(如图3所示),不但可减小PCB板的尺寸,同时也使高速信号在传输与处理时的噪声得以降低,并减小了耗电量。在CCD工作前,有关驱动脉冲的参数需由DSP通过三线式串行接口写入时序发生器的相应寄存器组中。通过外接主时钟CLI,AD9995将产生CCD所需的水平及垂直驱动脉冲以及AFE驱动时钟。模拟前端包括暗电流箝位器、双相关采样器、增益放大器和一个12位的A/D转换器。

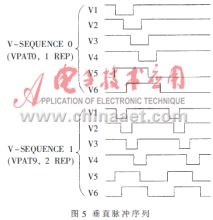

CCD水平驱动脉冲的周期和脉宽是固定不变的,而六相垂直驱动脉冲却是变化多样,每相垂直驱动脉冲的上升沿和下降沿时刻均会有所不同,在这里通过四个步骤设置AD9995中相应的寄存器组来产生CCD所需要的驱动脉冲。第一步通过VPAT0~VPAT9这10个寄存器组产生多至10组不同垂直驱动脉冲组合(如图4所示),每一种组合中的垂直驱动脉冲V1~V6的上升沿和下降沿时刻均可分别定义。等二步在第一步定义的脉冲组合的基础上组成不同垂直脉冲序列V-SEQUENCE(如图5所示)。对应一个垂直脉冲序列选择一组垂直脉冲组合,并定义垂直脉冲组合在垂直脉冲序列中的起始时刻以及重复次数。第三步为一场(FIELD)图像中的不同区域指定相应的垂直脉冲序列(如图6所示)。每一个场图像可以包含多达7个不同的区域(RIGEON);至多可以定义6个不同的图像场。最后通过模式寄存器的设置把不同的场组成图像输出(如图7所示)。在ICX432DQF的帧输出模式中,根据驱动脉冲要求,分别定义5组垂直脉冲组合、5组垂直脉冲序列、3个图像场,最后通过模式寄存器把这些驱动信号整合。

在驱动脉冲的作用下,从CCD输出的像素模拟电压信号由CCDIN引脚输送到AD9995的DIN引脚,经AFE采样、放大和A/D转换后,由DOUT引脚以12位数字量输出。

2.3 DSP及高速图像数据" title="图像数据">图像数据的存储

由于图像的数据量非常巨大,而且要以24MHz的高速率将每一像素的数据输出,所以高速图像数据的实时存储是图像采集系统的关键环节。本系统采用ADI公司新近推出的ADSP-BF533高性能数字信号处理芯片及外接SDRAM存储器来实现图像数据的传输与实时存储。通常为使CCD输出的高速数据流与外部总线接口较低的传输速度相匹配,必须使用FIFO作为数据缓冲器,之后再由DSP读取。然而,利用ADSP_BF533系列DSP芯片中的PPI(Parallel Peripheral Interface)却可以很容易地实现DSP与高速ADC和DAC的无缝连接。通过PPI和DMA的组合使用,可以有效地获取、存储和传输图像数据,大大减少了实时图像处理应用中内核处理器的开销,可编程和可设置性也减少了外部元器件。在系统中,由AD9995并行输出的高速数据送到DSP的PPI,并在直接存储控制器(DMA)的控制下写入SDRAM存储器。

2.3.1 PPI接口功能与原理

ADSP_BF533芯片提供的PPI是一种多功能并行接口,数据线宽度可以在8位~16位之间设置。PPI支持双向数据流,能够与高速A/D转换器、D/A转换器或其它通用外围设备直接并行连接,适合大量数据的高速连续输入与输出。它包括三条同步信号线和一个与外部时钟相连的时钟引脚。在本系统中,PPI时钟由AFE9995的像素输出时钟DCLK驱动,PPI可以在驱动时钟频率高达65MHz的情况下接收数据,所以完全能够满足本系统中CCD 24MHz速率的像素数据传输。根据经A/D转换后的数据宽度设置PPI的数据线宽度为12位,由AD9995输出的水平同步信号HD和垂直同步信号VD分别输入PPI的PPI_FS1和PPI_FS2同步信号引脚(如图8所示)。

从CCD输出的像素信号并不都是有用的,每一行中在有效像元前后都存在一些黑(OPTICAL BLACK)像素,和一些哑(DUMMY)像素,同样在一场有效输出前后也存在着一些哑行,所以由AFE输出的有效图像数据中间有一定的行间隔和场间隔。当HD同步信号输入到PPI的FS1后,需要等待若干时钟周期才开始有效像元数据的传输,这时可通过延迟计数寄存器(PPI_DELAY)来设置需要等待的时钟周期数。另外,还要在PPI_COUNT和PPI_FRAME寄存器中分别设定每一行的像素数和每一场图像的行数,这样便确定了每一次PPI调用中所要传输的数据量。

2.3.2 DMA的调用

在CCD数据采集这种数据量非常大的情况下,PPI 接口只有在DMA引擎的配合下,系统才能发挥它的高效能。虽然对图像数据进行的传输也可由软件实现,但将消耗掉大量的CPU时钟周期,使DSP的高速数据处理能力难以发挥。因为有了DMA独立负责数据传输,在系统内核对DMA初始设置并启动后,便不再需要内核参与,DMA控制器直接把图像数据从PPI接口传输至SDRAM存储器进行存储。于是,在有效地解决了大批量图像数据传输这一速度瓶颈的同时,又能让DSP处理器专心从事算法处理工作,极大地提高了系统的并行性能。

ADSP-BF533的DMA可以控制六种类型的数据传输:内部存储器之间、内部存储器-外部存储器、存储器-SPI接口、存储器-SPORT接口、存储器-UART接口、存储器-PPI接口。本系统使用PPI接口与外部存储器SDRAM之间的DMA传输。DMA的建立需要如下步骤:(1)设置寄存器DMA1_0_START_ADDR_REG,写入目标地址值;(2)设置寄存器DMA1_0_X_COUNT_REG,写入传输次数;(3)设置寄存器DMA1_0_X_MODIFY_REG,写入每次数据传输的目标地址修正值;(4)设置DMA控制寄存器DMA1_0_CONFIG_REG,启动DMA数据传输。

3 系统软件实现

在ADI 公司的DSP集成开发环境Visual DSP++3.0中,采用C语言与汇编语言混合编程的方式进行CCD图像采集的软件开发。系统软件流程图如图9所示。系统初始化之后,调用AD9995设置子程序对AD9995中的众多寄存器组进行设置,使其能够产生所要求的CCD驱动脉冲;之后检查DMA通道是否空闲,若通道忙则等待,若空闲则对PPI和DMA通道的相关寄存器进行设置,并且使能PPI和DMA通道,这样当PPI接口收到HD脉冲后便启动了数据传输。

该CCD图像采集系统采用集成了模拟前端电路与时序发生器的集成元件,从而保证系统具有更高的可靠性和较强的抗干扰能力;通过软件可以方便地改变时序发生器的驱动脉冲,因此适用于多种不同型号的CCD器件,具有较好的通用性。利用PPI和DMA完成数据的传输与存储,改变了通常在高速ADC和DSP之间通过FIFO存储器连接的方式,实现了高速ADC和DSP的无缝连接,简化了系统结构。基于以上特点,本CCD图像采集系统很适合应用于数码相机以及对分辨率要求较高的图像采集与处理场合。

参考文献

1 ADSP-BF533:Embedded Processor Data Sheet. Analog Devices Inc.,2003

2 12-Bit CCD Signal Processor With Precision Timing Generator Data Sheet. Analog Devices Inc.,2003

3 达选福,张伯珩,边川平.高速CCD图像数据存储技术. 光子学报,2003;32(11):1393~1395

4 袁胜春,向健勇, 杜 奇.DSP的DMA通道在高速图像处理系统中的应用.计算机应用,2003;29(12)4~6

5 郭明安,李斌康. 高分辨CCD图像采集系统的实现.电视技术,2003;(6):49~50