片上系统(SoC)需要在单个硅片上实现模/数混合集成。与数字系统工艺兼容、功耗、面积等指标优化的高性能模/数转换器(Analog to Digital Converters,ADC)是片上系统中非常重要的单元,它实现了模拟电路与数字电路之间的联系。流水线结构模/数转换器(Pipelined ADC)是一种研究和应用非常广泛的模/数转换器,其结构本身并非属于基本模/数转换器结构,但在精度、速度及功耗方面相对于其他类型都有很大的改进,是高速高精度领域的主要应用类型之一。本文介绍了流水线A/D转换器的基本原理,并构造了一个三级流水线结构的9位100 MSPS A/D转换器(ADC),采用Zarlink 0.6μm互补双极工艺模型对电路进行了模拟验证。

1 三级流水线A/D转换器电路设计

使用分级技术是解决高速高分辨率的一种方法。可以使用两级或多级高速、低分辨率子ADC组合起来,形成一个高速高分辨率的流水线ADC。

1.1 三级流水线A/D转换器工作原理

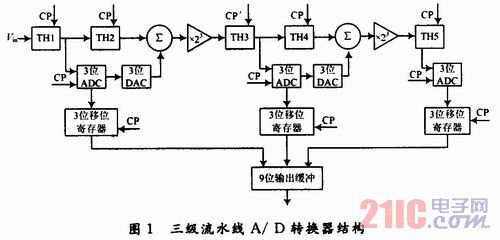

在基本A/D转换结构中,有些具备高速性能,有些具备高精度性能,没有能够同时达到高速高精度的要求。流水线ADC的出现在一定程度上解决了这个难题。流水线结构可以在采样速度和转换精度之间取得较好的平衡。图1是三级流水线ADC的结构。

由图1可知,流水线结构模/数转换器主要是由采样保持器、子ADC、子DAC及减法电路组成。输入模拟信号首先送入第一个采保电路(TH 1),TH1的输出信号输出给第一个的子ADC(ADC1)和第二个采保电路(TH2),ADC1将输入信号转换得到高3位数字信号,该高3位数据通过DAC(DA C1)还原成模拟量,再将该模拟量和TH2的输出一同输入到减法电路,并将差值由放大器放大一定倍数,便得到第一级模拟余量信号。此模拟余量将作为第二级转换电路的输入信号。重复上述步骤,得到次3位转换数据,依此类推。

设输入信号为Vin,Vin通过3位ADC产生的数字量为Dm,3位DAC输一模拟量为Vout,则Vin,Dm和Vout的关系由式(1)、(2)决定。

由式(2)可知,3位DAC还原得到的Vout小于等于输入信号Vin,其差值就是包含低位数据位信息的模拟余量。为了使下一单元的ADC得到满幅输入,以降低对子ADC性能的要求,还需将此模拟余量乘以ADC量化单位的倒数,即将此模拟余量放大23倍后再送给下一级子转换器。

1.2 采样保持电路" title="采样保持电路">采样保持电路的设计与分析

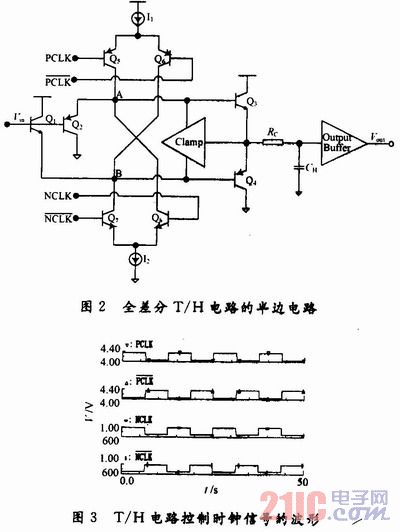

图2为全差分采样保持电路(T/H电路)的半边电路;图3为该T/H电路控制时钟信号。

当PCLK和NCLK信号为低电平时,T/H电路工作在采样模式,Q5,Q7导通" title="导通">导通,Q6,Q8截止,A节点电压升高,B节点电压降低,这时Q1~Q4均导通且工作在正向放大区,它们形成一个AB类缓冲器驱动保持电容CH。该输入电路结构具有输入偏置电流小、输入阻抗高、交调失真小的特点。当PCLK和NCLK信号为高电平时,T/H电路工作在保持模式,Q5,Q7截止,Q6,Q8导通,钳位电路(CLAMP)开始作用,使A节点电压钳位在VCH-VthN,使B结点的电压钳位在VCH+VthP(VthN和Vthp分别表示NPN管和PNP管的BE结导通屯压),也使A,B两节点呈现为低阻抗节点。此时Q1~Q4均截止,故而形成输入信号与保持电容之间的二重隔离,消除保持模式的信号馈通。

RC和CH构成一个低通滤波器,其截止频率会随负载而变化。为克服这一缺点,在输出端设计一个输出缓冲器。采样/保持电路的噪声特性主要来自于Q1~Q4的基极寄生电阻热噪声以及它们的散粒噪声和带宽限制电阻RC热噪声。电路设计时,选用大尺寸的器件来减小基极电阻Rb,使得基极寄生电阻热噪声最小化。将Q3,Q4偏置在较大的静态电流来最小化它们的散粒噪声,同时采样模式动态特性也要求Q3,Q4有大的静态电流,以减小VBE调制的影响。当该T/H电路被偏置在大电流时,它将有大的带宽,因此必须串联电阻RC来限制带宽以滤除高频噪声。大的偏置电流也要在功耗和性能之间进行折衷考虑。

1.3 子ADC的设计与分析

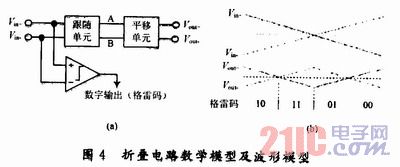

折叠型结构有比较器" title="比较器">比较器数量少、芯片复杂程度低、功耗较小的特点,具有较好的发展前景。将折叠结构ADC应用于流水线(Pipeline)技术中,构成流水线折叠式ADC,则可以提高其工作速度。折叠结构ADC的比较器个数与其分辨率成线性比例关系。1个n位分辨率的折叠结构ADC仅仅需要n个比较器。这不仅减小了芯片面积,而且降低了功耗。折叠单元电路是折叠式ADC的核心模块,其数学模型及波形模型如图4所示。

折叠单元电路工作原理如下;设折叠单元输入电压范围为-VR~+VR,如图4所示,输入信号同时送给跟随单元和比较器,跟随单元实现的功能是使得其输出端A,B分别跟随Vin+,Vin-中较高者和较低者;平移单元将跟随单元的输出电压进行平移,使其达到信号折叠的目的,如图4所示。其输出的电压信号Vout+,Vout-作为下一级折叠单元的输入信号。比较器输出的是格雷码" title="格雷码">格雷码数字输出,由于ADC最终要实现二进制码输出,所以还需要在后续电路中实现格雷码向二进制码的转换。

本文设计的A/D转换器电路采用2级折叠结构的子ADC,产生3位数字信号输出。2组折叠单元具有相同的结构,折叠单元接收差分模拟输入信号,产生1位输出数字信号,同时产生1对差分折叠模拟输出信号输出给下一级折叠单元。图5给出了折叠单元的结构原理,以及它的输入/输出波形。

模拟输入电压VINH,VINL驱动一对互补的射极跟随器(折叠单元),输出一对折叠信号VXH,VXL。VXH,VXL分别跟随VINH,VINL中电压较高的一个和较低的一个,这样就完成了输入信号的折叠。信号的共模电平由平移单元调整,平移单元由平移电阻R1(R2)及跟随器Q1。(Q2)组成,最终得到输出信号VOH,VOL。VINH,VINL还通过折叠单元放大后输入预放大比较器产生格雷码数字信号,并完成格雷码二进制码转换。 A/D转换器的子ADC实现模拟信号量化为格雷码的同时,实现格雷码向二进制码的转换,所以在转换过程中模拟信号必须在格雷码被锁存之前全部被折叠单元处理完毕。这里的折叠单元都是以射极跟随器为基础构成的,所以整个折叠转化过程很快。由于折叠单元的增益为一,模拟信号通过跟随器完成折叠之后振幅减半。

2 三级流水线A/D转换器电路仿真与分析

该转换器采用Zarlink 0.6 μm双多晶互补双极工艺实现。NPN管,PNP管特性频率分别可以达到25 GHz和19 GHz,完全满足电路性能要求。并使用Cadence Spectre电路仿真软件对电路进行仿真验证。

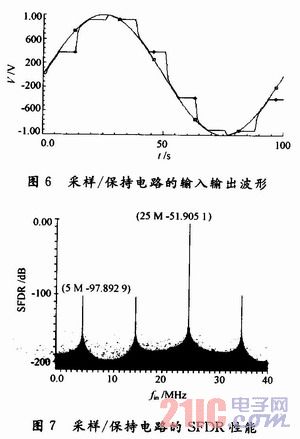

经Spectre仿真验证,T/H电路在-40~+100℃内均能正常工作。图6是典型工艺条件下,输入信号频率为10 MHz、幅度为2 V时,采样/保持电路的输出波形。图6中,在保持阶段保持电压的变化很小,其变化量不大于70μV,故该电路完全满足9位的精度要求。

图7是采样频率为100 MHz,输入信号在幅度为2.2 V、频率为25 MHz情况下,对输出信号做离散傅里叶变换(DFT)得到的频谱图。由图可知,输入信号频率为25 MHz时无杂散动态范围(SFDR)为97.84 dB,完全满足设计要求。

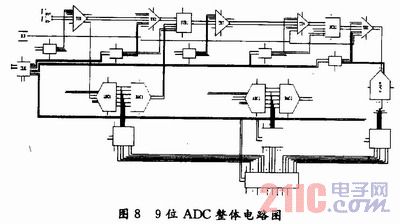

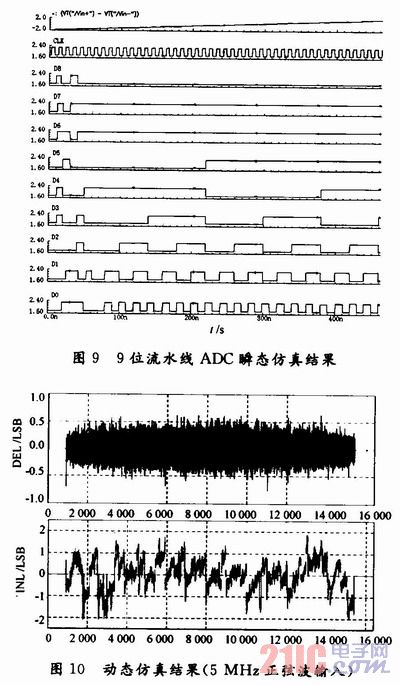

图8是9位100 MSPS三级流水线A/D转换器整体电路图,采样时钟CP频率为100 MHz,输入信号为一个上升的斜波的正弦波,峰峰值为2.2 V。图9和图10分别为A/D转换器的瞬态仿真结果和动态仿真结果。

由仿真结果可以看出,电路具有良好的线性度,在整个输入范围内鲜见误码。典型的DNL为0.7LSB,INL为2.0LSB,满足电路设计要求。

3 结语

本文设计了一个9位100 MHz低功耗流水线A/D转换器电路。该A/D转换器采用开环结构的采样保持电路提高了输入带宽,使用折叠结构子ADC,简化了电路结构,减小了芯片面积和功耗。该ADC有效输入带宽达到100 MHz。在奈奎斯特频率范围内,整个ADC的有效位数始终高于10位。在100 MHz采样频率下,电路的功耗仅为650 mW。