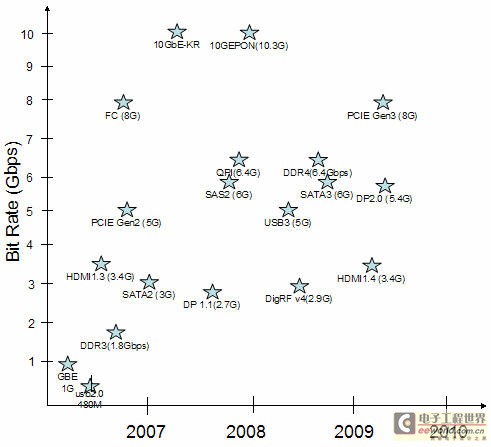

在这篇文章中我们深入讨论一下高速信号中最主要的方面——抖动。在上一篇中我们知道现在数字电路发展的趋势是并行向串行发展,而串行速率也在不断的提高,下图是流行的串行总线发展趋势图:

图:高速串行总线发展趋势

抖动的定义:“信号的某特定时刻从其理想时间位置上的短期偏离为抖动”。

参考: Bell Communications Research, Inc (Bellcore), “Synchrouous Optical Network (SONET) Transport Systems: Common Generic Criteria, TR-253-CORE”, Issue 2, Rev No. 1, December 1997

分析一下抖动的定义,有两个要点:抖动是时间的误差;抖动是实际与理想之间的误差。因此,在测试抖动的时候,我们需要明确这是一个时间量的测试;并且需要找到与之比较的理想信号。

越来越快的数据率意味着承载信息的比特位的时间长度(Unit Interval)会越来越短。对于1Gbps的LVDS信号,100ps Pk-Pk的抖动也许不算什么;但是对于PCIE Gen2.0,100ps pk-pk的抖动意味着会占据一半的UI。而Receiver数据采样点恰好位于50%UI的位置,100ps的抖动对PCIE Gen2是不能接受的。

抖动的类型有很多,不同的定义之间会有很大的差别。通常我们会在“抖动”这个术语前面增加一些限定词:如TIE抖动、cycle-cycle抖动、period jitter等。根据抖动的测试对象不同,我们可以简单的把抖动分为时钟抖动、数据抖动;时钟抖动中可以细分为period jitter、cycle-cycle jitter;数据抖动主要是TIE。

TIE(Time interval Error)顾名思义及时数据信号各个条边沿和理想信号条边沿之间的差异。那么何谓理想的信号呢?我们想象一个数据率为2.5Gbps的理想信号,其一个UI的宽度是数学意义上的400ps;实际的测试值多少会偏离这个理想的情况。在实际的工程应用中,理想的数据都是通过CDR之后的得到的clock来计算的。我们可以回忆一下上一节讨论到的CDR的意义。

图:数据TIE的定义。t1,t2,t3...为TIE样本

我们在实际工作中是怎么测量抖动的呢?Long long ago, there was no jitter analysing software...

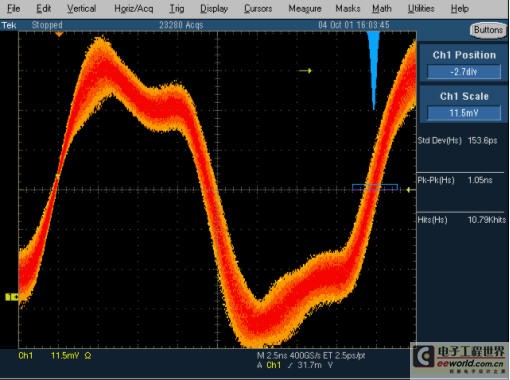

图:利用示波器基本功能进行抖动测试

利用触发将信号稳定在示波器上,测量触发边沿下一个周期的、过参考电平处的信号分布。图上蓝色的图形(直方图)反映了抖动的分布。可以测量直方图的pk-pk,RMS,Mean等等。这种方法简单易行,新老咸宜,既是使用最老信号的Tek示波器都可以做出这样的测试。但是这种测试方法存在的很大的误差,测试的时间越长、积累的波形越多,抖动的pk-pk就会越大。因此,这种测试方法仅仅适合粗略的观测。回顾一下TIE抖动的定义,就会明白这里并没有涉及到理想的信号。

另外一种方法是利用到示波器的内存长度,结合分析软件,对示波器所采集的信号进行抖动测试以及分析。例如Tek提供的DPOJET抖动、眼图和时序测试平台软件,除了能够完成各种类型抖动测试之外,还提供了分析的抖动分析功能。

图:抖动分析

这张树状图是最基本的抖动分析图,将最终系统的误码率分解为两个部分:总抖动和总噪声。在总抖动中,根据引起抖动的不同原因,又将抖动分为随机抖动和确定性抖动。

随机抖动(Random Jitter)在统计上服从高斯分布,其干扰源可能是存在在芯片中成千上万个MOS管中正在的向空穴中移动的电子;或是外在的背景辐射噪声。(最好祈祷随机抖动不要太大,否则很难保证系统误码率指标)

确定性抖动处理起来就好办多了,毕竟他们都是有章可循的。每一种确定性抖动都会对应着固定的干扰源,我们从他们的名字上就能知道他们所代表的含义,不是么?