引言

检测系统的可重构设计是检测技术的发展方向。可重构设计是指利用可重用的软硬件资源,根据不同的应用需求,灵活地改变自身体系结构的设计方法。对于检测系统而言,可重构可以分为软件可重构和硬件可重构。采用硬件可重构技术设计的检测系统具有硬件普适性,通过更换各个硬件模块或配置不同的软件代码,即可实现不同功能的检测,从而减少硬件和软件开发上的投入、缩短产品开发周期。

本文提出了一种基于ARM嵌入式微处理器和复杂可编程逻辑器件( CPLD) 的检测系统硬件可重构设计方法。这种结构检测系统既具有ARM微控制器体积小、集成度高、运算速度快、存储器容量大、功耗低等特点; 又具有CPLD强大的高速逻辑处理能力和方便灵活的动态可重构性,将两者结合起来使用能克服传统检测仪器的不足, 可将许多复杂的实时控制算法硬件化,减轻了MCU的负担,减少逻辑控制芯片的使用, 具有可靠性强、可重用性好性价比高突出优点。

1检测系统的结构

本文设计的可重构检测系统采用ARM芯片为主控制器, CPLD芯片为协处理器配合主控制器工作的结构。

1.1检测系统的总体硬件结构

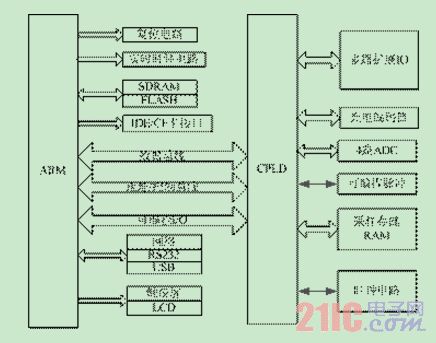

该控制器的硬件结构如图1所示, ARM芯片的外围电路包括复位电路、实时时钟电路、存储模块、海量数据存储模块、通讯模块、LCD接口电路和触摸屏接口电路,。其中存储模块由SDRAM和NOR型FLASH 组成,SDRAM 作为ARM 的内存、存放操作系统和应用程序运行的动态数据, FLASH 存储操作系统镜像文件及一些常量参数;海量存储模块提供了IDE/CF卡接口,可以直接接入硬盘和CF卡作为采样数据的海量存储介质;通讯模块由RS- 232、USB2.0及以太网接口组成,可根据实际情况选择其中一种方式作为通讯接口。CPLD提供模数转换电路控制单元( ADC) 、可编程脉冲产生电路 、采样数据自存储逻辑控制单元、数字量输入输出电路( DI/DO) 、光电编码器输入电路和PWM 波输出电路。ARM与CPLD之间通过并行总线相连。

图1 基于ARM9+CPLD可重构检测系统框图

在上述结构中, 可将CPLD视作ARM的一个高速外设,ARM通过CPLD 间接地操作某些外围器件,充分利用CPLD 的高速逻辑处理能力对整个检测过程实现实时控制, ARM只需负责检测参数的设定和控制检测过程的开始及结束,提高了控制器的实时性,增强了控制器对外设的兼容性和扩展性。

以上系统设计中,我们不仅实现了硬件原理设计上的模块化,可以根据实际需要将各个模块替换成合适的芯片,实现系统的可重构性。在检测仪器的生产、维修和升级等实践中,我们发现将不同模块设计成单板形式,然后通过约定的接口连接起来,方便系统的升级和产品的系列化,也给仪器的维修带来很大便利,同时便于隔离各个模块的相互干扰,提高了系统的抗干扰和稳定性。但是对于一个高速系统,这样的设计必然会带来信号完整性问题。我们将在后面重点介绍这个问题的解决方案。

1.2接口设计

由于ARM与CPLD的总线接口设计是否合理将直接影响着控制器的性能和系统的可重构特性,所以并行总线的设计就成为一个非常关键的问题,该总线包括ARM芯片的地址总线(AB[0..23]) 、数据总线(DB[0..15]) 、控制总线、复位信号以及多路可编程I/O,这样做的好处是,将CPLD芯片存储器化,即ARM可通过对特定地址和I/O口的访问来控制CPLD工作, 并且可通过共同的复位信号将ARM与CPLD 芯片同时复位, 尽量避免总线竞争和冒险现象的出现,CPLD还可通过可编程I/O向ARM发出中断请求,等待ARM对特定事件的处理。这种接口不仅保留了ARM控制平台和CPLD外接单元的独立性,而且接口的通用性也非常好,一般的控制平台和逻辑控制芯片都适用这种接口,这样我们可以根据不同需求,组建合适的系统。

同样CPLD板上的外部接口设计也很重要,直接决定系统可实现的功能和适用程度,我们在CPLD板上留出了4路ADC控制接口,包括采样同步时钟信号、采样数据传输线和多路扩展I/O,可以实现4路AD同时采样,自动存储,并记录采集的起始位置和采样长度,也可以完成对程控放大器、滤波器的控制。考虑到一个系列不同容量的采样存储芯片SRAM一般都会保持引脚的兼容,我们将SRAM设计在CPLD板上,增加系统的稳定性。预留的其它接口我们都尽量保证它的通用性,并在结构设计上考虑各个模块的连接和安装。

2应用实例

超声检测是无损检测的重要方法之一,广泛应用于对钢板、锻件、焊缝、混凝土、人造石墨等进行探伤检验。近年来,超声检测理论和方法都已取得较大进展,但是实践中无论在仪器硬件的实现还是软件的更新上都还存在很多未突破的关键技术。笔者采用以上系统设计了一款一发双收声波检测仪,其检测控制单元位于CPLD 芯片中,ARM芯片通过对CPLD进行存储器访问即可完成对整个检测过程的控制。

2.1芯片选择

ARM 选用内嵌ARM920T核的EP9315微控制器, CPLD选用Alter公司MAX II系列芯片EPM1270。其中, EP9315具有最高可达200MHz的工作频率、16KByte指令缓存、16KByte数据缓存和单/双精度整数及浮点处理能力,还集成了大量适用的外部接口,如IDE接口、USB接口和LCD接口等;EPM1270 型CPLD 含有1270逻辑元件、100多个可用I/O 引脚,每个IO口都可配置成TTL、LVTTL、CMOS、LVCMOS和施密特触发器模式。以上两芯片均为低成本、低功耗芯片。

2.2 CPLD的内部结构设计

在该系统中ARM作为主芯片,负责复杂的数据处理、人机交互、图形显示和接口通信等任务,如何合理设计CPLD外部接口和内部结构,将直接影响到系统的功能和可重构程度。CPLD内部结构如图2所示, 它包括时钟发生器、4个定时计数模块、发射脉冲发生模块、采样时序发生模块、光电编码计数模块和中断产生器, 可进行闭环/开环检测。

图2 CPLD内部结构图

2.3 高速板间设计的信号完整性问题分析

为了使该系统架构具有可重构性,笔者将该系统设计成多PCB结构,以ARM作为主芯片的系统板作为主板,以CPLD为核心的扩展板作为背板,由于这个系统为高速系统,这样的设计必将带来信号完整性问题。其中最主要的是信号长距离传输导致信号质量下降和“地弹”现象的产生。

背板设计必将大大增加信号的传输距离,使得信号的质量受到很大影响,笔者在设计中使用信号线上增加数据缓冲器进行隔离和选择源端电阻匹配等方式,很好的解决了信号的有效传输问题。

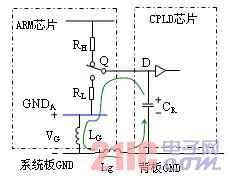

我们根据实际情况建立如下地弹模型图,如图3所示。从图3中可以看出在ARM芯片逻辑门迅速切换的时候,将引起很大的瞬态电流,由于两板之间的电源连接线上的分布电感Lg的存在,将导致严重的“地弹”现象。根据地弹电压

V=Lg×dI/dt

可知,地弹电压与电源连接线上的分布电感和瞬态电流的大小成正比。因此我们对两板之间的电源连接方式作处理,增加回流导线的面积,尽量减小回流导线的长度,使得回流路径上电感尽量小;同时在信号线上增加抑制瞬态电流的电阻,试验结果表明这种设计较好地解决了电源的完整性问题。

图3 地弹模型图

3结束语

本文介绍了一种基于ARM+CPLD 结构的可重构检测平台的设计方法, 并基于此方法开发了一台用于钢板、锻件和基桩等检测的试验样机。此方法以模块化的方式将ARM及CPLD技术巧妙的结合起来,使基于此方法构建的检测仪器兼有ARM 和CPLD两者的优势,实现了部分控制算法的硬件。与传统的基于MCU 的检测设备相比,具有实时性好检测速度高、外围器件少、兼容性和扩展性好等诸多优点;并具有硬件方案的可重构性, 又更方便于客户的应用开发,且成本低。经现场实验验证,该检测设备大大提高现场检测的速度和智能化。由于该设计方案具有极其灵活的可重构性,所以稍加修改扩展就可应用于其他检测系统中去。

本文作者创新点: 提出了一种基于ARM+CPLD结构的可重构检测系统的设计方法。并根据这一方法开发了一款新型声波检测仪,提高了现场测试的自动化程度。