电路功能与优势

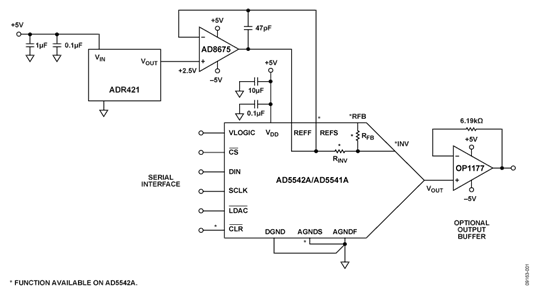

利用电压输出DAC实现真正的16位性能不仅要求选择适当的DAC,而且要求选择适当的配套支持器件。针对精密16数模转换应用,本电路使用AD5542A/AD5541A电压输出DAC、ADR421基准电压源以及用作基准电压缓冲的AD8675 超低失调运算放大器,提供了一款低风险解决方案。

基准电压缓冲对于设计至关重要,因为DAC基准输入的输入阻抗与码高度相关,如果DAC基准电压源未经充分缓冲,将导致线性误差。开环增益高达120 dB的AD8675已经过验证和测试,符合本电路应用关于建立时间、失调电压和低阻抗驱动能力的要求。

需要时,精密、低失调OP1177 可以用作可选的输出缓冲器。

这一器件组合可以提供业界领先的16位分辨率、±1 LSB积分非线性(INL)和±1 LSB微分非线性(DNL),可以确保单调性,并且具有低功耗、小PCB和高性价比等特性。

图1. 精密DAC配置(简化的原理示意图:未显示去耦和所有连接)

电路描述

对于无误差的理想DAC,输出电压与基准电压相关,如下式所示:

其中D为载入DAC寄存器的十进制数据字,N为DAC的分辨率。

对于2.5 V基准电压且N = 16,上述公式可简化为下式:

这样,在中间电平时VOUT为1.25 V,在满量程时为2.5 V。

LSB大小为2.5 V/65,536 = 38.1 μV。

16位时,1 LSB也相当于满量程的0.0015%,或者15 ppm FS。

基准电压源ADR421(B级)的室温初始精度为0.04%,相当于16位时的约27 LSB。此初始误差可以通过系统校准消除。ADR421(B级)的温度系数典型值为1 ppm/°C,最大值为3 ppm/°C。

假设使用理想基准电压源(基准电压误差已通过系统校准消除),则AD5542A的最差情况单极性输出电压(包括误差)可通过下式计算:

其中:

VOUT−UNI为单极性模式最差情况输出。

D为载入DAC的码。

VREF为施加于DAC的基准电压(假设无误差)。

VGE为增益误差,单位伏特(V)。(注意,基准电压缓冲的失调误差必须包括在增益误差中,因此为基准电压缓冲选用的运算放大器必须具有低输入失调电压特性)。

VZSE 为零电平误差(失调误差),单位伏特(V)。(注意,可选输出缓冲放大器的失调电压会增加此误差)

INL为DAC的积分非线性,单位伏特(V)。(注意,可选输出缓冲放大器的非线性会增加此误差)

室温下,此电路的实测零电平误差和增益误差分别为±0.7 LSB和±2 LSB。在整个温度范围内(−40°C至+85°C),零电平误差为±1.5 LSB,增益误差为±3 LSB。这些测量结果是从AD5542A的VOUT直接获得,没有连接输出缓冲器。

本电路采用电压输出DAC AD5542A,提供真16位INL和DNL。AD5541A/AD5542A的DAC架构为分段R-2R电压模式DAC。采用这种配置,输出阻抗与码无关,而基准电压源的输入阻抗则与码高度相关。因此,基准电压缓冲的选择对于码相关基准电流的处理非常重要,如果DAC基准电压缓冲不充分,可能会导致线性误差。选择配合精密电压输出DAC使用的基准电压缓冲时,运算放大器的开环增益、失调电压、失调误差温度系数和电压噪声也是重要的选择指标。基准电压电路中的失调误差会引起DAC输出端产生增益误差。

本电路采用驱动/检测配置(开尔文检测)的AD8675运算放大器作为AD5542A的低阻抗输出基准电压缓冲。AD8675具有120 dB的开环增益,是一款精密、36 V、2.8 nV/√Hz运算放大器。其典型失调电压为10 µV,典型温漂小于0.2 µV/°C,噪声为0.1 µV峰峰值(0 Hz至10 Hz),因而AD8675特别适合那些需要最小误差源的应用。

AD5542A有两种工作模式:缓冲模式和非缓冲模式。使用何种工作模式由具体应用及其建立时间、负载阻抗、噪声等要求而定。可以选择输出缓冲器来优化直流精度或快速建立时间。本电路所用的可选输出放大器为高精度OP1177。DAC的输出阻抗恒定(典型值6.25 kΩ),且与码无关,但为了将增益误差降至最小,输出放大器的输入阻抗应尽可能高。输出放大器还应具有1 MHz或更高的3 dB带宽。输出放大器给系统增加了另一个时间常数,因此会延长输出的建立时间。运算放大器的带宽越宽,则DAC与放大器组合的有效建立时间越短。

图1所示的器件组合实现了最小的PCB面积。AD5542A采用3 mm × 3 mm、16引脚LFCSP或16引脚TSSOP封装。AD5541A采用3 mm × 3 mm、10引脚LFCSP或10引脚MSOP封装。

请注意,AD5541A不包含基准电压和地上的开尔文检测线路、清零功能以及RFB 和 RINV电阻。

AD8675和ADR421采用8引脚MSOP或SOIC封装,OP1177采用8引脚MSOP封装。

可选输出运算放大器为采用单位增益配置的OP1177,它包括一个与反相输入端串联的6.19 kΩ电阻。此电阻用于抵消偏置电流,并与AD5542A的输出电阻相匹配,后者约为6.25 kΩ ± 20%。

测量结果表明,AD5542A/AD5541A是高精度、低噪声电平设置应用的理想选择。在这一高精度、高性能系统中,通过基准电压源ADR421和基准电压缓冲AD8675保持直流性能水平。测量直接在VOUT上进行,没有连接可选的输出缓冲器。

积分非线性和微分非线性测量

积分非线性(INL)误差指实际DAC传递函数与理想传递函数的偏差,用LSB表示。差分非线性(DNL)误差指实际步进大小与1 LSB的理想值之间的差异。图1所示电路提供了16位分辨率,DNL和INL均为±1 LSB。图2和图3显示了该电路的DNL和INL性能。

图2. 微分非线性

图3. 积分非线性

零电平误差和增益误差测量

室温下,零电平误差 (VZSE)和增益误差(VGE) 的测量结果分别为±0.7 LSB和±2 LSB。在整个温度范围内(−40°C至+85°C),零电平误差为±1.5 LSB,增益误差为±3 LSB。

布局考虑

在任何注重精度的电路中,必须仔细考虑电路板上的电源和接地回路布局。包含本电路的印刷电路板(PCB)应将模拟部分与数字部分分离。如果该电路所在系统中有其它器件要求AGND至DGND连接,则只能在一个点上进行连接。该接地点应尽可能靠近AD5542A/AD5541A。本电路应该采用具有较大面积接地层和电源层的多层PCB。有关布局和接地的更多讨论,请参考教程MT-031。

AD5542A/AD5541A的电源应使用10 μF和0.1 μF电容进行旁路。这些电容应尽可能靠近该器件,0.1 μF电容最好正对着该器件右上方。10 μF电容应为钽珠型或陶瓷型电容。0.1 μF电容必须具有低等效串联电阻(ESR)和低等效串联电感(ESL),普通陶瓷型电容通常具有这些特性。

针对内部逻辑开关引起的瞬态电流所导致的高频,该0.1 μF电容可提供低阻抗接地路径。有关正确去耦技术的更多信息,请参考教程MT-101。

电源走线应尽可能宽,以提供低阻抗路径,并减小电源线路上的毛刺效应。时钟和其它快速开关的数字信号应通过数字地将其与电路板上的其它器件屏蔽开。

常见变化

AD8628 是另一款适合用作本电路中基准电压缓冲的优秀运算放大器,它提供低失调电压和超低偏置电流,开环增益为125 dB。ADR421 (2.5 V)可以用ADR423(3.00 V)或ADR434 (4.096 V)代替,二者均为低噪声基准电压源,与ADR421同属一个基准电压源系列。超低噪声基准电压源ADR441和ADR431 也是合适的替代器件,提供2.5 V输出。

AD8661是可选输出缓冲器的另一个不错的选择。它是一款CMOS运算放大器,采用了ADI公司的DigiTrim®专利技术,可实现低失调电压,并具有低输入偏置电流和宽信号带宽等特性。

AD8605或AD8655(均采用+2.7 V至+5.5 V单电源供电)也是可以考虑的选择,不过由于所有轨到轨运算放大器都有的输出级限制,在近0 V输出时具有非线性(参见教程MT-035)。

AD5542A的内置电阻RFB and RINV,可以配合外部运算放大器提供双极性电压输出。(更多信息请参考AD5542A数据手册 。)