0 引言

遥测舱是导弹研制中不可缺少的关键测试部件,它为导弹系统的顺利研制提供了重要保证。为了提高安全性和可靠性,遥测舱产品使用前必须通过检测和调试。遥测舱信号源是根据测试要求向待测产品实时地发送各种激励,以此来模拟导弹遥测舱实际测量到的信号,遥测舱产品会对收到的激励信号做相应的处理,然后从其输出端输出数据,这些数据将被采集到遥测舱内部,通过地面接收系统软件的分析,就可以判断遥测舱产品有无故障。由此可见,信号源是遥测舱检测系统中非常重要的组成部分,本文主要针对此信号源的设计与实现展开论述。

1 设计要求

该信号源需要为遥测舱提供串行图像数据、并行数据、串行RS 422数据、模拟信号,这些信号可单独或者组合输出。模拟信号可输出幅值为-10~+10 V,频率为100~40 kHz的脉冲信号。

目前市场上的信号发生器一般都用来产生较为简单的信号,不能够满足本系统的需求。因此,将针对本系统的特殊要求设计一个可编程的信号源。

2 设计方案

采用数字信号源的设计方法,主要以FPGA可编程芯片为核心,辅以必要的电平转换电路,构成可编程信号源。控制逻辑由FPGA可编程芯片来实现。FPGA通过内部逻辑,主要实现三个功能:产生模拟信号所需的频率基准信号;产生并行数据和图像数据的伴随信号,产生并行数据和串行RS 422数据和串行图像数据。模拟信号由功率放大电路进行幅值调节。数字信号经过接口芯片进行电平转换。

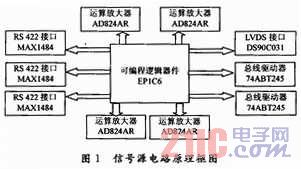

信号源电路板由电源转换模块、可编程逻辑器件、LVDS接口芯片、RS 422接口芯片、运算放大器和总线驱动器等组成。硬件电路原理框图如图1所示。

FPGA采用Altera公司的Cyclone系列EP1C6。Cyclone FPGA是目前市场上性价比最优且价格最低的FPGA。容量为5 980个逻辑单元,具有多达92 160位嵌入RAM。支持各种单端I/O标准如LVTTL,LVCMOS,PCI和SSTL-2/3。FPGA的I/O端口多达185个,可通过VHDL语言编程来自由支配、定义其接口功能,方便PCB版图设计时的布局布线,而且FPGA硬件的速度是纳秒级的,VHDL程序内部对各功能模块的处理是按并行方式进行的,这样既很好地解决了信号通路多的问题,又能实时、快速地传输处理高速数据流。同时,借助EDA工具软件Quartus直接进行代码编写、功能仿真和时序仿真,简单易行地完成硬件功能的验证、添加和修改。配置器件采用Altera公司的串行配置器件EPCS1,工业级低成本,提供在系统编程(ISP)和多次编程能力,这种能力是一次性可编程器件所不具备的,但其成本甚至低于一次性可编程器件,是Cyclone系列器件最完美的补充。存储容量的范围为1 Mb,使其更容易配合FPGA构造所需的最佳解决方案。

3 设计与实现

3.1 串行图像数据

整帧传输时间为10 ms(包括帧头和所有有效数据位);在每帧数据开始发送时,先发送两个帧头校验字FAF3EB90,其中每个字宽度不大于200 ns(校验字每帧发送一次,所以每组校验字之间间距为10 ms),然后再发送16 384(128行,128列)个字的原始图像数据,每个数据字宽度同样不大于200 ns,字的内容为0000~4000循环发送;原始图像数据发送完毕后,还需发送256个字的数字量,前两个字为校验字050C146 F,202个字为有效数字量信息,字的内容为0100~0000循环发送,其余信息字填零。

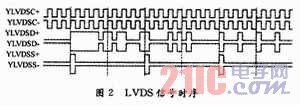

信号时序图见图2。

YLVDSD:发送16位数据,传送系统给图像采集设备的所有数据,每个数据位宽度与时钟的半个周期等宽;

YLVDSS:发送同步信号,每字同步,与首数据最高位同时发出,宽度为半个时钟;

YLVDSC:时钟信号,始终保持。

所有的数据以行时间为基准,即每62.5μs发送一组128个数据(以同步信号为基准计数)。共发送130行,其中正程128行发送图像数据,逆程两行发送信息字。

采用VHDL语言编写程序,使FPGA输出固定时序的LVTTL电平的3路信号,经过一片LVDS接口芯片后,转为LVDS信号。

LVDS接口芯片采用National Semiconductor公司的DS90C031,它是四路LVDS线驱动器,单电源5 V供电。

3.2 并行数据

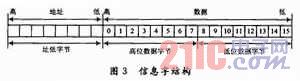

并行数据是以信息帧的形式沿字节多路转换通道发送。信息更新周期为10 ms,每个更新周期传送128个信息字。这些信息字分成2个子帧,每帧64个字,每5 ms发送一子帧。信息字为24位,包括8位地址、16位数据,这样,并行数据的数字遥测信息速率为307.2 Kb/s。

并行数据的数字遥测信息字的结构如图3所示。

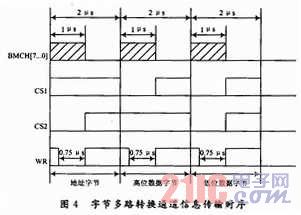

并行数据采用8位并行传输,每个信息字的三个字节分三次沿8位总线分时发送。伴随信号CS1,CS2的不同组合构成地址字节、高位数据字节和低位数据字节的区分标志,信号WR表明信息的发送。地址按00~7F循环发送,数据按0000~9FFF循环发送,8位总线信号、伴随信号和写信号传输均由245作驱动,由这些信号的信号线电压的变化形式表示的信息传输时序如图4所示。

从图4可以看出,一个信息字节的传输时间是2μs,一个信息字的传输时间是6μs。相邻两个信息字之间的间隔时间是10μs。

并行数据信息在5 ms周期内完成后发送,每个周期发送信息的时间大约为640μs。

采用VHDL语言编写程序,使FPGA输出固定时序的LVTTL电平的3路信号,经过2片总线驱动器后,转为TTL电平的并行数据信号。

3.3 串行RS 422数据

串行RS 422数据共有3路。通过FPGA的VHDL程序产生符合RS 422协议的LVTTL电平数据,经过RS 422接口芯片进行电平转换。

RS 422接口芯片采用Maxim公司的MAX1484,它是1收1发驱动器,全双工。

(1)第一路DF422

波特率为500 Kb/s,每帧2.5 ms,帧长9个字节。

(2)第二路ZW422

波特率为240 Kb/s,每帧1 ms,帧长12个字,8 b/字。

数据格式是:

1位起始位+8位数据+1位停止位+10位空闲位其中:8位数据是低位在前,高位在后。

(3)第三路YX422

波特率为200 Kb/s,消息块更新频率为400 Hz,每个消息块6个字,每字11位:

1位起始位+8位数据+1位奇偶校验位+1位停止位

3.4 模拟信号

通过对48 MHz的外部时钟分频产生固定频率的脉冲方波,幅度为0~3.3 V,采用高速运算放大器产生线性比例放大电路对幅度进行调节。

运算放大器采用AD公司的AD824,支持单电源供电,是低功耗的场效应晶体管输入操作放大器。

3.5 电路设计

在设计中采取了多种措施以保证信号源在各种情况下的正常工作。

(1)采用4层PCB板设计,避免使用过多分立器件,减小设备体积,缩短引线,提高可靠性;

(2)电源和器件电源管脚加滤波电容,减小电源噪声对器件和电路板的影响;

(3)印制板合理布局、布线,减小各种信号间的相互干扰;

(4)差分信号线d+和d-到接口不超过30 mm,两信号线长度差控制在2 mm以内,确保满足LVDS数据传输带宽的要求;

(5)电路设计中,采取措施尽量提高系统对各种干扰的隔离以及突发大信号的抑制,保护系统可靠工作。输出电路串接保护电阻,在输出短路时确保电路完好。

4 结论

综上所述,主要介绍了遥测舱多路可编程信号源的设计与实现,着重对设计中的几个关键技术做了较为详细的研究论证。通过采用FPGA作为设计核心,编写VHDL程序产生主要逻辑功能,附加外围电平转换芯片实现各种类型信号输出。实践证明,此信号源完全能够模拟遥测舱测量到的信号,符合设计要求。