摘要:分析了数字信号处理器TMS320C6416和CAN控制器SJAl000的接口时序。给出了基于复杂可编程逻辑器件EPM7512的DSP数字信号处理器和CAN控制器之间的接口电路,同时给出了详细的软硬件实现方法。

关键词:TMS320C6416;SJAl000;CPLD;接口电路

O 引言

CAN总线是现场总线中的一个应用热点,可支持分布式控制和适时控制的串行通信网络。由于CAN总线具有通信速率高、开放性好、报文

短、纠错能力强以及控制简单、扩展能力强、系统成本低等特点,因而其应用越来越受到人们的关注。基于CAN总线的CAN控制器具有完成CAN

总线通信协议所要求的全部必要功能,因此,CAN控制器与其它微处理器的接口已成为设计CAN总线系统的首要工作。目前已有一些微处理器将CAN控制器嵌入到系统之中,但是,仍有大量人们比较熟悉的微处理器并不带有CAN控制器。为此,本文介绍了CAN控制器SJAl000与DSP芯片TMS320C6416的接口电路。

SJAl000是符合CAN2.0B标准的CAN通信控制器,该器件具有完成高性能通信协议所要求的全部特性,同时具有下列特性:

◇可连接各种微控制器接口;

◇取决于报文标志符的总线访问优先权;

◇强有力的错误处理能力;

◇可组态总线接口;

◇带有位填充功能的非归零编码/解码;

◇输出驱动器状态可编程。

TMS320C6416是一款高性能DSP数字信号处理器。它基于C64x核心架构,并集成了丰富的外围设备和接口,最高主频可达到1.0GHz。TM-S320C6416以高速的处理能力和出色的接口能力,已广泛用于当今技术的各个领域。

1 TMS320C6416与SJAlOOO的接口设计

1.1 INTEL方式下SJAl000的读写时序

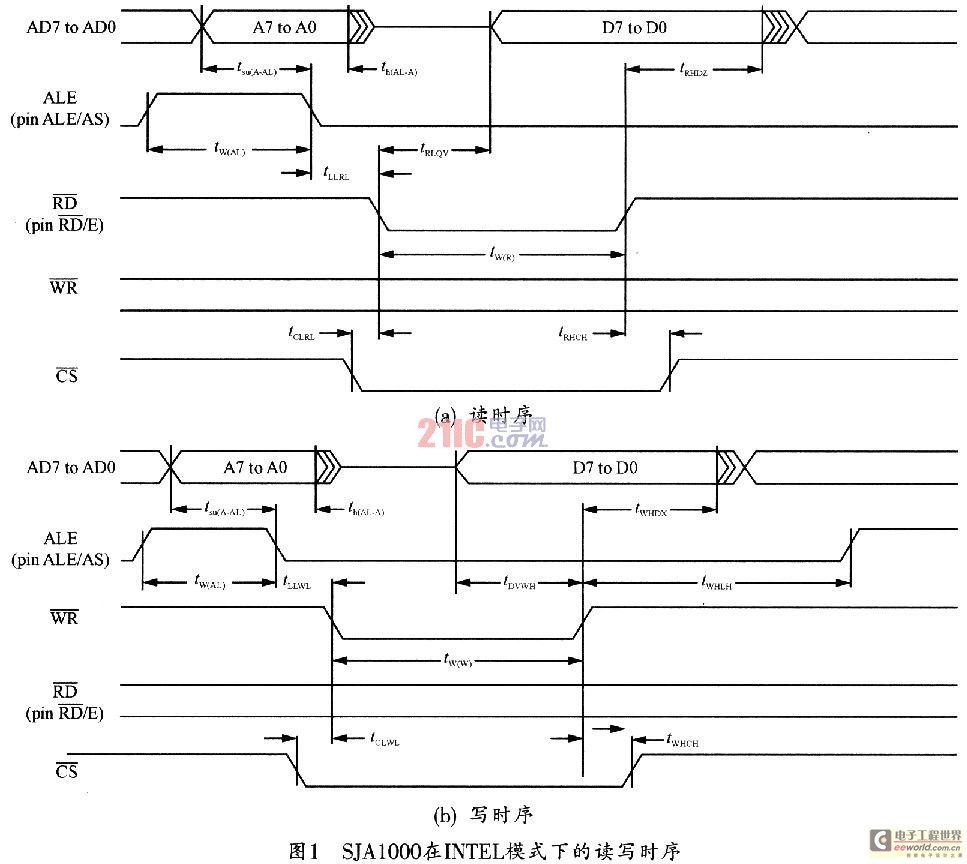

INTEL方式下,SJAl000的读、写时序图如图1所示。

在INTEL方式下读写SJAl000时,其地址和数据是分时传送的,地址在前,数据在后。ALE为高时,为地址总线周期;ALE为低电平,同时

也为低时,为数据总线周期。为低时,为读数据;为低时,为写数据。

1.2 TMS320C6416的读写时序

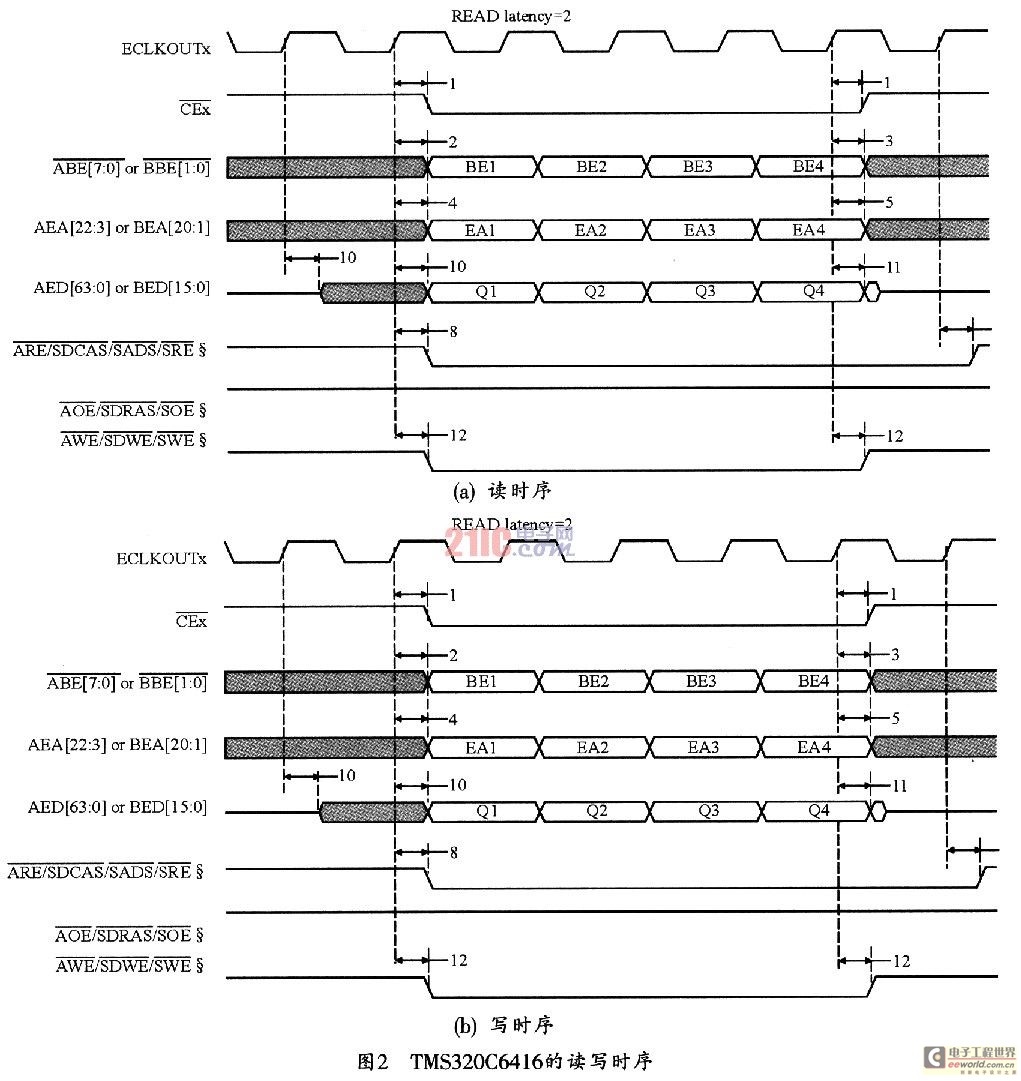

数字信号处理器TMS320C6416的读写时序如图2所示。

TMS320C6416的数据线和地址线是分开的,而SJAl000的数据线和地址线是复用的。所以TMS320C6416不能与SJAl000直接对连,而必须将数据和地址线进行转换后才能连接。

1.3 TMS320C6416与SJAl000的接口设计

TMS320C6416的数据总线和地址总线是分开的。在对存储器操作时,地址和数据几乎是同时出现的,而且系统采用流水线工作方式,TMS-320C6416的地址和数据总线是无法与SJAl000的AD0~AD7直接连接的,也没有方法可以将SJAl000的RAM直接映射到TMS320C6416的存储器中。因此,为了实现TMS320C6416与SJAl000的接口,应将SJAl000的ALE和直接映射为TMS320C6416的两个I/O端口。可将SJA1000的ADO~AD7直接和TMS320C6416的BED0~BED7连接。当ALE为高电平时,TMS320C6416的BED0~BED7送数据给SJAl000,表示地址值;当ALE为低电平,而且也为低电平时,TMS320C6416的BED0~BED7则和SJAl000交换数据。在这种方法中,可以利用ALE为高电平和为低电平来区分地址总线周期和数据总线周期。

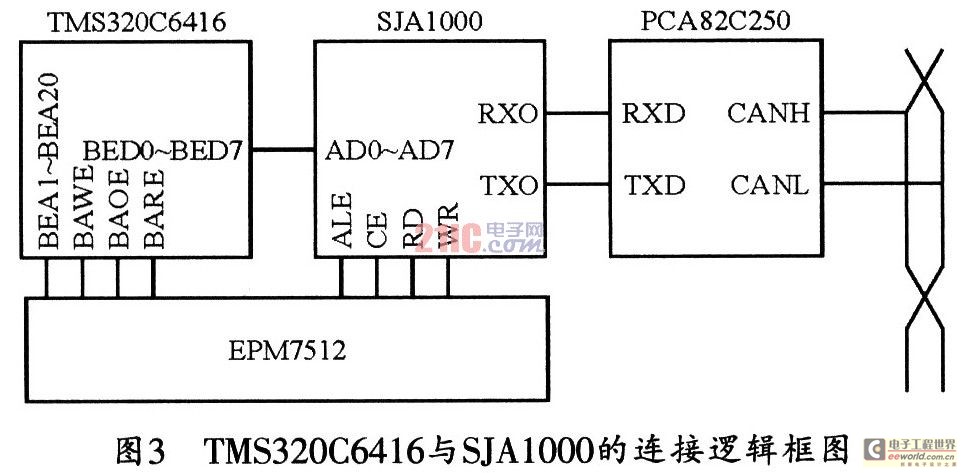

图3所示是其硬件连接方法。

图3中的PCA82C250为CAN串行链接I/O器件。CPLD芯片EPM7512用于产生相应的控制信号并输出给SJAl000,从而控制SJAl00O的地址和数据总线周期。

2 基于EPM7512的接口逻辑

EPM7512是AIZERA公司生产的复杂可编程逻辑器件(CPLD),可与AIXERA公司的QuartusII开发系统软件配合,并可以100%地模仿TTL。采用EPM7512作为DSP的外部接口扩展,可非常方便而且灵活地实现接口功能。

DSP处理器的地址线BEAl5经CPLD产生片选信号后,可由地址线BEA15作为CAN控制器的地址和数据选择线,并和一起产生SJAl000的地址锁存信号ALE。BEAl5为l时,地址有效;BEAl5为0时,数据有效。

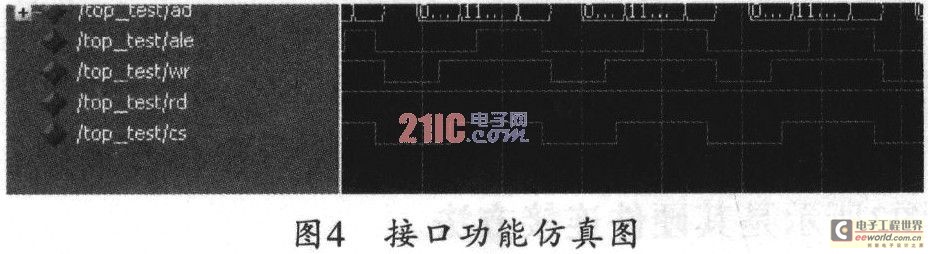

采用ModelSim仿真软件可对接口电路进行功能仿真,其仿真结果如图4所示,能够满足SJAl000的读写时序要求。

3 接口电路的软件读写操作

CAN控制器SJAl000的地址线和数据线可映射为DSP芯片TMS320C6416的外部程序存储EMIFB的CE3区域,其在DSP控制器上的地址分别为0x6-C008000和0x6C000001。其用C语言编程的实现代码如下:

#defineTXB 16

#define RXB 16

(char*) CANAS= (char*) 0x6c008000;//定义CAN控制器数据线

(char*) CANCS=(char*)0x6c000001;//定义CAN控制器地址线

//以下两句为SJAl000的控制寄存器MOD(PeliCAN模式下地址0)赋值Ox09;

*CANAS=0;//提供CAN控制器寄存器地址

*CANCS=0x09;//提供CAN控制器寄存器数据

//以下两句从SJAl000的状态寄存器SR (PeliCAN模式下基地址+2)读取数据;

*CANAS=2;//提供CAN控制器寄存器地址

*SR=CANCS&0xoff;//读取CAN控制器数据。

4 结束语

本文提供了一种基于CPLD的DSP处理器TMS320C6416和CAN控制器SJAl000接口方法,该实现方法比传统硬件逻辑门电路的实现方法更加方便灵活。通过对该方法的软硬件实现进行的仿真结果证明,该设计可以稳定可靠的运行。