PSD813F1及其接口编程技术

2009-02-03

作者:胡国鹏 武自芳

摘 要:介绍了PSD813F1芯片的性能特点及内部结构,结合数据采集设备进解了PSD813F1与80C196KC组成的测量系统的实现方法。

关键词: PSD单片机可编程外围芯片 微控制器 JTAG 数据采集

由WSI公司研制的新一代可编程微控制器系统外围器件PSD813F1芯片,具备完整的在系统可编程(In System Programmable)特性。其在系统可编程不仅仅是对程序存储器而言,而是指整个芯片内的所有功能块的配置,而且可对器件的逻辑和功能进行随时组态或重组。该芯片采用模块化设计技术,可集成一个单片机应用系统所需的多个外围模块,如将FLASH MEM、EEPROM、SRAM、PLD等集成到单一硅片上,为简化微控制器应用系统的设计、缩短产品的开发周期、提高系统的可靠性、降低系统的成本、缩小产品尺寸、增强系统保密性提供了一条捷径。

1 PSD813F1芯片的性能特点

PSD813F1的内部结构如图1所示。

PSD813F1内部集成了可分区段保护的128K字节FLASH MEM(闪速存储器)和32K字节EEPROM,以及掉电时通过切换到备用电源以保持数据的2K字节SRAM。每一个存储器块可以被用户通过配置定位在不同地址空间。FLASH MEM分成8个大小相同的块,EEPROM分成4个大小相同的块,以上各块均可被设定成程序空间或数据空间;2K字节的SRAM存储器可完成数据缓存的功能。

PSD813F1具有可与微控制器相匹配的总线接口逻辑,片内还集成了优化的“宏单元”逻辑结构,包括24个输入宏单元和16个输出宏单元。这些宏单元,既可作为内部PLD阵列的一个组合逻辑输入信号,又可用来完成寄存输出,以完成一定的时序要求。其中输入宏单元可将来自引脚的输入信号经锁存、寄存后或直接传至内部PLD阵列的输入总线。而输出宏单元既可作为一个内部节点反馈至PLD的输入总线,也可直接通过引脚输出。

芯片包括4个可编程I/O端口,共27个允许独立配置的端口引脚,端口A、B和C为8位,端口D为3位,端口可设置为MCU I/O、PLD I/O、外设I/O、地址输入输出、数据端口等不同的配置,而且其中的16个I/O引脚可以设定为CMOS电平或漏极开路工作方式。这些端口的工作方式由数据输入、数据输出、方向、控制、驱动选择等寄存器决定,这些寄存器位于以CSIOP为基地址的256字节空间里,CSIOP基地址由配置软件决定,不同寄存器具有唯一的相对于CSIOP基地址的偏移地址,对寄存器的操作可在程序中完成。

PSD813F1的译码逻辑由内部FLASH PLD(包括FDPLD和FGPLD)实现,具体结构由与阵列组成。FDPLD为内部功能部件提供地址译码,例如内部的FLASH MEM、EEPROM、SRAM、寄存器,以及I/O端口的选择。FGPLD用于实现系统逻辑,如状态机功能块和组合逻辑的实现。

PSD813F1的加密技术为系统的加密提供了便捷的实现方法,当PSD配置寄存器中的保密位被置位时,不允许在器件编程器或通过JTAG端口读器件,当使用JTAG端口时,只有全芯片擦除命令允许,其他命令被阻断。

2 JTAG编程

PSD813F1为真正的现场可编程器件,包括芯片的PSD配置、PLD阵列、EEPROM和FLASH MEM均能在系统中编程。

基于PSD技术的硬件设计方法是采用硬件描述语言来设计复杂的数字逻辑系统,生成符合PSD芯片要求、在电路上可行的数字逻辑,通过WSI公司提供的PSDSOFT软件包,可生成编程器所需的目标文件(包括程序及系统配置文件),经JTAG接口可下载到芯片中。

端口C是可复用的端口,可配置成JTAG编程端口,在现场对空白器件进行在系统编程或对已编程器件进行重新编程,而无需使用微控制器。另外,也可以通过微控制器执行来自EEPROM的编程算法,FLASH MEM也可在系统内被编程。通过执行来自FLASH MEM的算法,EEPROM也可用同样的方法进行编程。PLD逻辑或其他PSD813F1配置同样也可通过JTAG口或器件编程器编程。

PSD813F1遵守IEEE1149.1 JTAG(Joint Test Action Group联合测试行动小组)技术规范的基本内容,支持JTAT接口的ISC(In System Configurition在系统配置)规范,允许PSD813F1与其他工作于边界扫描方式的器件一起存在于JTAG链中,但不支持该技术规范内定义的边界扫描功能。

标准JTAG采用4个基本信号:TCK,TMS,TDI,TDO。其中,TCK为同步时钟,TMS为JTAG方式选择,TDI、TDO分别为串行数据输入和串行数据输出。WSI公司的JTAG接口除以上4个基本信号外,还附加提供了用于增强功能的TSTAT和/TERR信号,其中TSTAT代表正在进行的当前动作的瞬时状态,/TERR指示对字节或扇区的编程/擦除是否超时。此外的附加信号为:/JEN提供低电平有效的使能输入信号,以便使PSD813F1的JTAG功能在端口C引脚上有效;

/RST复位目标系统,/TRST复位目标板上的JTAG,CNTL是由用户定义的信号。

3 PSD813F1在数据采集系统中的应用

PSD813F1可与8位或16位MCU构成一应用系统,本文在此介绍了采用PSD813F1与80C196KC[2]构成的现场数据采集电路。

3.1 硬件结构

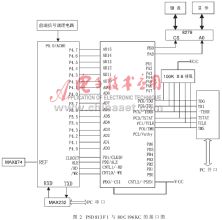

系统硬件结构如图2所示,核心器件为80C196KC和PSD813F1,图中简化了复位等电路。

80C196KC为INTEL公司16位单片机。该单片机具有16位多路复用的地址/数据总线,工作于12MHz的时钟频率,系统主体程序采用C96语言设计,程序空间大小占用32K,系统设计要求采用非易失性存储器进行数据存储,另外需外扩SRAM用于数据缓存。程序存储、数据存储和数据缓存分别由PSD813F1的FLASH MEM、EEPROM和SRAM完成。

A/D转换采用80C196KC自身的10位8路逐次比较型A/D,键盘/显示接口芯片采用8279,与PC机通信采用MAXIM公司的MAX232用于RS-232通信,由MAX874经精密调整后给80C196KC提供4.096V电压。8279的片选和地址译码由PSD813F1的FGPLD完成。

3.2 软件设计

3.2.1 PSD813F1配置文件设计

该电路在PSDSOFT(WSI公司提供的下载软件)中的配置为:

·多路复用工作方式

·ALE高电平有效

·读/写控制选择RD/WR

PSD813F1以ABEL语言为硬件描述语言,在本电路中的设计方法为:

(1)内部译码实现:

fs0=!a15*!a14*!a13*!a12; /*fs为设计中FLASH MEM的保留名fs0地址空间为0000h~0fffh*/

fs1=!a15*!a14*!a13*a12; /*fs1地址空间为1000h-->1fffh*/

fs2=!a15*!a14*a13*!a12; /*fs2地址空间为2000h-->2fffh*/

fs3=!a15*!a14*a13*a12; /*fs3地址空间为3000h-->3fffh*/

ees0=!a15*a14*!a13*a12; /*ees为EEPROM的保留名,ees0地址空间为4000h-->4fffh*/

ees1=!a15*a14*a13*!a12; /*ees1地址空间为5000h-->5fffh*/

ees2=!a15*a14*a13*!a12; /*ees2地址空间为6000h-->6fffh*/

ees3=!a15*a14*a13*a12;/*ees3地址空间为7000h-->7fffh*/

rs0=a15*!a14*!a13*!a12*!a11*!a10; /*rs为SRAM的保留名,地址空间为8000-83fffh*/

csiop=a15*!a14*!a13*a12;/*csiop基地址为9000h*/

(2) 外部译码的实现:

将PB的最低位端口设计为片选信号的设计方法为

cs1 pin7; /*PB的0端口*/

cs1=!(a15 *a14*/a13*a12); /*8279的地址空间为d000h-->dfffh*/

3.2.2 程序设计

程序设计语言为C96,其实现如下:

对SRAM的操作为:

static const unsigned char *pointer_sram=0x8000; /*设置SRAM数据单元的基址指针*/

pointer_sram=0xaa; /*将数据写入基址单元*/

pointer_sram[1]=0xbb; /*将数据写入下一地址单元*/

……

对EEPROM的操作为:

static const unsigned char *pointer_ee=0x4000;/*设置EEPROM空间的基址指针*/

pointer_ee=0xaa;

…… /*延时等待,对EEPROM的单元写入数据时必须增添一定的时间延时*/

pointer_ee[i]=0xbb; /*i为地址增量,即相对于基地址的偏移量*/

……

端口A、B的地址及各控制寄存器的地址由CSIOP的基地址加偏移地址来决定,本设计中PA.0用于为8279的A0提供地址信号。如不采用PSD813F1,则需在80C196KC和8279之间接74373用于地址锁存输出,采用PSD813F1则只需配置端口A的PA.0工作于地址锁存工作方式,配置由A口的控制寄存器(占据一字节空间)决定,实现方法如下:

static const unsigned char *csiop=0x9000;

csiop[2]=0xfe; /*端口A的控制寄存器相对于CSIOP基地址的偏移地址为02H;此时PA.0在控制寄存器中的相应位为0,因此PA.0工作于地址锁存输出方式,其他高7位相应位为1,因此工作于MCU I/O方式*/

对8279的初始化操作为:

static const unsigned char *pointer_8279=0xd000h;/*基址为数据口地址*/

pointer_8279[1]=0xd1;/*对命令端口写入清除命令*/

do{}

while((pointer_8279[1]‖0x7f==0x7f);/*等待清除完成*/

pointer 8279[1]=0x2a; /*送程序时钟分频常数*/pointer_8279[1]=0x08; /*写键盘/显示器工作方式命令*/

pointer_8279[1]=0x90; /*写显示RAM命令*/

pointer_8279=0x10;/*向数据口送入显示数据0x10*/

总之,本文通过设计该数据采集系统,表明PSD813F1芯片集FLASH MEM、EERPOM、SRAM、PLD等于一体,可代替电路设计中的程序存储、数据存储、数据缓存和译码等芯片,从而可使单片机系统大大简化,一个实用系统可简化为“两片”系统,而其JTAG技术更是为该芯片的使用增添了便捷的设计和使用手段。

参考文献

1 PSD8XXF系列数据手册及应用笔记.武汉:武汉力源1998

2 孙涵芳.INTEL 16位单片机.北京:北京航空航天大学出版社