摘要:针对目前高速电路发展带来的信号完整性问题,在分析信号完整性要求的基础上,借助HyperLynx仿真软件,通过器件IBIS模型,对基于EP2C8和TMS320F2812组成的系统进行信号完整性分析和仿真。基于反射原理来介绍减少反射的端接方法,利用大量的板前和板后仿真对设计方案进行反复验证。研究结果表明,HyperLynx可以解决该系统信号完整性方面存在的诸多问题,仿真结果给实际工程提供了借鉴。

关键词:信号完整性;可编程逻辑器件;HyperLynx;IBIS模型

0 引言

随着高速电路的不断发展,时钟频率早已进入吉赫兹时代,电路板尺寸的减小、设备集成度的提高,使得信号完整性问题变得越来越重要。当时钟频率超过100 MHz时,如果不满足系统的信号完整性要求,可能导致系统工作不稳定,同时也会带来EMC问题。随着FPGA和DSP处理速度的提高,带来的信号完整性问题日益严重,这需要电子工程师重点考虑。

目前,有很大一部分文章从理论上分析信号完整性,而从实际应用方面分析的文章较少。基于此,本文主要研究通过对EP2C8和TMS320F2 812组成的系统所涉及的仿真问题进行了分析和研究,通过对关键信号线的仿真来分析系统的信号完整性。

1 HyperLynx软件

HyperLynx是Mentor Graphics公司推出的高速仿真工具,从内容上可分为信号完整性仿真(SI)、电源完整性仿真(PI)和电磁兼容性仿真(EMC);从结构上可分为板前仿真(LineSim)和板后仿真(BoardSim)。为了保证PCB设计的成功率,在设计前遵守一些良好的设计规则很重要。HyperLynx软件则提供了一个验证设计方法和检测PCB性能的环境,这将会提高工作效率。

2 面向系统的信号完整性仿真分析

2.1 系统构成和关键信号

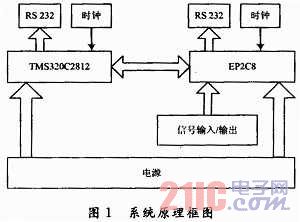

TMS320F2812和EP2C8构成的系统原理框图如图1所示。

由于系统信号线众多,如果全部对它们进行仿真,将会花费很大的时间,只需对茨键信号仿真。根据器件上升沿、工作频率、走线长度、时钟信号等作为划分关键信号的条件。明确了高速信号有TMS320F2812和EP2C8的通信端口、时钟网络、EP2C8数据接收端等。这些高速信号易受干扰同时又容易干扰其他网络,需要着重考虑这些信号线的设计。通过HyperLynx的仿真可以优化这些走线,找到合适的设计方法。

2.2 系统板层设计

在对系统仿真前,需要确定PCB叠层数、走线特性阻抗等,这是系统进行信号完整性仿真的基础。对于微带线,IPC推荐的特性阻抗近似式为:

![]()

式中:h是导线离参考层的距离;w是导线宽度;t是导线厚度;由上式可知当w=2h时,走线特性阻抗为50 Ω,这可以作为经验公式。该系统采用4层电路板,相对介电常数εr为4.3的FR4材料,走线特性阻抗设定为50 Ω,PCB板的厚度是1 mm,具体叠层方案如图2所示。

3 LineSim仿真

LineSim可以在布局布线前对所设计的方案进行仿真,将仿真的结果作为实际布线的约束条件,在初期预测和消除信号完整性问题。

3.1 高速信号线端接仿真

信号反射的原因是信号沿导线传播所受到的瞬态阻抗发生变化时,则一部分信号将被反射,另一部分发生失真并继续传播下去,这将导致波形的边沿处发生振铃现象。一般要求过冲幅值限定在150 mV左右,否则会造成EMC问题。典型的端接方式包括:源端串联端接;远端并联端接;远端戴维南端接;远端RC端接。其中源端串联端接使用器件少并且效果好,因此该系统采用源端串联端接方案。

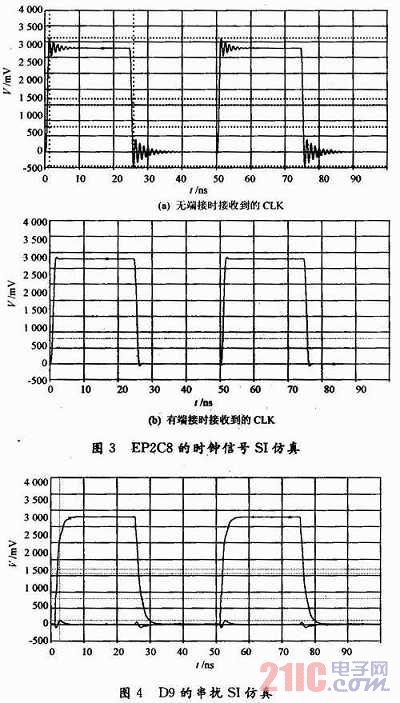

由于EP2C8采用20 MHz独立的有源时钟,因此在仿真时只需考虑EP2C8的CLK。若将有源晶振的输出直接和EP2C8相连,则LineSim仿真的结果如图3(a)所示,信号边沿处有振铃现象,电压过冲幅值3.629 V,下冲值为-450.2 mV,超过了过冲幅值范围。当采用一个阻值为50 Ω源端串联电阻时,SI仿真的结果如图3(b)所示,接收端接收到的时钟信号在跳变处无振铃现象,抑制信号反射的效果很好。

串扰是信号完整性问题之一,它是指有害信号从一个网络转移到相邻网络。串扰可分为近端串扰(NEXT)和远端串扰(FEXT),传输线的反射跟串扰也有联系,采用合适的源端端接和远端端接可以在一定程度上减小串扰。但串扰与信号之间的容性耦合和感性耦合有关,串扰不可能完全消除,只能减小。在TMS320F2812和EP2C8之间有大量的高速数据线,如果不进行处理则有可能接收错误的数据。图4所示为用LineSim对数据线D8,D9和D10进行SI仿真的结果,设定D9是被干扰的网络,D8、D10是攻击网络,振荡频率为20 MHz,端接电阻为50 Ω。从图可知D9受到的干扰较小,过冲电压只有122 mV。如果想要进一步减小串扰则可以减小走线宽度到8 mil,同时缩短走线耦合长度。

3.2 高速信号线时序问题

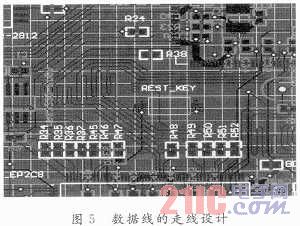

TMS320F2812和EP2C8之间数据收发率高,因此时序就变得十分重要,如果两信号到达接收端的时差近似于一个采集周期将导致接收到错误的数据。为了避免这种时序可题的发生,通过蛇形线来保证高速信号走线长度的一致,如图5所示。PCB设计的工具是Altium公司的DXP 2004。

4 BoardSim仿真

BoardSim是在PCB绘制完成后进行的仿真,生成整版报告,验证原有设计的合理性、修正布局布线。仿真将利用器件的IBIS模型对已经设计好的PCB走线进行仿真,包括信号完整性、EMC、时序等。

4.1 串扰仿真验证

第3.1节中已经对D8,D9和D10进行了串扰仿真,现在用BoardSim来验证上述仿真结果。考虑到实际电阻值没有50 Ω,所以采用端接电阻值为51 Ω,振荡频率为20 MHz。图6所示为当D8,D10有数据通信时D9受到的干扰。由图可知,D9处的波形抖动很小,串扰电压过冲只有44.8 mV,下冲电压只有-39.8 mV,基本上不会影响D9的信号,结果表明已经通过信号完整性检查。

4.2 端接仿真验证

主要验证时钟信号和数据线的端接方案的合理性。

4.2.1 时钟信号的端接

时钟信号网络标号为CLKIN,端接电阻阻值是51 Ω,SI仿真的结果如图7所示,可见BoardSim仿真与在LineSim中的仿真相差无几,满足SI要求。

4.2.2 数据线的端接

虽然用蛇行线可以解决信号的时序问题,但要注意的是蛇形线对信号完整性有一定影响。蛇行线的间距越小、耦合长度越长,则信号的串扰也越大,因此设计时需要注意这一点。表1是EP2C8与TMS320F2812之间的D0~D15这16根数据线长度,最短的网络是D14只有2.661inch,最长的是D7有2.856 inch,长度变化控制在(2.76±0.1)inch之内。SI仿真结果见表2。

表2为BoardSim对数据线SI批量仿真结果。从中发现16根数据线的上升和下降沿的具体时延基本相当,说明通过正确端接和等长线保证了信号接收端的质量和时延等要求。接着对这几根数据线进行批量的EMC仿真,仿真设定的标准是FCC和CISPR,结果为Net's EMCis within selected limits,可知系统满足EMC要求。

5 结语

本文利用HyperLyn软件和元器件的IBIS模型对TMS320F2812和EP2C8系统进行了信号完整性仿真分析。通过分析可知,合适的端接电阻可以大大减小信号在导线上的反射和串扰。采用蛇形线的走线方案解决了高速数据线的时延问题,走线长度匹配后的数据线在上升/下降沿的具体时间基本相当,满足SI要求。