1 DDR NAND闪存的特性

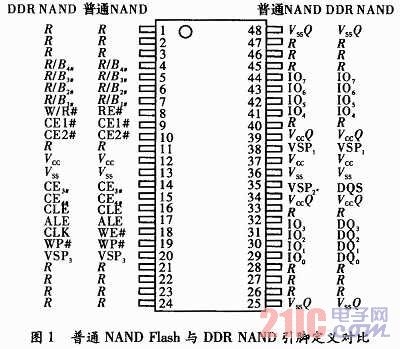

与传统的48脚NAND Flash引脚定义不同,DDRNAND闪存不再分别划分读时钟(RE#)和写时钟(WE#),而是将读写合为1个时钟,即CLK,而用W/R引脚的高低来区分这次是读操作还是写操作,如图1所示。数据I/O接口也改为正负双沿采集的DQ数据线。如图1中DDR NAND闪存部分所示,各引脚功能说明如下:

CE1#~CE4#:片选信号,低为使能。一个48脚的物理NAND Flash片子最多能同时包含(封装)4个NAND Flash。

CLE:命令锁存使能信号,高为使能。

ALE:地址锁存使能信号,高为使能

CLK:时钟信号。

W/R#:区分读写操作信号,高为写,低为读。

DQ0~DQ7:数据/地址/命令复用数据线。

R/B1#~R/B4#:NAND状态信号线。

VCC,VCCQ:接电源。

VSS,VSSQ:接地。

R:无定义。

2 对DDR NAND闪存的软件驱动操作

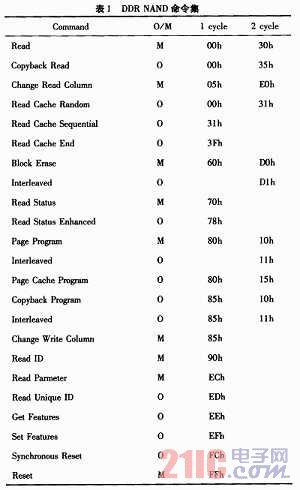

DDR NAND与普通NAND Flash一样,遵从ONFI协议的命令集合,如表1所示。其中,O/M项为M的必选,为O的可选,也就是说标有M的命令所有NAND Flash都支持,而标有O的命令则为部分支持部分不支持。

下面分别以NAND Flash最重要最为常用的驱动接口:读,写,擦为例,分别说明DDR NAND的操作流程。

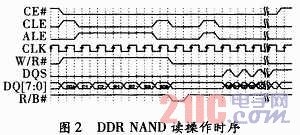

2.1 读操作

DDR NAND的读操作和写操作一般都是以页为单位操作的,与传统的NAND Flash一样,它允许在1个页读写周期内读取1 Byte到data区与spare区大小之和这么多字节。读取数据过程为:(1)先向DDRNAND发送读命令00h。(2)然后接着发送需要读取的DDR NAND的位置row地址和column地址。(3)接着发送读确认命令30 Hz,DDR NAND收到这个命令后会拉低RB信号线,然后开始工作,将相应的一页数据读取到DDR NAND里的页缓冲,读完后把RB信号线拉高,产生一个RB中断。(4)主控程序接收到RB中断后,发送同步时钟准备信号,即CLE和ALE同时产生一个cycle。(5)接着就可以发送读数据的clock cycle,每发送一个clock cycle就会在DDR NAND的页缓冲FIFO中送出2 Byte数据,上升沿一个,下降沿一个,因为DDR NAND是双沿采数的,同时DDR NAND也会控制DQS信号线与data同步。(6)主控程序发送完读数据的clock,读操作结束。如图2所示。

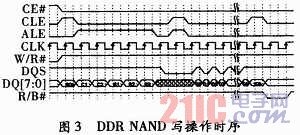

2.2 写操作

在DDR NAND中,写操作也叫编程。写操作的单位也是页,它的操作过程如下:(1)先向DDRNAND发送写命令80 Hz。(2)然后接着发送需要写入的DDR NAND的位置row地址和column地址。(3)发送同步时钟准备信号,即CLE和ALE同时产生一个cycle。(4)接着就可以发送读数据,发送数据是根据clock产生DQS信号,在DQS信号上下沿分别发送数据到DDR NAND。(5)发完一个page的数据后,接着发送写确认命令10 Hz,DDR NAND收到这个命令后会拉低RB信号线,然后开始工作,将相应的一页数据从DDR NAND里的页缓冲中正式编程到DDR NAND中,待编程完毕后把RB信号线拉高,产生一个RB中断,如图3所示,此时写操作已完成。

2.3 擦除操作

DDR NAND的擦除操作单位为block,擦操作比较特殊,它不涉及任何数据,没有用双沿操作的地方,所以它的操作过程和时序跟普通NAND Flash是一样的,操作过程如下:(1)先向DDR NAND发送擦命令60 Hz。(2)接着发送需要擦除的DDR NAND的位置,3 Byte的row地址。(3)发送擦确认命令d0h,DDR NAND收到这个命令后会拉低RB信号线,然后开始工作,待擦除完毕后再把RB信号线拉高,产生一个RB中断,一个block擦除完毕。

3 结束语

从市场方面了解到DDR NAND这种双沿采数的新型NAND Flash有逐步取代原高端16 bit NANDFlash之势,成为新的高端闪存。它具有更高的读写速率,不需要优化代码就能轻松突破存储速度的瓶颈限制。