O 引 言

随着现代通信业的不断发展,要求信号的频率测量范围也越来越宽,部分领域已达到110GHz。利用超外差法通过变频形式把信号变频到较低的中频上,以相对较低的成本实现llOGHz的频率测量范围,使得超外差式扫频接收机得到了广泛的应用。在超外差式扫频接收机中,扫描控制器的作用是控制协调各硬件单元,使得接收机内各部分同步于快速变化的扫描本振。扫描控制器的控制精度越高、控制速度越快,接收机的扫频准确度也就越高。目前,市场上有相当多的超外差式扫频接收机采用模拟的扫描控制方式,利用扫描斜波电压同步各扫描硬件单元,这种控制方式精度差,并且要求主控CPU实时干预扫描过程,使得接收机的扫描速度很慢。针对这些问题,本文提供了一种数字扫描控制器设计新方法。采用该方法,我单位在2005年成功开发了一种新型微波毫米波接收机,其扫描控制精度、扫描速度等指标较以前的接收机产品有了很大的提高。

1 扫描控制变量

超外差式扫频接收机在扫描过程中一般需要控制的变量有:YIG振荡器频率(或VCO频率)、YIG滤波器中心频率(或带通滤波器频率)、与测试频率相关的功率补偿数据(如平坦度补偿数据)等。

理想的YIG器件调谐曲线是一条直线(调谐曲线是根据谐振频率变化与线包电流变化绘制的曲线),但是,由于受磁性材料磁特性的影响,实际的调谐曲线是非线性的。与此类似,由于接收机内各部件(如混频器、滤波器等)幅度一频率响应曲线是非线性的,造成整机幅频曲线也是非线性的。

在工程上,通常采用多段直线逼近的方法对上述曲线进行线性化处理,就是将各控制量曲

线进行分段,在段内认为控制量曲线是一条直线。只要各线段分段点位置选取合适,可以保证整机指标满足设计要求。

通过计算各段控制量的起始值、步进值与步进个数(终止值减去起始值再除以步进量)就可以表征本段的控制量曲线。超外差式扫频接收机包含多种控制变量,因此对每种控制变量都需要计算其控制量的起始值、步进值与步进个数。又由于各控制量曲线不尽相同,所用逼近曲线的直线段数目也就不尽相同。划分的线段越多,逼近效果越好,控制精度也就越高。因此,在进行扫描控制之前,计算机主控的程序应该首先确定各控制量的分段数目和各段内的起始值、步进值、步进个数,这也就是送给扫描控制器的输入参数。另外,为了提高控制速度,避免在扫描过程中CPU干预扫描进程,在各控制量换段时要求设计的扫描控制器能够根据控制进度主动地读取下一段的换段信息。下面,我们详细介绍一下数字扫描控制器内各单元的组成及实现。

2 组成框图及控制时序

如图1所示,扫描控制器包括:地址译码/数据缓存单元、RAM存储单元、运算单元、触发单元、中断处理单元、步进脉冲发生单元和D/A输出单元。

扫描控制基本流程如下:

1)程序首先计算各控制量的分段数目及段内各控制量的起始值、步进值、步进个数。

2)通过系统总线,程序将上述计算好的数据依次送入扫描控制器内的RAM中保存。

3)程序控制触发单元产生全局中断信号,由中断处理单元通知运算单元读取各控制量首段的初始值。

4)程序控制触发单元产生使能信号,控制步进脉冲发生单元产生计数脉冲。这时运算单元开始进行累加/减计算并且计数器记录已产生的脉冲个数。累加/减运算器的输出值通过D/A变换器转换为电压值控制相关硬件电路。

5)当运算单元内计数器的计数值达到本段设定的步进个数时,运算单元产生中断信号通过中断处理单元进行中断识别并通知运算单元内已产生中断的模块自动从RAM内读取下一段的初始值。运算单元内四个模块产生中断的中断级别各不相同,如果多个中断同时产生,那么中断处理单元会对各中断进行缓存、排序并且首先处理中断级别高的中断。

6)当下一个计数脉冲到来时,运算单元内产生中断的模块又会重新开始累加/减运算并计数,重复4、5步。

7)触发单元记录扫描时间。当扫描时间达到预设值时,触发单元控制使能信号为低电平,各寄存器复位,扫描过程结束。

3 模块内部实现

1)地址译码/数据缓存单元地址译码/数据缓存单元连接外部总线,通过译码接收属于本扫描控制器的数据和控制字,包括:复位控制字、扫描使能控制字、触发单元内计数器的计数值(用于计算扫描时间)、步进脉冲发生单元内计数器的计数值(用于产生步进脉冲)以及RAM内需存储的控制量DAC值。

2)RAM存储单元

存储控制量DAC值。如果接收机内地址资源足够丰富,软件可以通过地址译码/数据缓存单元直接访问RAM。如果接收机内地址资源有限,可以将整个RAM划分为若干个区域(段地址),每个区域对应于一种控制量。每种控制量的各分段数据依次排列,可通过段内偏移地址访问。

3)运算单元

运算单元包括RAM数据回读模块、计数器及累加/减运算器模块。RAM数据回读模块的回读方式取决与RAM内数据的存储格式;计数器通过将读取的步进个数值与当前的计数值进行比较决定是否产生中断。在实际应用中,累加/减运算器位数有限,而计算的步进DAC值位数有可能大大超过运算器位数,这就要求设计人员必须认真选取步进DAC的有效长度,对DAC值进行适当截取,使控制误差能够在可接受的范围内。累加/减运算器模块在步进脉冲的触发下,对初始值进行累加/减运算,其DAC值输出位数等于选甩的DAC器件位数。

4)D/A输出单元

D/A输出单元负责将已累加/减数据转换为模拟信号输出。D/A输出单元时序同步于控制脉冲。如果扫描控制器硬件资源不多,可以给每一个控制量单独配置一个D/A转换器;否则,可以将这些控制量先缓存起来再通过一个D/A转换器输出以减少硬件成本。

5)触发单元

触发单元接收到扫描使能控制字后控制步进脉冲发生单元使能端有效,步进脉冲发生单元开始工作,进而使得整个扫描控制器运转起来。当触发单元内计数器的计数值与接收到的用于计算扫描时间的计数量相同时表明扫描过程已经完成,这时触发单元控制步进脉冲发生单元使能端失效,步进脉冲发生单元停止工作,扫描过程结束。另外,在扫描开始前触发单元接收控制字产生全局中断信号,通过中断处理单元通知运算单元调用各硬件控制量的初始DAC值。

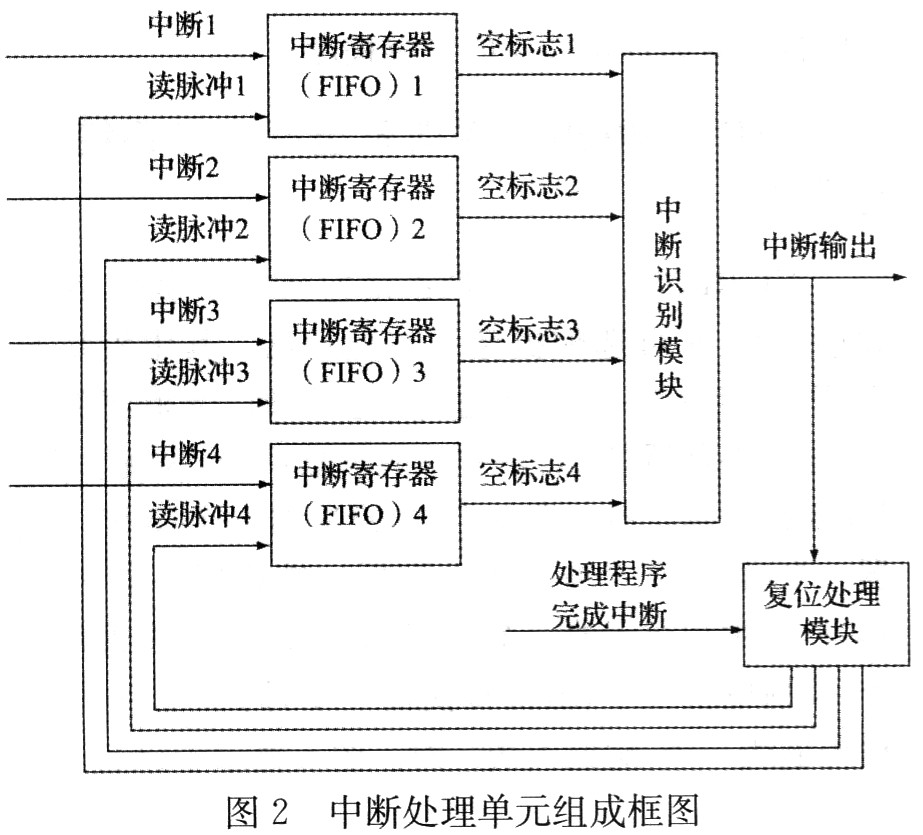

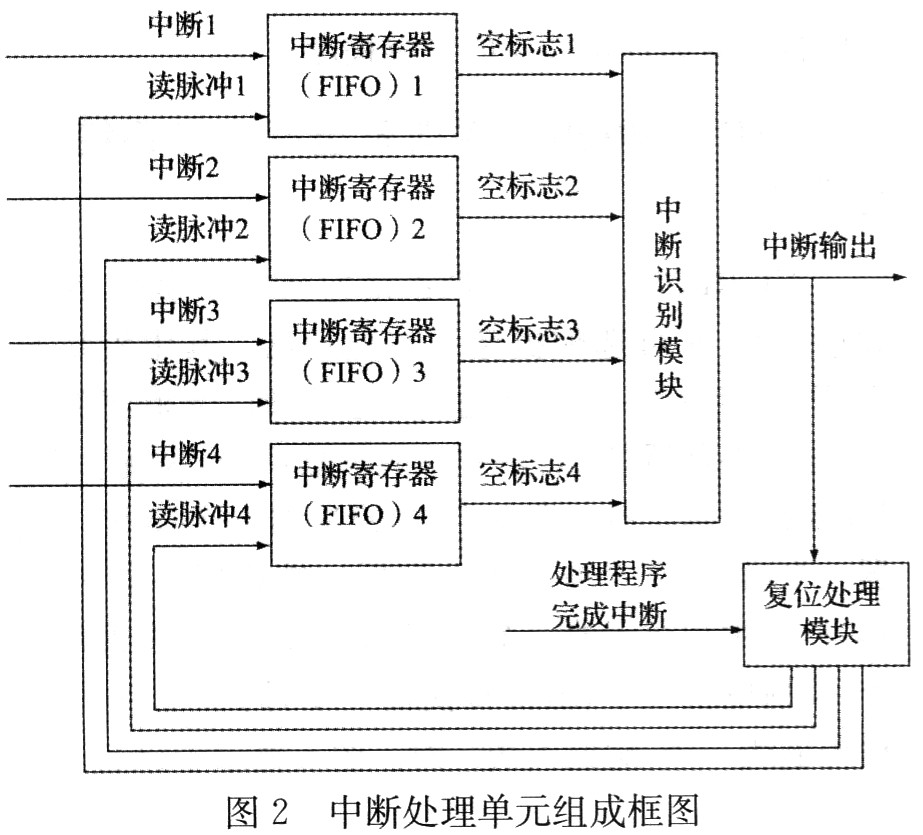

6)中断处理单元

中断处理单元根据预先设定的中断优先级别决定控制运算单元内各模块的先后顺序。中断处理单元由中断寄存器、中断识别模块、复位处理模块三部分组成。组成框图见图2所示。

扫描控制基本流程如下:

1)程序首先计算各控制量的分段数目及段内各控制量的起始值、步进值、步进个数。

2)通过系统总线,程序将上述计算好的数据依次送入扫描控制器内的RAM中保存。

3)程序控制触发单元产生全局中断信号,由中断处理单元通知运算单元读取各控制量首段的初始值。

4)程序控制触发单元产生使能信号,控制步进脉冲发生单元产生计数脉冲。这时运算单元开始进行累加/减计算并且计数器记录已产生的脉冲个数。累加/减运算器的输出值通过D/A变换器转换为电压值控制相关硬件电路。

5)当运算单元内计数器的计数值达到本段设定的步进个数时,运算单元产生中断信号通过中断处理单元进行中断识别并通知运算单元内已产生中断的模块自动从RAM内读取下一段的初始值。运算单元内四个模块产生中断的中断级别各不相同,如果多个中断同时产生,那么中断处理单元会对各中断进行缓存、排序并且首先处理中断级别高的中断。

6)当下一个计数脉冲到来时,运算单元内产生中断的模块又会重新开始累加/减运算并计数,重复4、5步。

7)触发单元记录扫描时间。当扫描时间达到预设值时,触发单元控制使能信号为低电平,各寄存器复位,扫描过程结束。

3 模块内部实现

1)地址译码/数据缓存单元地址译码/数据缓存单元连接外部总线,通过译码接收属于本扫描控制器的数据和控制字,包括:复位控制字、扫描使能控制字、触发单元内计数器的计数值(用于计算扫描时间)、步进脉冲发生单元内计数器的计数值(用于产生步进脉冲)以及RAM内需存储的控制量DAC值。

2)RAM存储单元

存储控制量DAC值。如果接收机内地址资源足够丰富,软件可以通过地址译码/数据缓存单元直接访问RAM。如果接收机内地址资源有限,可以将整个RAM划分为若干个区域(段地址),每个区域对应于一种控制量。每种控制量的各分段数据依次排列,可通过段内偏移地址访问。

3)运算单元

运算单元包括RAM数据回读模块、计数器及累加/减运算器模块。RAM数据回读模块的回读方式取决与RAM内数据的存储格式;计数器通过将读取的步进个数值与当前的计数值进行比较决定是否产生中断。在实际应用中,累加/减运算器位数有限,而计算的步进DAC值位数有可能大大超过运算器位数,这就要求设计人员必须认真选取步进DAC的有效长度,对DAC值进行适当截取,使控制误差能够在可接受的范围内。累加/减运算器模块在步进脉冲的触发下,对初始值进行累加/减运算,其DAC值输出位数等于选甩的DAC器件位数。

4)D/A输出单元

D/A输出单元负责将已累加/减数据转换为模拟信号输出。D/A输出单元时序同步于控制脉冲。如果扫描控制器硬件资源不多,可以给每一个控制量单独配置一个D/A转换器;否则,可以将这些控制量先缓存起来再通过一个D/A转换器输出以减少硬件成本。

5)触发单元

触发单元接收到扫描使能控制字后控制步进脉冲发生单元使能端有效,步进脉冲发生单元开始工作,进而使得整个扫描控制器运转起来。当触发单元内计数器的计数值与接收到的用于计算扫描时间的计数量相同时表明扫描过程已经完成,这时触发单元控制步进脉冲发生单元使能端失效,步进脉冲发生单元停止工作,扫描过程结束。另外,在扫描开始前触发单元接收控制字产生全局中断信号,通过中断处理单元通知运算单元调用各硬件控制量的初始DAC值。

6)中断处理单元

中断处理单元根据预先设定的中断优先级别决定控制运算单元内各模块的先后顺序。中断处理单元由中断寄存器、中断识别模块、复位处理模块三部分组成。组成框图见图2所示。

中断处理过程如下:首先,四种中断分别缓存入四个中断寄存器。中断寄存器使用FIFO存储单元可以储存多个中断,利用FIFO存储单元内部自身的标志位作为逻辑判断依据可以简化我们的设计。其次,中断识别模块检测各FIFO存储单元的空标志位。如果有任意一个FIFO存储单元的空标志位为O,则说明有中断产生,那么中断识别模块将按中断优先级别排序,并产生一个脉冲通知与最高中断级别相对应的运算单元内的数据调用模块从RAM中读取下一段控制量的初始值。再次,数据调用模块完成读取任务后返回给复位处理模块一个处理程序完成标志。复位处理模块在收到处理程序完成标志后根据输出中断类别产生读脉冲至空标志位为O且中断优先级别最高的中断寄存器中。此时,中断寄存器的空标志位有可能发生变化。最后,中断识别模块再次检测所有的空标志是否都为1,如果不是,中断处理单元继续上述过程直到所有的空标志都为1。中断处理过程结束。

7)步进脉冲发生单元

步进脉冲发生单元内包含多个计数器,计数使能由触发单元控制,计数器的模从地址译码/数据缓存单元读取。每隔一定时间,步进脉冲发生单元产生计数脉冲作为累加/减器的时钟并由运算单元内计数器计数。

4 设计实例

以某型号微波毫米波接收机为例。在此接收机中,系统总线设计为串行总线,需要控制的变量有YIG振荡器频率、YIG滤波器中心频率、平坦度补偿数据和预选器带宽控制电压。选用Altera公司的EplkSOQC208—3芯片作为数字扫描控制器芯片,IDT71V016SA20Y作为RAM存储芯片,AD7538KR、DAC8412作为DAC转换芯片。

经测量,YIG振荡器频率开环控制精度达到5MHz(接收机锁相环的锁频范围可达80MHz),YIG滤波器中心频率控制精度达到3MHz(YIG滤波器3dB带宽最小处40MHz),平坦度补偿值误差小于O.2dB,预选器带宽误差小于带宽2%。数字扫描控制器选用60MHz时钟作为外部时钟,在最忙碌情况下(四种中断同时到来),完成四种中断处理总时间小于5μs。

通过仿真和测试数字扫描控制器仅使用了FPGA内约70%的资源,可以为今后的模块扩展留有余地。

5 结束语

对于扫描控制器自身硬件来说,我们可以通过将控制量曲线划分更多段、更加逼近真实曲线,达到提高控制精度的目的;通过选用高档的FPGA芯片并提高系统工作时钟,达到提高控制速度的目的。但在实际使用过程中,我们还必须综合考虑硬件自身的性能(如YIG器件磁滞效应、机械开关切换时间、中频滤波器响应时间等)、软件设计复杂度、要求的性能指标等多组因素对扫描控制精度、速度的影响,合理选择划分段数及工作时钟,最大限度挖掘出接收机潜能