1 引言

随着集成电路规模的发展, 电子设备的体积、重量和功耗越来越小, 这对电源电路的集成化、小型化及电源管理性能提出了越来越高的要求。而随着片上系统( SOC) 的不断发展, 单片集成的LDO 线性稳压器的应用也越来越广泛[1]。对于片内的LDO,最担心的是寄生电容过大引起不稳定,论文针对片内应用而设计的这款LDO,能保证在uF 级别的寄生电容范围内都可以正常工作,毕竟寄生电容再大也不至于是μF 级别的。功耗是LDO 线性稳压器的重要指标之一,一般的LDO 功耗都在几十μA 以上,例如文献[2]中电路的静态电流为38μA,文献[3]中静态功耗高达65μA, 而本文的静态功耗做到10μA 左右,不仅功耗低,本文中第二级靠电阻的电流关系提供了一个小增益级,并且提高了整个LDO的带宽。

2 LDO 电路组成原理与关键模块设计

2.1 电路基本工作原理

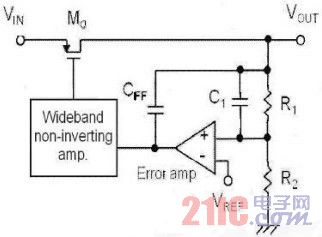

图1 是LDO 线性稳压器的结构框图, 由下面几个部分组成:基准电压源(Vref)、误差放大器、同相放大器、反馈电阻网络、调整管等。其中基准电压源输出参考电压Vref, 要求它精度高, 温漂小。误差放大器将输出反馈回来的电压与基准电压Vref 进行比较, 并放大其差值,其经过同相放大器来控制调整功率管的状态, 因而使输出稳定。在这里C1 是前馈电容,可以提高负载调整率,并增加了一个左零点补偿,Cff提供一个零点补偿。第一级放大器就是一个差分对,和大多数误差放大器结构一样,第二级为同相放大级,靠电阻的电流关系提供一个小增益级,并控制带宽。相对于普通结构而言的,如果靠运放直接驱动功率管,那带宽就被功率管的寄生电容和运放输出阻抗和增益决定了,而这个结构的增益和输出阻抗,相比运放小很多,带宽自然就提高很多。表1 为该LDO 的主要设计参数和性能指标。

图1 LDO 线性稳压器结构示意图

表1 LDO 的设计参数和性能指标

2.2 电路组成与设计

(1)调整管结构设计:MOS 型线性稳压器的调整管是电压驱动的, 能大大降低器件消耗的静态电流, 而且其较小的导通阻抗使得漏失电压也比较低,从而提高了电源的转换效率[4]。根据调整管的平方率关系式以及设计指标Vdropout ≈ 200mV,可以计算出调整管的宽长比, 结合调整管的栅极寄生电容以及工艺的要求,在重载情况下考虑调整管需工作在线性区, 将调整管的宽长设计为:W=6000μm,L=0.5μm。

(2)电阻R1 与R2 选择:输出电压由反馈网络决定,根据VOUT =VREF[(R1+R2)/R1],当选定的VREF=1.25V,R1 = 625KΩ,那么R2 = 625KΩ。

2.3 误差放大器(EA)设计

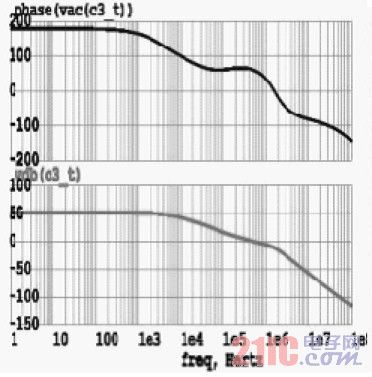

为保证低功耗的前提下I1设为5μA,I2设为3μA,在小的偏置电流以及较大的负载的情况下为了保证能得到不小于25dB 的增益,把RF设计为500K。由于同相放大器的增益随负载的增加而减小,在设计中需要适当增加偏置电流I1 和增加RF的值[7]。而带宽受M2 的跨导和调整管的W/L 的影响,需要增加M2 的W/L 以及偏置电流I2。图中M1 的宽长比为4/1, 这里取W1=30μm,L1=3μm,M2 的宽长比为110/1,取W2=110μm,L2=1μm。仿真结果如图5 所示。

图5 同相放大器的增益

3 LDO 整体仿真结果与讨论

我们基于HHNEC 0.35um BCD 工艺下,采用cadence 和Hspice 仿真软件对整体电路做仿真,如图6 所示为LDO 环路稳定性仿真曲线。

(a)负载电流为50mA 仿真曲线

(b)负载电流为0 时仿真曲线

图6 LDO 环路稳定性仿真曲线

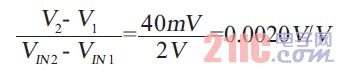

(a) 图为负载电流为50mA 时,LDO 环路增益为50dB、单位增益带宽为470KHZ、相位裕度为74degree。(b)图为负载电流为0 时,LDO 环路增益为63dB、单位增益带宽为1KHZ、相位裕度为87degree。图7 给出了该LDO 的线性调整率曲线,仿真条件为C L=1μF, 由仿真曲线可以看出该LDO 的线性调整率为:

图7 CL=1μF 线性调整率曲线

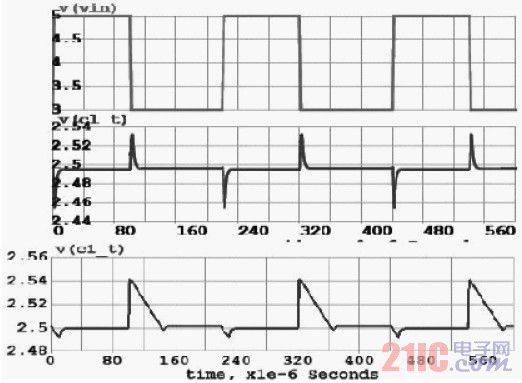

图8 给出了该LDO 的负载调整率曲线,仿真条件为CL=1μF, 由仿真曲线可以看出该LDO 的负载调整率为:

图8 CL=1μF 负载调整率曲线

图9 给出了该LDO 的电源抑制比仿真曲线,仿真条件为IL=1mA。从该曲线可以看出,该LDO 的PSRR 在1KHZ时为- 60dB。

图9 电源抑制比仿真曲线

4 结论

本文提出的这款LDO 线性稳压器,能保证在μF 级别的寄生电容范围内都可以正常工作。

该LDO 的静态电流低至10μA,文中同相放大器的引入,提高了整个LDO 的带宽。从仿真结果可以看出,在负载电流Iload=50mA 时,带宽为470KHz。

该LDO 其它各方面指标都满足设计要求。