ADV7125有3个视频数据寄存器DATA REGISTER和一个视频控制寄存器POWER-DOWN MODE。数据寄存器的3个输入端分别连接红绿蓝三色的数字视频信号,数据寄存器后面紧跟数模转换单元,将数字信号转换为模拟信号;控制寄存器将数字的消隐信号、同步信号转换合并。数模转换后的模拟视频信号和控制寄存器输出的同步、消隐控制信号共同作为ADV7125的输出信号,此输出信号大小受Rset端和地之间接入的外加电阻RSET大小的控制。

2 ADV7125芯片用于VGA转换的基本原理

ADV7125芯片用于VGA转换的基本原理是,将S3C2440输出的数字视频信号转换为模拟的VGA输出信号,模拟的VGA输出信号的大小受ADV71 25芯片外围参考电压VREF和外加电阻RSET的控制,(VREF和RSET的具体接法如图4所示)其关系如下:

![]()

式中IOG、IOR、IOB分别代表绿、红、蓝三色信号的幅度。当不用复合同步信号![]() 时,需要把

时,需要把![]() 端连接低电平,这时IOG的关系式同式(2)。

端连接低电平,这时IOG的关系式同式(2)。

上式中的![]() 是ADV7125的一个附加信号控制端,ADV7125的另外一个附加信号控制端是

是ADV7125的一个附加信号控制端,ADV7125的另外一个附加信号控制端是![]() (消隐信号控制端)。

(消隐信号控制端)。![]() 和

和![]() 都是在时钟上升沿被锁存,保证像素数据流的同步。

都是在时钟上升沿被锁存,保证像素数据流的同步。![]() 和

和![]() 的功能是:通过视频同步信号的编码,影响VGA视频信号的输出。通过在模拟输出端口内部加了一个加权电流,实现此功能。这个电流的有无,由

的功能是:通过视频同步信号的编码,影响VGA视频信号的输出。通过在模拟输出端口内部加了一个加权电流,实现此功能。这个电流的有无,由![]() 和

和![]() 逻辑输入判定。

逻辑输入判定。

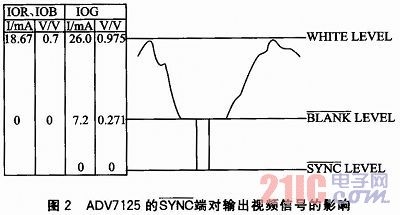

图2说明了当![]() 和

和![]() 两者都为高电平时,IOR和IOB两者与IOG的对比。

两者都为高电平时,IOR和IOB两者与IOG的对比。

表1详细说明了![]() 和

和![]() 对模拟输出的影响。该表是在VREF=1.235 V,RSET=530 Ω,RLOAD=37.5Ω的条件下测量的。

对模拟输出的影响。该表是在VREF=1.235 V,RSET=530 Ω,RLOAD=37.5Ω的条件下测量的。

对应图2和表1可得到以下结论:

①当IOR、IOG、IOB三端的DAC输入为0x00时,代表屏幕最黑,此时对应图2为![]() LEVEL,对应表1为第7行。从图2左面列表可以看到,IOR、IOB端的电流、电压分别是0mA、0V,IOG端的电流、电压分别是7.2 mA、0.271 V。即电流相差7.2 mA。

LEVEL,对应表1为第7行。从图2左面列表可以看到,IOR、IOB端的电流、电压分别是0mA、0V,IOG端的电流、电压分别是7.2 mA、0.271 V。即电流相差7.2 mA。

②当IOR、IOG、IOB三端的DAC输入为0xFF时,代表屏幕最白,此时对应图2为WHITE LEVEI,对应表1为第2行。从图2左面列表可以看到,IOR、IOB端的电流、电压分别是18.67 mA、0.7 V,IOG端的电流、电压分别是26.0 mA、0.975 V。即电流相差7.3 mA。

从表1,可以得到以下的结论:

①当![]() 和

和![]() 都为高电平(为1)时,IOG端口的白电平信号的电流,要比IOR、IOB端口同样情况下的电流高出7.3mA左右;视频信号电流、黑电平信号的电流,要比IOR、IOB端口同样情况下的电流高出7.2 mA左右。

都为高电平(为1)时,IOG端口的白电平信号的电流,要比IOR、IOB端口同样情况下的电流高出7.3mA左右;视频信号电流、黑电平信号的电流,要比IOR、IOB端口同样情况下的电流高出7.2 mA左右。

②当![]() 为低电平(为0)、

为低电平(为0)、![]() 任意时,同样的DAC输入条件下,IOR、IOB、IOG三端的输出信号电流大小是完全一样的。

任意时,同样的DAC输入条件下,IOR、IOB、IOG三端的输出信号电流大小是完全一样的。

③当![]() 为低电平(为0)时,无论DAC输入是多少,IOR、IOG、IOB三端的输出信号均对应于

为低电平(为0)时,无论DAC输入是多少,IOR、IOG、IOB三端的输出信号均对应于![]() 高/低的同步无效/有效黑电平。

高/低的同步无效/有效黑电平。

3 VGA接口设计

根据需要,把LCD信号转换为VGA信号,转换时必须根据VGA信号的时序进行转换。VGA信号一共包括5部分,分别是红(R)、绿(G)、蓝(B)三色信号和行(H)、场(V)同步信号,红(R)、绿(G)、蓝(B)三色信号和行(H)、场(V)同步信号根据S3C2440的配置时序,由S3C2440以数字信号的形式输出,之后由ADV7125对红(R)、绿(G)、蓝(B)三色信号进行转换,行(H)、场(V)同步信号直接进入VGA接口中,不需要转换。下面分别介绍VGA信号的时序、硬件连接、软件设计以及注意事项。

3.1 VGA时序信号

以分辨率为640x480、刷新频率为60 Hz、16位的彩色显示模式为例,VGA信号的扫描时序如图3所示。

在场扫描时序中,VSYNC为场同步信号,Tvsync是指显示器扫描1帧完整画面需要的时间,大小为16 667μs;VSYNC信号每场有525行,其中480行为有效显示行,45行是场消隐期。场消隐期包括场同步时间(低电平场同步脉冲)twv(2行/63μs)、场消隐前肩tHV(13行/412μs)、场消隐后肩tVH(30行/952 μs),共45行。

在行扫描时序中,HSYNC为行同步信号,Thsync是指显示器扫描一行需要的时间,大小为31.75μs,该周期通过Hsync(行同步脉冲)来同步,脉冲的宽度tWH=3.81μs。每显示行包括800点,其中640点为有效显示区,160点为行消隐期(是非显示区)。行消隐期包括行同步时间tWH(3.81μs),行消隐前肩tHC(0.516μS)和行消隐后肩tCH(1.786μs),共160个点时钟。

3.2 S3C2440和ADV7125的电路连接

设计中主要使用S3C2440处理器的LCD控制器接口,它主要通过DMA方式占用系统总线,支持彩色TFT液晶屏,支持16 bbp无调色真彩。LCD接口数据的低8位,中间8位和高8位分别与ADV7125芯片的BLUE信号、GREEN信号和RED信号相连,这样就完成了S3C2440处理器与ADV7125芯片之间数字信号的传输。ADV7125芯片的时钟信号采用LCD接口的时钟信号,![]() 信号与VM(VSDN)信号相连接,

信号与VM(VSDN)信号相连接,![]() 同步信号接地。COMP端用于内部参考运放的补偿,用0.1μF的陶瓷电容连接在COMP与模拟电源VAA之间,防止自激振荡以增加稳定性。采用AD1580作为参考电压,AD1580输出信号稳定,能够很好地满足电路设计的需要。RSET引脚与地之间接一个530 Ω的电阻,用来控制视频信号的满幅度。在图像系统中,不会自动产生复合同步信号

同步信号接地。COMP端用于内部参考运放的补偿,用0.1μF的陶瓷电容连接在COMP与模拟电源VAA之间,防止自激振荡以增加稳定性。采用AD1580作为参考电压,AD1580输出信号稳定,能够很好地满足电路设计的需要。RSET引脚与地之间接一个530 Ω的电阻,用来控制视频信号的满幅度。在图像系统中,不会自动产生复合同步信号![]() ,利用本设计可以实现视频同步信息编码直接进入绿色信道。如果不需要,把

,利用本设计可以实现视频同步信息编码直接进入绿色信道。如果不需要,把![]() 输入端与逻辑低电平相连。S3C2440和ADV7125的电路连接如图4所示。其中VD0、VD1、…VD23、VDEN、CLK、HSYNC、VSYNC为S3C2440的输出端。

输入端与逻辑低电平相连。S3C2440和ADV7125的电路连接如图4所示。其中VD0、VD1、…VD23、VDEN、CLK、HSYNC、VSYNC为S3C2440的输出端。

3.3 电路连接需要注意的问题

ADV7125可以用于灰度视频信号输出。例如:仅用于1个通道进行视频输出,这时其他两个不用的视频数据信道都应该与逻辑0相连,不用的模拟输出应该与使用的信道一样连接相同的负载。

为了实现ADV7125的最优噪声性能,对PCB的设计必须特别注意。ADV7125电源和地线上的噪声应该优化。可以通过屏蔽数字输入和提供好的退耦达到这一点。VAA和GND的引线长度应该尽量短,这样可以减小电感环路。在设计PCB时应尽量把模拟地与数字地分开,地线应该通过1个磁珠与PCB大面积铺地相连,并且磁珠应该尽可能的靠近ADV7125器件的地引脚。电路中使用的电容应该尽可能的靠近对应引脚,并且电容的引线应该尽可能的短,这样可以减小引线电容。由于使用频率非常高,时钟引线应尽可能地短,这样可以减小噪声的抖动。视频输出信号应该由数字地平面覆盖,这样可以增大高频电源抑制比。

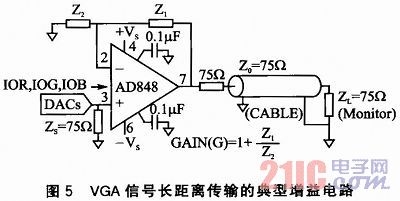

由于模拟RGB信号采用高阻电流源输出方式,可以直接驱动75 Ω的同轴传输线。长于10 m的电缆可能会对高频模拟输出脉冲衰减。使用输出缓冲可以补偿电缆的失真。这些缓冲器在整个输出电压摆幅期间,必须有足够的电流。常见的有AD84x系列的单片运放。在较高的频率下(如80 MHz),推荐使用AD848。其典型增益电路如图5所示。

通过简单的计算可以得知其增益为:GAIN=1+Z1/Z2。改变缓冲电路的增益器件Z1、Z2来满足所要求的视频电平。

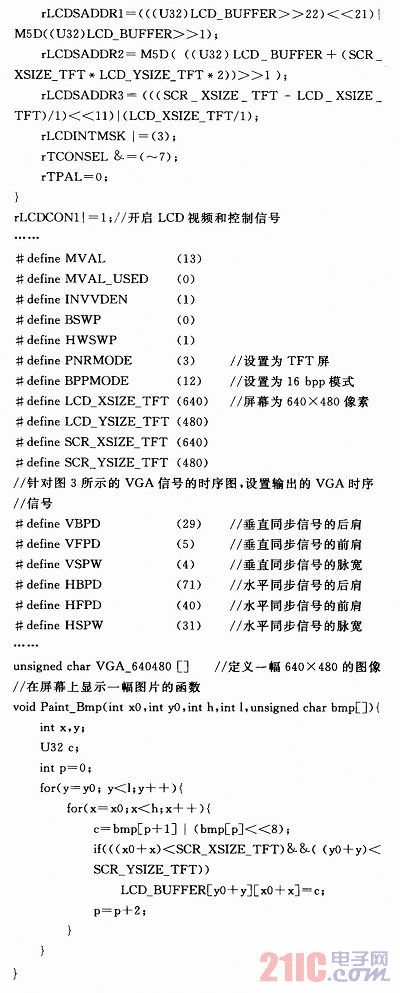

3.4 相关的软件设置

下面以简单的测试程序为例来说明相关软件的编写。

软件设计的基本流程如图6所示。具体过程如下:

①首先对LCD的功能寄存器进行初始化,主要设置LCD控制寄存器1~5,LCD缓冲区起始地址控制寄存器;屏蔽LCD中断。

②其次对LCD的输出时序(VGA信号时序)进行设置。设置分辨率、周期、前(后)信号、同步脉冲。

③再次是对视频信号进行设置,主要是使能LCD视频信号的输出。

④用一幅图像的输出来测试VGA的显示是否正常。

主要代码如下所示:

结语

本文结合S3C2440处理器和ADV7125芯片的特点,介绍了LCD转VGA方案,该方案简单易行,适用于嵌入式系统设备的VGA信号输出。ADV-7125芯片有多种频率可供选择。本设计也可以用于灰度级输出的信号中,在此基础上进行一些简单的修改,可以满足高分辨率,高刷新频率的环境要求。