本文设计了一种应用于负电源的电平位移电路。实现从0~8V低压逻辑输入到8~-100V高压驱动输出的转换。分析了该电路的结构和工作原理。基于此电路结构设计了满足应用要求的高压薄膜SOI LDMOS器件。分析了器件的工作状态以及耐压机理,并利用工艺器件联合仿真对器件的电学特性进行了优化设计。

在栅驱动电路中需要电平位移电路来实现从低压控制输入到高压驱动输出的电平转换。而在一些领域如SOC中的待机模式激活、ESD保护等需要能工作在负电源的电平位移电路。

SOI(Silicon-On-Insulator)技术以其高速、低功耗、高集成度、极小的寄生效应以及良好的隔离等特点,在集成电路设计应用中倍受青睐。

本文基于SOI高压集成技术设计了电源电压为8~-100V的电平位移电路,并对电路中的核心LDMOS器件进行了设计和模拟仿真优化。

1 电路结构

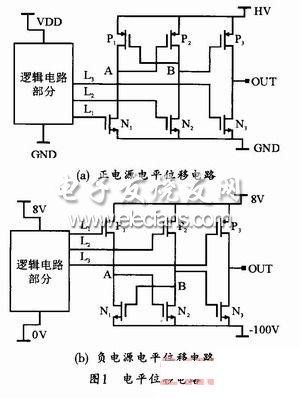

传统正电源应用的电平位移电路结构如图1(a)所示。L1、L2、L3是由逻辑电路部分产生的低压时序控制信号,N1、N2、N3为高压nLDMOS器件,P1、P2、P3为高压平pLDMOS器件。由P1,P2和N1、N2构成的电平位移单元将L1、L2的低压逻辑信号转变为可以控制P3管的高压电平,与L3一起控制由P3和N3组成的反向输出级,从而实现从低压逻辑信号到高压驱动输出的转换。

在正电源电平位移电路中,由于nLDMOS的源极为低压,所以可以通过低压逻辑部分来控制其开关状态,而源极为高压的pLDMOS则通过电平位移来控制。当高压驱动电压为8~-00V,低压逻辑部分工作电压为0~8V时,电平位移转换部分的电压分布本身没有改变,但是在和低压控制端接合时,与传统的正电源相比电平发生了改变,就需要重新设计低压逻辑的控制方式。此时,nLDMOS的源极为-100V电压,显然不能通过低压逻辑控制部分的0~8V电压来实现控制,而pLDMOS的源极为8V电源。因此采用了低压逻辑输出直接控制pLDMOS,而nLDMOS则通过电平位移来控制的方法,如图1(b)所示。

2 器件设计及优化

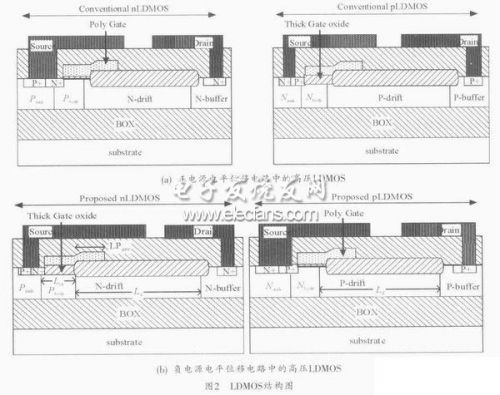

由于负电源供电的电平位移电路结构的改变,应用于正电源的常规nLDMOS和pLDMOS不能满足该电路结构要求。在正电源供电的电平位移电路中,由于pLDMOS的源端接高压电源,其栅源需要承受高压,所以pLDMOS采用了厚栅氧的结构,如图2(a)所示。在使用负电源的电平位移电路结构中(图1(b)),pLDMOS的源端为逻辑高压8V,栅端由低压逻辑0~8V电压控制,因此栅源不再承受高压。但是nLDMOS的源端为负电源的最低电位,其栅源需要承受高压,因此高压nLDMOS需要采用厚栅氧结构,如图2(b)所示。

电源的改变不仅仅改变了电路的结构,nLDMOS的厚栅氧,同时器件的耐压机理也发生了改变。考虑到低压管的背栅效应,SOI材料的衬底只能接地,因此源漏电平的改变将引起nLDMOS和pLDMOS耐压机理的改变。图3是利用工艺(Tsuprem4)、器件(Medici)联合仿真得到的正电源和负电源电平位移电路中高压nLDMOS和pLDMOS关态击穿时等势线分布对比图。对于nLDMOS,常规正电源应用的衬底电位对于漂移区来说是辅助耗尽作用,这就是常规SOI中的RESURF原理。但是对于负电源的nLDMOS来说,衬底不再起辅助耗尽SOI层漂移区的作用(图3(b))。对于pLDMOS来说,情况刚好相反。所以针对负电源应用,两种器件都要进行相应的优化处理。

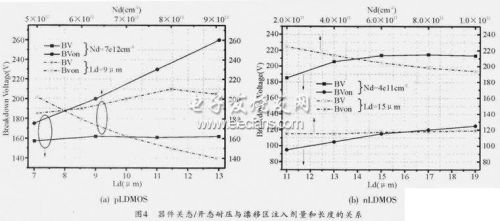

利用工艺器件联合仿真,在传统的正电源应用的LDMOS基础上对器件的结构参数进行优化设计。图4(a)为pLDMOS在漂移区注入剂量Nd=7 e12cm-2时关态耐压、开态耐压与漂移区长度Ld(μm)的关系,以及在漂移区长度Ld=9μm情况下关态耐压、开态耐压与漂移区注入剂量Nd(cm-2)的关系。其他参数为:n型体区注入剂量5e12 cm-2,Nsink注入剂量3e15 cm-2,P-buffer注入剂量1.5e13 cm-2,沟道长度3μm,栅极场板3μm。从仿真结果可以看出:pLDMOS的关态耐压随漂移区的增加而增大,随漂移区的注入剂量的增大先增大后减小;开态耐压随着漂移区注入剂量的增大而降低,但是在一定范围内漂移区长度对其影响较小。总体上,pLDMOS的关态耐压、开态耐压都在160V以上,完全能够满足8~-100V工作电压(108V耐压)的要求。

图4 (b)为nLDMOS在漂移区注入剂量Nd=4e11cm-2时关态耐压、开态耐压与漂移区长度Ld(μm)的关系,以及在漂移区长度Ld=15μm情况下关态耐压、开态耐压与漂移区注入剂量Nd(cm-2)的关系。其他参数为:p型体区注入剂量5e13 cm-2,Psink注入剂量3e15 cm-2,N-buffer注入剂量1e13cm-2,沟道长度3μm,栅极场板3.5μm。相对于pLDMOS,漂移区注入剂量和漂移区长度对于开态耐压、关态耐压的影响不大。同时关态耐压都能维持在180V以上,但是开态耐压却只有90~120V,不能满足8~100V工作电压(108V耐压)的要求。nLDMOS开态耐压问题成为电路、器件设计的关键。

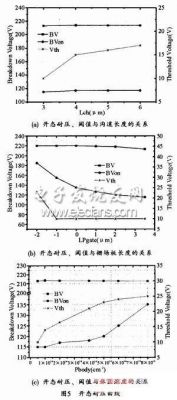

针对nLDMOS器件开态耐压低的问题,有针对性地仿真了沟道长度、多晶硅栅场板长度及体区浓度对开态耐压的影响。图5(a)为nLDMOS的关态耐压、开态耐压及阈值与沟道长度(Lch)的关系。可以看出沟道长度对器件的开态耐压和关态耐压影响很小。阈值随着沟道长度的增加而增加,这是由于采用横向双扩散形成沟道,所以随着沟道长度增加,p型体区的浓度越来越大,阈值也就越来越大。图5(b)为nLDMOS的关态耐压、开态耐压及阈值与多晶硅栅极场板长度(LPgate)的关系。在栅极场板较长时,其对阈值和关态耐压影响很小,当栅极场板缩短到多晶硅栅不能覆盖沟道时,器件的开态耐压大幅增加。这时阈值也迅速增加。虽然多晶硅栅不能完全覆盖沟道,但是由于开态时nLDMOS的栅漏电压差很大,所以仍然能够在表面形成反型层沟道。因此,大幅减短栅极场板能有效提高器件的开态耐压,但是同时也带来了器件不能有效开启的问题。图5(c)为nLDMOS的关态耐压、开态耐压及阈值与体区注入剂量(Pbody)的关系。可以看出增加体区的注入剂量对器件的耐压影响很小。但是随着注入剂量的增加,体区浓度增加,所以阈值就增加,同时器件的开态耐压也随之增加。当体区注入剂量达到5e14cm-2时,阈值增加缓慢,开态耐压却大幅增加,所以只能通过阈值上的牺牲来改善nLDMOS的开态击穿耐压。

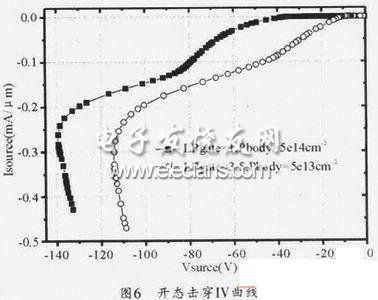

通过以上分析,发现提高nLDMOS的开态击穿电压最有效的方法是缩短栅极场板和提高体区注入剂量。这二种方法的实质提高导通阻抗或降低电流能力。但是对于普通应用的nLDMOS,电流能力本身就比pLDMOS有优势。当应用到负电源电平位移电路中时,厚栅氧高栅源电压使得nLDMOS的电流能力更加突出,但是同时也导致了开态耐压的降低。所以提高nLDMOS开态击穿电压就必须降低其电流能力。如图6所示,在nLD-MOS正常工作时,源端的电压为-100V,此时饱和电流相差0.05mA/μm。

在缩短栅极场板到1μm,提高体区注入剂量到5e14 cm-2的情况下,在得到nLDMOS的阈值电压为24V,关态击穿电压215V,开态击穿电压140V,能够满足-100V电压的应用要求。

3 结束语

基于此电路结构设计了满足电路应用需求的高压器件。并对高压LDMOS进行了优化设计,尤其是高压nLDMOS的开态耐压。得到高压nLDMOS的关态击穿电压215V,开态击穿电压140V,阈值电压24V;高压pLDMOS的关态击穿电压200V,开态击穿电压160V,阈值电压-1V。

.