目前在Altera SOPC">SOPC Builder下集成了包括UART、SPI、Ethernet、SDRAM、Flash、DMA等控制器的IP核。此外,用户也可以根据系统的需要自己设计或者购买第三方厂商的IP核,通过Avalon总线像搭积木一样方便地将其捆绑在系统上。IP核是经过功能验证的知识产权核,使用IP 核有以下优势:(1)提高设计性能;(2)降低产品开发成本;(3)缩短设计周期;(4)设计灵活性强;(5)仿真方便;(6)OpenCore Plus支持无风险应用。

当然本论文所说的IP核功能没有那么丰富,实际上就是一个功能验证正确的用户逻辑,和商业应用的IP核还有一定的差距。本文的主要工作就是通过硬件描述语言描述了视频信号的采集,分配,存储以及色度空间的转换等逻辑,并且验证了功能的正确性。

1 视频编解码Camera_show原理

嵌入式摄像控制系统除了必要的电源电路以外,还要包括存储电路、通信电路和下载电路等,所有的设备均与Avalon总线连接,这里主要介绍用户逻辑接口Camera_show,它完成了模拟视频数据转化成数字视频数据并在VGA上显示的功能,主要包括模拟视频信号的采集、分配(串并转换电路完成)、存储(存储控制逻辑和片上RAM完成)和色度空间转换。具体的功能框图如图1所示。

图1 用户逻辑Camera_show的原理框图

2 视频编解码IP核Camera_Show设计

视频编解码IP 核主要完成的功能包含视频信号的采集、分配、存储以及色度空间的转换。模拟视频信号经过ADV7181B后变成了符合ITU-R656的YUV数字信号,但是要对YUV信号进行处理必须将这三路信号分开并行处理,所以需要采集分配这三路信号,这是2.1的IP核需要实现的功能;由于模拟视频信号是隔行扫描的,但是CRT显示器是逐行扫描,如果不加处理那么必然会导致行错开,所以需要将数据进行存储,通过控制实现隔行变逐行,这是2.2的IP核需要实现的功能;最后经过处理的YUV三路数字信号,需要完成色度空间的转换变成RGB信号,这是2.3的IP核需要实现的功能。

2.1 YUV信号的采集、分配

在嵌入式摄像控制系统中,ADV7181主要承担着模拟摄像头的视频数据进行解码的任务,将CVBS的等模拟信号转化成ITU-R656标准的YUV信号。图2给出了ADV7181的功能框图。

图2 ADV7181功能框图

由图可以看到,对于输入的CVBS等模拟信号经过ADV7181B芯片转换后输出YUV信号,行同步信号HS,帧同步信号VS。这些就是需要的数字视频信号,也就解决了数字视频源的问题。图2给出了YUV信号的组成排列方式,“FF,00,00”作为AV信号的开始,所以需要构造一个检测电路。注意到SAV和EAV均是FF,00,00开头但是XY的值不一样。根据芯片资料,XY表示的是V,即有用信号与空白信号的分界点,如果V=0则表示的是SAV,否则是EAV 。XY是场信号的区分标志。0是奇场,1是偶场。

模拟信号的一行是1716个CLOCK,有用信号是1440个CLOCK,在信号采集和分配的过程中,仅需对有用信号进行采集,所以利用检测到SAV作为一个标志,启动信号的分配过程是非常有必要的。

由于YUV信号在模拟信号中是交织着的,所以需要一个信号选择电路。YUV一共是三路信号,设计一个计数器进行选择,计数是O和2时,是UV信号,计数是1和3时是Y信号,完成的实际上是串行信号转并行信号的过程。以上过程可以用图3的原理框图来表示。

图3 YUV信号的采集、分配原理图

在硬件描述语言中,完成上述过程还是比较简单的。例如检测电路,只要描述一个移位寄存器就可以了,具体代码如下:

其中的wire变量Y_check就是当检测到FF,00,00的时候就为1的标志。根据上文所述,区分SAV和EAV是根据XY来决定,区分奇偶场是根据XY来区分,所以只有随后的信号是SAV的时候,信号分配电路才有效,所以需要描述一段逻辑来判断,代码如下:

START信号就是开始信号采集、分配的标志,只有当TD_D=0也就是START= 1时信号分配电路才会工作。串转并电路代码如下:

以上代码完成了图3的功能,输入的信号名为TD_D,输出的三路信号是Cbb,YY,Crr。注意到还有个YPix_clock,实际上是27M的2分频,这个时钟非常有用,在下面将详细阐述。

2.2 YUV信号的存储

要将视频信号隔行变逐行,有2 种解决方法:

第1种:将一帧的数据存储下来,根据奇偶场的不同(区分可以根据XY),在写周期的时候,因为奇场的行之间有偶场的信号,所以写数据的时候需要跳地址写,根据行同步信号(或者SAV也可以)来区分行,换行的时候地址要加额外的720(用来存放夹杂在奇场信号中的偶场信号),直到出现偶场信号(也就是XY=1)地址切换为初始基地址加720,其余的同奇行的处理方法,具体的地址分配表参照图4。

图4 地址分配表

在读周期只需要按照顺序读出就可以了,需要注意的是写时钟是13.5M,读时钟是27M,而且对于Y、U、V信号要进行分别存储。

第2种:将一行的数据存储下来,因为1716个时钟周期刚好等于VGA两行的时间,所以在这段时间里可以将7加个有效视频信号读取2遍,以奇行的信号去取代偶行的信号,达到隔行变逐行的目的。在实现上只要是两个RAM块进行乒乓操作就可以了,具体在后文阐述。

比较两种实现方法,方法1的优点在于图像没有失真,即奇偶行信号依旧相间在一起,方法2却不能做到这一点,而且方法1也可以通过乒乓方式提高运行的速度,但是由于读写时钟的不同步,每个存储空间应当读2遍。方法2也是读2遍,但是是每行读2遍,方法1是一帧数据读2遍。

方法1的缺点在于存储的数据量太大。一帧数据仅Y分量就是8bit*720*525=3024000bit=378KB,这个数据是不适合在SRAM中操作的,需要使用SDRAM,而操作SDRAM是比较复杂的,所以一般考虑使用方法2,因为它需要很小的空间,而且可以利用FPGA的片内资源就可以实现。当图像数据传输很快的时候,人眼基本上是分不清奇偶场信号的,所以方法2是可行的。在讲方法2之前,需要了解在流水线操作中经常使用的乒乓操作,这是可编程逻辑常用的设计思想和技巧。乒乓操作常常应用于数据流控制,典型的乒乓操作如图5所示。

图5 乒乓操作示意图

乒乓操作的处理流程描述如下:输入数据流通过“输入数据流选择单元”,等时地将数据流分配到两个数据缓冲模块。数据缓冲模块可以是任何存储模块,比较常用的存储单元是双口RAM ( DPRAM ),单口RAM ( SPRAM)和FIFO等。在第一个缓冲周期,将输入的数据流缓存到“数据缓冲模块1”。在第2个缓冲周期,通过“输入数据流选择单元”的切换,将输入的数据流缓存到“数据缓冲模块2”,与此同时,将“数据缓冲模块1”缓存的第1个周期的数据通过“输出数据流选择单元”的选择,送到“数据流运算处理模块”被运算处理。在第3个缓冲周期,通过“输入数据流选择单元”的再次切换,将输入的数据流缓存到“数据缓冲模块1”,与此同时,将“数据缓冲模块2”缓存的第2个周期的数据通过“输出数据流选择单元”的选择,送到“数据流运算处理模块”被运算处理。如此循环,周而复始。

乒乓操作的最大特点是,通过“输入数据流选择单元”和“输出数据流选择单元”按节拍、相互配合的切换,将经过缓冲的数据流没有时间停顿地送到“数据流运算处理模块”,被运算和处理。把乒乓看成一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进行流水线式处理。所以乒乓方式常常应用于流水线式算法,完成数据的无缝缓冲与处理。

在FPGA里面,使用乒乓操作是面积与速度互换原则的一个体现。

方法2 可以这样实现:在FPGA内部使用Megacore,构造一个双口的RAM,双口RAM的输入输出信号的硬件描述语言定义如下:

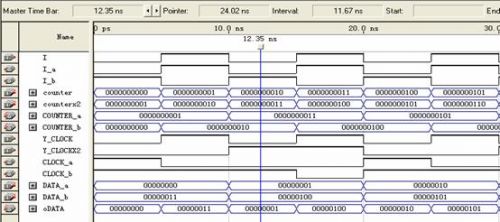

使用的信号包括:数据信号data_a,dat_b;读写有效信号wren_a,wren_b;地址信号address_a,address_b;时钟信号clock_a,clock_b;输出数据信号q_a,q_b。可以看到所有的信号都是成对出现的,就是为了进行乒乓方式的数据传输。分成了两个RAM区域,A和B,相当于前面讲乒乓方式里的数据缓冲模块1和2。两个RAM块是交替着读写(由I_a和I_b决定),输出数据流也是由I决定。刚说到写时钟是13.5M,读时钟是27M,所以clock_a和clock_b必须是读写时钟切换着输入,而且地址的计数也不一样,写周期时候地址增加的时钟是13.5M,读周期地址增加的时钟是27M。所以每行的数据读了两遍,相当于隔行变逐行。图6在Qartus II下RAM的乒乓操作功能仿真图:

图6 RAM的乒乓操作仿真图

RAM块进行乒乓方式操作信号的分配表如下:

最后输出的DATA信号进入下一级单元,即YUV到RGB的转换。

2.3 颜色-空间转换部分设计

为什么要有这个转换呢?因为不论是电视机还是CRT显示器,都是使用RGB三基色合成的方法来显示颜色。用RGB三基色来表示彩色的确很直观,但是如果把这种方法用作图像传输则绝不是一个好方法。主要是因为:

(1)与黑白图像不兼容;

(2)占用太多带宽;

(3)抗干扰能力差。

本系统图像传感器输出YCbCr信号,需要进行到RGB信号的转换,用于CRT显示。YCbCr到RGB按照下面公式进行转换:

R = 1.164 ( Y-16 ) + 1.596 ( Cr-128 );

G = 1.164 ( Y-16 )- 0.813 ( Cr-128 ) - 0.392(Cb-128);

B = 1.164 ( Y-16 ) + 2.017 ( Cb-128 );

观察上面公式可以发现,转换均需要乘加运算,并且式子中用到了小数,所以必须要对系数进行放大。经过合理转化,公式如下:

R = (1/256) * ( 298*Y + 409*Cr - 57065 );

G = (1/256) * ( 298*Y - 100*Cb - 208*Cr + 34718 );

B = (1/256) * ( 298*Y + 516*Cb - 70861 );

用Verilog HDL编写代码,实现YUV到RGB的转化。其中共包括3个模块跟1个仿真激励。在模块const_mult中,主要实现乘法运算,主要代码如下:

模块csc.v中,调用const_mult模块,通过参数传递改变参数IN_SIZE,OUT_SIZE,CST_MULT的值,然后实现加法运算。

以R = (1/256) * ( 298*Y + 409*Cr - 57065 )为例,主要代码如下:

用以实现G、B的代码与上面类似,在此不再赘述。以下代码实现R_full*1/256功能。

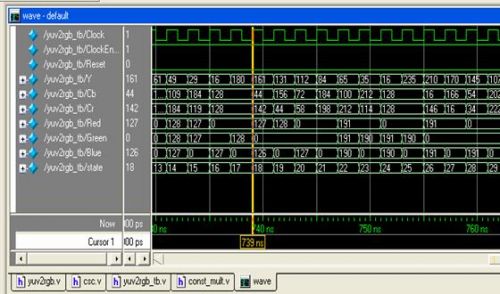

主模块yuv2rgb实现子模块的调用,用Modelsim进行了仿真。仿真波形如图7所示:

图7 YUV到RGB的转化仿真图

3 结论

本文设计了基于SOPC">SOPC的视频编解码控制器IP核,根据自顶向下的设计思想,将IP核进行层次功能划分,并对IP核的仿真验证,实现了视频信号的采集,分配,存储以及色度空间的转换。本IP核具有很好的移植性,可以方便的应用到以Nios II为核心的各种需要视频编解码控制器功能的嵌入式中。