微型星载GPS接收机硬件设计

2007-12-05

作者:包鼎华

摘 要:本文介绍了清华宇航中心航天GPS 接收的硬件设计,给出了测试结果和分析。

关键词:航天GPS接收机 硬件设计 GP4020 基带处理器

微小卫星具有成本低、性能好、研制周期短、重量轻、体积小等优点,但整星功耗也受到限制。GPS接收机用于微小卫星,能够测定微小卫星的航迹、姿态、时间参数及编队飞行的微小卫星间的相对距离,能够减少传感器数量,增强微小卫星的在轨自主运行能力,显著降低微小卫星的成本、功耗、重量,已成为微小卫星星载" title="星载">星载导航系统的最佳选择。目前国内市场上GPS接收机的使用高度和速度有限制,不满足航天应用;国外航天GPS接收机也多是单件小批生产,价格昂贵,而且存在禁运问题。基于上述原因,开展航天GPS 接收机设计与研究工作十分必要。

1 主要部件

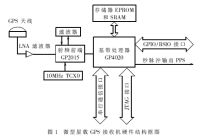

微型星载GPS接收机在硬件设计上选用Zarlink公司的基带处理芯片GP4020和射频芯片GP2015,其硬件设计框图如图1所示。

GPS接收机的硬件部分包括射频前端、基带处理器和外围芯片。射频前端包括从天线到数字处理器之间的所有部件,基带处理器则包括了相关器" title="相关器">相关器单元和嵌入式处理器单元,而外围芯片则为各种存储器和通信接口。

GPS射频前端的功能包括放大、下变频、滤波、自动增益控制和本地振荡信号发生器。GPS卫星发射的C/A伪码以1.023MHz的码率调制在1575.42MHz的载波信号上,到达天线的卫星信号功率大约为-130dBm,深埋于热噪声电平之下(-114dBm/MHz),因此射频前端必须将GPS信号放大到某一电平之上,使得该信号能够为基带处理器所利用。射频电路" title="射频电路">射频电路还必须将1575.42MHz的载波下变频到基带处理器的工作频率范围之内,一般需要采用二级或多级下变频。除接收GPS信号外,射频电路还需要对噪声信号进行抑制。

GPS基带处理器包括两个部分:进行数字信号处理的相关器单元和进行导航应用计算的嵌入式处理器单元。相关器单元对射频前端经过下变频后输出的中频信号进行采样和接收,并通过数字的频率锁定环去除载波的多普勒频移将数字中频信号转化为基带信号。基带信号与本地伪码发生器产生的C/A伪码相关,并通过数字的延迟锁定环精确测量GPS信号的传播路径所导致的伪码的相位延迟,转换为用于导航应用计算的伪距量。中频信号经过相关器单元移去多普勒频移和C/A伪码后,嵌入式处理器可以获得码率为50Hz的GPS导航信号,其中包含卫星轨道信息、健康状态和误差校正参数等。嵌入式处理器对获得的GPS导航信号进行解码,计算出GPS卫星的位置和速度参数。基于GPS卫星的位置信息和卫星与接收机之间的伪距量,嵌入式处理器可以计算出接收机的位置、速度和时间参数。

1.1 GP4020基带处理器

GP4020是基于Zarlink公司的Firefly MF1微处理器内核和12通道伪码扩谱相关器的全数字式基带处理芯片。作为该公司的第二代GPS芯片,它把一个与GP2021相关器芯片功能一致的相关器单元和一个ARM7TDMI微处理器单元集成在一起,以降低系统功耗和成本,提高系统性能。

相关器单元共有12个相关通道,每个通道都含有相同的跟踪模块。相关通道除了含有捕获和跟踪GPS信号所需的所有元件外,还含有用于产生部分测量数据的其他功能模块。在必要时,相关器单元还可以关闭部分通道,以降低系统功耗和处理器负载。

1.2 GP2015射频前端芯片

GP2015是应用于GPS接收机的小型射频前端芯片,它与GP2010射频前端芯片的性能相同,但用TQFP封装,适合于体积要求比较小的GPS接收机的设计。GP2015将天线接收到的且通过低噪声放大器的1575.42MHz信号经过三级变频变到中频4.309MHz,得到2位的数据流。GP2015正常工作时需要有源天线增益大于+16dB。

2 硬件设计

GPS接收机硬件设计主要包括射频电路设计和数字电路" title="数字电路">数字电路设计。

2.1 射频电路设计

2.1.1 GPS天线的选择

根据所设计星载GPS接收机的航天应用特点,选择Micropulse1621LW GPS无源天线,其特点是简单、坚固、体积小,适合于安装在微小卫星上,但需要进行低噪声前置放大器的设计。

2.1.2 低噪声前置放大器的设计

微型星载GPS接收机的低噪声前置放大器采用AM50-0002低噪声放大器进行设计,可以直接做在射频电路板上,也可以与Micropulse1621LW GPS无源天线做成一体,以降低馈线损耗。AM50-0002的特性参数如下。

2.1.3 射频前端电路设计

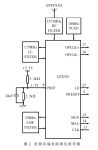

射频前端电路主要由GP2015和外围电路构成,其简化原理图如图2所示。

经低噪声前置放大器放大和滤波后的射频信号(1575.42MHz)与锁相环频率合成器产生的第一本振信号(1.4GHz)混频,经滤波后得到差频信号(175.42MHz);该信号与第二本振信号(140MHz)混频,经过声表面滤波器中心频率选择得到差频信号(35.42MHz);该信号经两个自动增益控制器(AGC)放大后,与第三本振信号(31.11MHz)混频,经低通滤波器选出中频信号(4.309MHz);该中频信号随后进入A/D转换器由5.714MHz的采样频率进行二值量化,转换为1.405MHz的二位数字信号——符号(SIGN)和模(MAG),分别表示输出信号的极性和幅值。最终输出的数字中频信号(1.405MHz)供后续的数字电路进行信号处理。

下面介绍射频前端的外围电路设计。

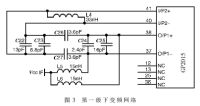

(1)第一级中频滤波器

第一级外置中频滤波器位于第一级混频器" title="混频器">混频器和第二级混频器之间,要求它能够滤除第二级中频在第一级中频的镜像频率104.58MHz(140-35.42MHz),这个频率对应的射频输入频率为1504.58MHz。这些射频镜像频率在前面的GPS天线和射频滤波器被滤掉一部分,在第一级中频滤波器则被进一步滤除。

这一级滤波器的插入损耗最大不能超过3dB,否则GPS接收机的增益将不足以让第三级混频器中的AGC电路正常工作。这一级滤波器同时还要抑制干扰信号电平,以免影响第二级混频器。

GP2015第一级混频器输出需要一个外置直流偏置以获取最大的中频信号处理空间。所以第一级中频滤波器包含一个直流偏置连接到VCC,这可以通过上拉电感来实现。由于从第一级混频器到第二级混频器的信号必须通过交流偶合,所以这一级滤波器电路可以设计成一个电感电容滤波网络,如图3所示。

用这种方式设计的滤波电路能够滤除位于混频输出的绝大多数本振和射频信号。但是这一部分的PCB图的元件布局要求非常严格,需要精心设计。因为这一部分的元件间隙的任何变动都可能产生元件间的寄生振荡现象。同理,这些元件间的连接导线也需要精心安排,而且设计时要考虑在这一部分滤波器和射频信号输入电路之间留有足够的空间,以实现相互隔离,保证系统的稳定性。

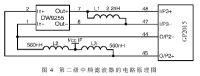

(2)第二级中频滤波器

这一级中频滤波器位于第二级混频器的输出端和第三级混频器的输入端之间,它的频率特性对整个射频前端乃至整个GPS接收机的性能的影响都非常大。本 设计采用Zarlink公司生产的专用滤波器DW9255。它是一种声表面波(SAW)带通滤波器,性能优良,以35.42MHz为中心频率,1dB的衰减带宽为1.9MHz,插入损耗仅为17dB±1dB。当滤波器的输入输出端匹配好以后,它能达到的滤波器性能在±2.0MHz时优于21dB,在±7.5MHz时优于35dB。这个性能指标远远优于设计指标。

第二级中频滤波器的电路原理图如图4所示。

(3)第三级中频滤波器

第三级中频滤波器为GP2015的片上滤波器,中心频率为4.3MHz。GPS接收机总的射频带宽由第二级中频滤波器定义,第三级中频滤波器用于防止带外噪声和干扰信号进入A/D转换器。

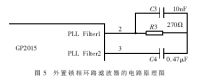

(4)外置锁相环滤波器

GP2015采用内置锁相环的方式产生本地振荡频率以供各级变频的需要,其锁相环滤波器是外置的。锁相环滤波器为低通滤波器,通过它来取出其中缓慢变化的直流电压分量来控制压控振荡器(VCO),将环路控制在锁定状态。

外置锁相环路滤波器采用二阶低通滤波器,滤波器参数和电路原理图如图5所示。

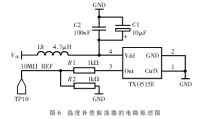

(5)基准振荡器

GPS接收机几乎所有频率和时钟信号(除了数字电路部分的RTC实时时钟)本质上都来自于基准振荡器,因而基准振荡器的选择对于GPS接收机的性能影响非常重要。

微型星载GPS接收机的基准振荡器采用温度补偿晶体振荡器TXO515E,在室温下的频率稳定度为1.5ppm,具体的电路设计如图6所示。

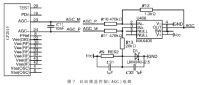

(6)自动增益控制(AGC)电路

GP2015采用部分内置的自动增益控制(AGC)电路,AGC电路的设计如图7所示。

自动增益电路是GPS接收机必不可少的控制电路之一。这是因为GPS接收机工作时,其输出功率是随外来信号强度的大小而变化的。GPS接收机所接收到的信号强度随各种条件的变化,其变化范围可从几毫伏到几百毫伏,但GPS接收机输出电平的变化范围应尽量小。如果信号过强,将使晶体管和终端器件过载以致损坏;如果信号过弱,GPS接收机又可能无法正常工作。因此,必须采用AGC电路来自动控制GPS接收机的增益。

AGC电路能够实现当输入信号电压变化很大时,GPS接收机的输出电压基本保持不变。为了实现这个功能,必须有一个随外来信号强度而改变的电流或电压来控制相关的增益。实际设计时,可使用一个外置电容(100nF),通过判断该电容上的电压大小来确定信号的强弱。在调试时也可以通过检测此电容上的电压变化来判断AGC电路是否工作正常。

2.2 数字电路设计

微型星载GPS接收机的数字电路部分主要以Zarlink公司的基带处理器GP4020为核心进行设计。数字电路的设计工作主要包括接口设计、电源设计和存储设计。数字电路的设计分为:输入输出接口设计、射频电路接口设计、调试接口设计和电源设计。下面介绍数字电路设计的各个部分。

2.2.1 输入输出接口电路设计

微型星载GPS接收机一方面从外部获得5V的输入电源VIN,另一方面又可通过RS232与计算机终端通信。此外,GPS OEM标准接口所定义的通用输入输出管脚和保留管脚还可以用来输入输出GPIO信号和一些调试信号。其余的管脚定义还包括复位管脚、电池管脚和实时时钟输入输出管脚等。

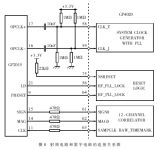

2.2.2 射频电路接口设计

数字电路部分与射频电路的接口包括:射频电路的电源、40MHz的差分时钟信号、5.714MHz采样信号、射频功率监控信号、射频PLL锁定指示信号和二值量化数字信号等。

射频电路和数字电路的连接关系如图8所示,GP4020内部的系统时钟发生器接收来自GP2015的40MHz差分时钟信号CLK_T和CLK_I,产生相关器、Firefly MF1微控制器和总线等的时钟信号。

GP2015的LD信号接入GP4020的RF_PLL_LOCK管脚,当LD管脚由低变高时,表示射频前端锁相环路处于锁定状态,40MHz差分时钟信号已经稳定。

GP2015的PRESET信号接入GP4020的Power_Good管脚,指示当前电源的状态,高为正常,低则迫使GP4020进入调电模式。

GP2015的SIGN和MAG信号分别接入到GP4020的SIGN0和MAG0管脚,将数字中频信号输入到相关器。

GP4020的SAMPCLK信号接入到GP2015的CLK管脚,将5.714MHz的采样信号输出到GP2015,对4.309MHz的中频信号进行二值量化。

2.2.3 JTAG接口电路设计

GP4020的Firefly MF1微控制器内置了三种成熟的软件和硬件调试方案,分别为:

(1)嵌入式在线仿真器(ICE),通过ARM7TDMI的JTAG接口访问;

(2)Angel调试监视器;

(3)逻辑分析仪结合反汇编工具,通过SSM调试接口访问。

微型星载GPS接收机设计时采用了嵌入式ICE作为调试接口,其JTAG接口电路设计如图9所示。在GP4020芯片中,通过NICE管脚(84)选择ARM7TDMI的工作模式,高为正常模式,低为ICE模式。

2.2.4 电源电路设计

数字电路部分的电源设计实际上也包括了射频电路的电源设计,其电路原理如图10所示。数字电路从外部的GPS OEM 标准接口电路获得5V的电源输入VIN,并使用电源芯片MAX1692将5V的输入电压转换成3.3V电压分别供应数字电路和射频电路。其中射频电源VCC通过射频接口输出给射频电路,而VDD和VBAT则为数字电路电源。VBAT与VDD的区别在于它增加了锂电池充电电路的设计,可以在接收机断电时继续使用3V锂电池供应GP4020,以保存GP4020内部SRAM中的重要数据。

3 设计结果

本微型星载GPS接收机为双板接收机,射频电路板和数字电路板分别进行设计和制造,再通过螺栓螺母将两个电路板固定为一体,并采用专门设计的接口连接两部分电路。微型星载GPS接收机的电路原理图和PCB图都采用了Protel99se软件进行设计和绘制,选用器件基本上为表面贴器件。

射频前端电路的器件布置在四层PCB板上,单面布置器件。

数字电路的器件布置在六层PCB板上,双面布置器件。

4 测试结果及分析

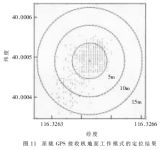

测试定位时间为80秒。冷启动情况下,该指标与接收机搜索GPS卫星顺序及GPS卫星可视情况有关。接收机首先分配12个相关器通道搜索PRN1到PRN12卫星,当这些卫星多于3颗可见时,在约30秒时就能实现定位解算。定位结果如图11所示。

伪距速度的捕获范围与应用软件中设定的±35kHz的多普勒频率搜索范围吻合;

PLL载波跟踪环路动态特性差,能够跟踪的最大加速度是3g;

FLL载波跟踪环路动态特性好,能够跟踪的最大加速度为50g;

5 工作展望

当前,系统已经具有完整的接收机硬件和软件平台,且已经能够在地面应用情况下良好工作。针对航天应用,还将进行如下工作:

(1)验证卫星在轨高速运动情况下的接收机捕获跟踪解算功能;

(2)改善定位算法,提高定位精度;

(3)热循环、热真空、振动试验、抗辐射的考虑等。

参考文献

[1] GP4020 GPS baseband processor design manul.Zarlink (Mitel) Semiconductor Company,http://www.zarlink.com

[2] GP2000 GPS receiver hardware design.Zarlink(Mitel) Semiconductor,http://www.zarlink.com

[3] ARM Limited.ARM software development toolkit version 2.50 reference guide.