CAN总线与一般的串行通信总线相比,它的数据通信具有可靠性高,实时性高,灵活性强等优点,不仅广泛应用于汽车行业,而且扩展到了机械工业、机器人、数控机床等诸多领域。尤其在大量数据通信处理中,高可靠性及实时响应的场合,单通道CAN总线不能满足实际通信的要求。为此,介绍一种基于多通道实时CAN模拟器的设计方案。

1 CAN总线技术介绍

1.1 CAN总线特性

CAN(Controller Area Network)总线是一种串行多主站控制器局域网总线。它具有很高的网络安全性、通信可靠性和实时性,并且简单实用,网络成本低。它主要用于各种过程监测及控制的一种网络。CAN最初是由德国BOSCH公司为汽车的监测、控制系统而设计的。由于CAN总线具有卓越的特性和极高的可靠性,特别适合于工业过程中监控设备的互连。

1.2 CAN通信协议

在CAN 2.0B的版本协议中有两种不同的帧格式,不同之处为标识符域的长度不同,含有11位标识符的帧称为标准帧,而含有29位标识符的帧称为扩展帧。扩展格式是CAN 2.0B协议新增加的特性。在报文传输时,不同的帧具有不同的传输结构,只有严格按照该结构进行帧的传输,才能被节点正确接收和发送。下面将分别介绍四种传输帧的结构:

(1)数据帧(Data):数据帧将数据从发送器传输到接收器。CAN协议有两种数据帧类型标准2.0A和标准2.0B。两者本质的不同在于ID的长度不同。在2.0A类型中,ID的长度为11位;在2.0B类型中,ID的长度为29位。它由7个域组成:帧起始、仲裁域、控制域、数据域、CRC校验码域、应答域、帧结束。

(2)远程帧(Remote):总线单元发出远程帧,请求发送具有同一标识符的数据帧。接收数据的节点可通过发远程帧请求源节点发送数据。它由6个域组成:帧起始、仲裁域、控制域、校验域、应答域、帧结束。

(3)错误帧(Error):任何单元检测到总线错误就发出错误帧。由错误标志和错误分界两个域组成。接收节点发现总线上的报文有误时,将自动发出“活动错误标志”,其他节点检测到活动错误标志后发送“错误认可标志”。

(4)过载帧(Overload):过载帧用在相邻数据帧或远程帧之间提供附加的延时。由超载标志和超载分隔符组成。超载帧只能在一个帧结束后开始。当接收方在接收下一帧之前,需要过多的时间处理当前的数据,或在帧间空隙域检测到显性电平时,则导致发送超载帧。

1.3 CAN协议控制器

目前主流的CAN协议控制器一般采用I/O总线(SJA1000等)或SPI接口(M(2P2515等)与处理器进行通信。该设计采用SJA1000控制器。

SJA1000是一款独立CAN控制器,应用于移动目标和工业局域网控制领域。SJA1000具有两种工作模式:BasicCAN和PeliCAN。该设计采用PeliCAN工作模式。SJA1000用来完成CAN协议所规定的物理层和数据链路层的所有功能,它可以支持多种处理器的时序特性,如Intel模式或Motorola模式,与微处理器的接口非常简单,微处理器以访问外部存储器的方式来访问SJA1000。

SJA1000通过CAN控制器接口即PCA82C250芯片接到CAN总线上。CAN收发器使用飞利浦公司的PCA82C250,它是连接CAN控制器和物理总线之间的接口,提供了对总线的差动发动和接收能力,与ISO11898标准完全兼容,有三种不同的工作方式即高速、斜率控制和待机,可根据实际情况选择。硬件电路中使用PCA82C250是为了增加通信距离,提高系统的瞬间抗干扰能力,保护总线,降低干扰等。2 系统设计

2.1 系统方案设计

根据通用计算机的总线分类,可采用基于ISA总线对多通道实时CAN总线模拟器进行研制,根据CAN总线通信原理可以提出以下两种设计方案:

(1)ISA总线+CAN通信控制器;

(2)ISA总线+微处理器+CAN通信控制器。这两种设计方案的不同点在于是否采用处理器来加强控制。

由于CAN总线通信要求实时性高,再加上多通道的设计满足实际的需要,故采用单片机来负责CAN总线的通信功能。在这里主要介绍单片机与CAN控制器之间的设计部分,其系统设计框图如图1所示。

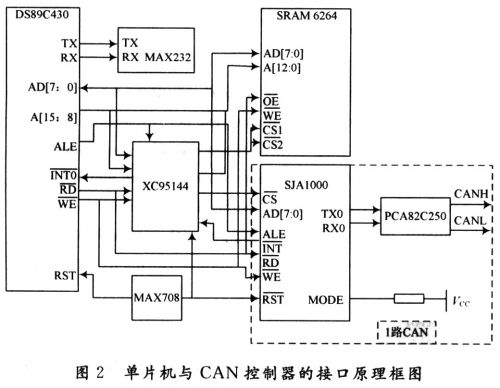

单片机选用DALLAS公司的DS89C430,它是当前8051兼容微控制器中性能最高的。具有重新设计的处理器内核,在相同的晶振频率下,执行指令的速度是最初8051微处理器的12倍。特性:高速8051架构,每个机器周期一个时钟;片内存储器16 KB/32 KB/64 KB闪存,在应用可编程,通过串口实现在系统可编程;与8051引脚和指令集兼容;四路双向、8位I/O端口;三个16位定时器/计数器;256 B暂存RAM等特点。可根据实际应用的需要选择其部分功能。随着可编程逻辑器件的飞速发展,其应用领域不断扩大,可用于译码、解码等方面,使用CPLD可以提高系统集成度,降低噪声,增强系统可靠性。因此,单片机与CAN控制器之间的锁存、译码采用Xilinx公司XC95144CPLD芯片,优化了系统资源,降低了其功耗。

2.2 系统硬件设计

该部分由单片机、CAN控制器、CAN收发器、SRAM存储器组成。单片机主要用于系统计算及信息处理等功能;CAN控制器主要用于系统通信;CAN收发器主要用于增强系统的驱动能力;SRAM主要用于缓存数据。系统的发送过程是:单片机将外围设备传送过来的信息处理后,按CAN规范规定的格式,将其写入CAN控制器的发送缓冲区,并启动发送命令,把数据发送到CAN总线上;接收过程是:CAN控制器从CAN总线上自动接收数据,并经过滤后存入CAN接收缓冲区,且向单片机发出中断请求,此时单片机可从CAN接收缓冲区读取要接收的数据。SJA1000提供的微处理器接口方式为典型INTEL或MOTOROLA地址数据多路复用总线模式。主要信号有地址数据信号AD7~AD0,地址选通信号ALE,片选信号CS,读信号RD,写信号WR,模式选择信号MODE。当MODE=1时,为INTEL模式;当MODE=0时,为MOTOROLA模式。后面描述的总线模式均为INTEL模式。AD7~AD0引脚在ALE有效时,传送的是地址信号,在RD或WR有效时,传输的是数据信号,在这里分别与单片机的PO口相连,RD,WR信号线分别与单片机的读/写信号线相连。具体方案如图2所示。限于篇幅限制,虚线内给出1路CAN的连接图,2路CAN有同样的连接方法。

SRAM和CAN控制器的片选信号。由于单片机可以查询或中断方式访问,在此采用中断方式进行CAN多通道选择访问,以满足不同通信速率下数据处理的需要。SRAM的地址线与数据线是分开的,故采用74LS373锁存器实现锁存功能。可采用XC95144CPLD芯片以及VHDL硬件描述语言以实现锁存、译码等功能。

2.3 CPLD设计部分

2.3.1 结构设计

CPLD的输入信号是单片机发送的信号,由高位地址A[15..8]、ALE锁存信号、中断信号以及写/读信号组成。地址线A14和A15经译码后作为片选信号,ALE实现低8位地址线的锁存。实体和构造体部分代码如下所示:

2.3.2 仿真结果

该模块在Xilinx ISE 9.1工具下进行综合,并在结合ModelSim环境下进行功能仿真。其仿真结果如图3所示。

3 软件设计

该系统软件设计的关键是通信程序设计。通信软件由三部分组成:单片机和CAN控制器的初始化程序、CAN发送程序、CAN接收程序。对于初始化程序,采用MAX232芯片对单片机进行在线编程,可同时对多通道CAN控制器初始化。对于CAN控制器的初始化程序,主要是通过对CAN控制器控制段中的寄存器写入控制字,从而确定CAN控制器的工作方式等,即通过上电复位、硬件复位或软件复位给CAN控制器发一个复位请求,便可进入初始化。在复位期间,对必需的寄存器进行设置。对于发送和接受程序,只需把到来的信息帧送到CAN的发送或接受缓冲区,同时启动命令即可。二者可采用查询方式或中断方式,对于中断方式,程序分为主程序和中断服务程序两部分设计。在具体项目中,需要软硬件结合调试才能保证各部分的设计准确无误,到达实际应用的要求。

4 结 语

在对CAN通信协议进行分析的基础上,构建了一种多通道实时CAN总线模拟器架构,同时利用CPLD器件,通过功能仿真,验证了设计方案的正确性。经实际工程项目使用,验证了该设计方案切实可行,满足了实际应用中高可靠性、高实时性以及传输速率较高的需求。