ZL10036的工作原理及其典型应用

2007-12-07

作者:张 曦,梁世光,范庆元

摘 要:介绍了数字卫星调谐芯片ZL10036的内部结构及工作原理,研究了其应用的主要问题,实现了其在射频至基带转换器中的应用。

关键词:ZL10036 下变频 I2C总线 电荷泵" title="电荷泵">电荷泵锁相环 射频至基带转换

随着数字卫星和无线通信技术的迅猛发展,面向专用系统的射频集成芯片的种类越来越多,集成度也越来越高。从某种程度上说,一个完整的无线通信系统射频模块的构建过程,已经变成对不同芯片的选择与使用的过程。因此,射频系统性能的优劣很大程度上取决于所选核心集成芯片的性能。ZL10036是卓联(ZARLINK)半导体公司生产的一款用在数字卫星信号接收机中的进行直接下变频的射频芯片。在本文所述的应用中,该芯片被用来作为一台射频至基带转换器的核心部件。本文在介绍这款芯片特点的同时,将围绕它在射频至基带转换器中的具体应用做详细研究。

1 芯片ZL10036

ZARLINK半导体公司的数字卫星调谐芯片ZL10036是一个单片宽带直接变频调谐器,它提供高度集成的卫星调谐器功能。内部集成有I2C串行总线接口控制器,低相位噪声PLL频率合成器" title="频率合成器">频率合成器,正交相位分离调谐器,全集成的本地振荡器和可调带宽的基带低通滤波器。包括PLL频率合成器,芯片增益和基带带宽在内的所有芯片功能都通过I2C串行总线接口实现控制。此外,ZL10036对相邻信道有良好的隔离度,提供了一个可供选择的射频旁路,总线接口可与3.3V的逻辑电平兼容,具有降功耗模式等特点。

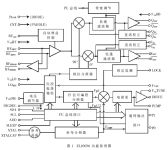

ZL10036功能原理框图如图1所示,可以分为RF信号处理部分(图1上半部分)和PLL频率合成器(图1下半部分),此外还有芯片的逻辑控制寄存器部分(图1中未画出,见图3)。

1.1 RF信号处理部分

RF信号处理部分主要由前置增益可调放大器、两个线性度高的混频器、两个带宽可调的基带滤波器、自动增益调控模块(AGC SENDER)、直流偏移校正(DC CORRECTION)模块组成。

射频信号经过良好的阻抗匹配由差分输入端口RFINPUT和/RFINPUT进入芯片,输入至前置放大器级,然后分为两个通道,分别与正交的两路本振" title="本振">本振信号混频,下变频至基频,然后分别通过带宽可调(4~40MHz)的基带低通滤波器,再经差分放大器放大后分别输出QOUT,/QOUT和IOUT,/IOUT两路正交的差分基频信号。

整个通路的增益控制设计非常有特点,可分为模拟RF AGC、RF数字控制增益、基带前置滤波器和基带后置滤波器四个部分(图1只表示出第一部分),增益的控制非常灵活和方便。其中模拟RF AGC增益是连续变化的(0~72dB),由AGC SENDER实现控制;RF数字控制增益是一个0dB、4dB二选一的增益开关,由芯片内部逻辑位RFG的高低来实现控制;基带前置滤波器和后置滤波器的增益均为0~12.6dB,步长为4.2dB,分别由芯片内部逻辑位BA1、BA0和BG1、BG0来实现增益选择控制。

基带滤波器的带宽可以根据用户的需要在4~40MHz范围内连续调整,也可通过I2C总线设置逻辑位BF1-BF6和BR0-BR5来实现。

ZL10036芯片中还带有放大器的直流偏移校正电路。它通过一个内置的偏置矫正反馈放大器消除放大器的直流偏移。在放大器的增益达到饱和状态时,直流偏移会影响放大器的工作点而影响非线性性能。但是,偏移校正电路中的时间常数会影响芯片的上电时间,所以在对上电时间要求比较严格的情况下,可以通过外接交流短路电容来禁用偏移校正功能[4]。

1.2 PLL频率合成器部分

ZL10036芯片中用于与射频信号混频的本振信号由芯片内电荷泵锁相环(CPPLL)频率合成器产生。在电荷泵锁相环中,鉴频鉴相器与电荷泵相结合使得采用无源环路滤波器" title="环路滤波器">环路滤波器的电荷泵锁相环理论上能产生无限的直流增益和无穷大的频率牵引范围,并且获得零静态相位误差[2][3]。

ZL10036中所采用的整数分频" title="分频">分频频率合成器结构是一种最基本的电荷泵锁相环结构,其结构如图2所示,包括由晶体振荡器产生的参考时钟、鉴频鉴相器、电荷泵、环路滤波器、压控振荡器、可编程分频器。鉴频鉴相器比较两个信号的相位与频率差,并且产生up和down的控制信号给电荷泵,电荷泵相应地给环路滤波器充放电,压控振荡器的输出频率正比于环路滤波器上的控制电压,最终使参考时钟与可编程分频器输出信号同频同相,从而压控振荡器的输出信号频率为参考时钟信号频率的N倍,N为芯片内15位可编程分频器的分频比。

ZL10036芯片中除了环路滤波器和参考时钟需要外接之外,其他所有构成电荷泵锁相环路的组成部分都已经集成在片内。其中外接环路滤波器采用无源一阶低通滤波器,而参考时钟信号由外接晶体振荡器电路产生的振荡信号经过芯片内的参考分频器(REFERENCE DIVIDER)分频后得到。

15位可编程分频器和参考分频器的分频比,以及电荷泵的最大电流均通过I2C总线设置芯片相关逻辑位实现控制。此外,压控振荡器组的工作也由I2C总线根据分频比的设置情况实现自动控制,不需要人为干预,非常方便。

1.3 逻辑控制部分

ZL10036芯片内有13字节的寄存器空间,用户可以通过对这些寄存器进行写操作实现对芯片的控制和芯片工作参数的设置。还可以对这些寄存器进行读操作以监视芯片的工作。

下面对ZL10036的13个寄存器的功能和设置做一个简单和必要的介绍,图3是ZL10036寄存器映像表。

字节1:芯片地址字节,用于总线对芯片寻址。

字节2,3:PLL频率合成器15位可编程分频器分频比的控制位。

字节4:LEN为射频旁路功能使能位;BG0和BG1为基带后置滤波器增益控制位;BA0和BA1为基带前置滤波器增益控制位;RFG为RF数字控制增益的控制位。

字节5:R0~R4为参考分频器分频比的设置位;C0和C1为电荷泵最大电流控制位;P0为通用输出端。

字节6:RSD为基带滤波器电阻转换使能位。为了改善I、Q两通道的带宽和相位的同步,基带滤波器使用了电阻转换技术(resistor switching technique),滤波器中使用不同的电阻值把滤波器基带带宽分成了三个子带,当带宽设置正好处于3个子带的2个交点处时,带宽的准确性可能会下降。这个问题可以通过使用RSD位禁止电阻转换来解决:每当芯片上电时,RSD位默认为0,电阻转换可用,芯片根据用户设置的带宽自动选择合适的电阻值,然后用户置RSD为1,禁用电阻转换,使其固定在已选值。

字节7:BF1~BF6用来调节基带滤波器的带宽,其取值为0~62(63无效),与BR0~BR4(见字节13)共同确定基带滤波器带宽;P1是通用输出端。

字节8~10:其上电值分别为0xDB、0x30、0xE1,初始化时应按硬件的要求分别置为0xD3、0x40、0xE3。

字节11:初始化时要用0x5B、0xF9写入两次,写入的顺序可以改变。

字节12:仅供测试用。

字节13:TL为缓冲本振输出选择位,此位为1,用于测试目的的本振信号会从LOTEST脚输出,此位上电值为0;CLR位是控制逻辑重置位;BR0~BR4,取值为4~27(其他数值无效),与BF1~BF6(见字节7)共同确定基带滤波器带宽;PD为芯片节电模式控制位。

2 ZL10036的应用实例

2.1 硬件设置

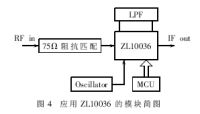

在本文涉及的实际应用中,使用ZL10036作为核心芯片构建了一种可用于通信系统的射频至基带转换器。由于ZL10036芯片的集成度非常高,应用中对芯片的硬件设计涉及比较少,也相对比较简单,主要是接入锁相环路中的无源低通滤波器以及振荡电路。另外,射频输入端要提供 的阻抗匹配。这些外围电路的接法可以参照ZARLINK公司提供的数据手册,其模块简图如图4所示。

的阻抗匹配。这些外围电路的接法可以参照ZARLINK公司提供的数据手册,其模块简图如图4所示。

ZL10036使用了40脚的QFN封装,体积很小,高频端的布线必须考虑射频干扰。芯片的底部有一个散热支架(thermal paddle),具有很高的热传导率,裸片(die)散发的热量可以通过支架高效传出;同时支架对地的连接电阻很小,不会影响芯片工作。ZL10036芯片工作时具有相当高的能量密度,如果多余的热量不能有效散发,芯片会迅速被加热至超过正常工作的极限温度125℃,影响芯片的性能甚至烧毁。所以,为了确保良好接地散热,芯片焊上后,应再从背面滴注焊锡。另外,为了减小版图尺寸,采用0402封装的电容电阻元件。

2.2 软件设置

在通过I2C总线对芯片控制寄存器进行写操作时,主控制器(MCU)发出正确的地址信号(地址字节值的确定参见文献[1])后,ZL10036给出应答,在下一个时钟信号来临时开始写入数据。每写完一个字节,ZL10036都会发出一个应答信号,主控制器收到应答信号后可以发出结束信号终止写操作,也可以继续对下一字节进行写操作,当写完12个字节后,如主控制器继续发出写入数据,则ZL10036将忽略这些数据字节。

ZL10036还提供了非常方便的寄存器子寻址(Register Sub-Addressing)方式,当需要改变的是某些寄存器的值时,并不需要把所有的寄存器都重写。每一对编号为相邻的偶数、奇数的寄存器对可以被单独寻址,如字节2、3或者4、5等。例如,要改写字节7的值,必须先用C$($代表一位16进制数)的数据寻址到字节6,同时芯片用C$重写字节6。注意,只要是C开头的数据字节,芯片即自动寻址到字节6。对于所有的字节对,写入的顺序可以是任意的,用户可以根据需要自定。

软件的主体是把计算好的(或者是芯片要求的)值按一定的顺序写入芯片的12个寄存器。在本应用中外部晶振采用10MHz,参考分频器的分频比取32,频率合成器的初始工作频率取为1000MHz,可编程分频器的分频比为3200,基带滤波器的带宽取为16MHz。由这些值根据芯片数据手册中的公式[1]得到如下的写入数据和顺序(写入顺序不是惟一的):

(1)首先对芯片寻址(地址为0xC2);

(2)顺序写入字节2(0x0C)、3(0x80)、4(0x9F)、5(0x44);

(3)用0xC0、0x24写字节6、7;

(4)用0xC8重写字节6(硬件要求,见字节6的说明);

(5)用0xD3、0x40写字节8、9(此2值为硬件要求);

(6)用0xE3、0x5B写字节10、11;(此2值为硬件要求);

(7)用0xE3、0xF9重写字节10、11;(硬件要求重写11字节);

(8)用0xF0、0x45写入字节12、13。

2.3 单片机控制程序

本应用采用51单片机作为微控制器(MCU)对ZL10036进行控制和设置,其中单片机与ZL10036的I2C接口连接采用软件模拟的方式。所谓软件模拟,就是用单片机的I/O口来模拟I2C总线的工作时序,从而达到能够访问带I2C总线接口器件的目的[5][6]。单片机的任意两个输出端与ZL10036的12脚SCL、13脚SDA分别相连即可,本应用中选用P3.3和P3.4。采用软件模拟的方式模拟I2C总线的通信时,最重要的是确保典型信号的时序要求,如开始信号、数据传送、应答信号和停止信号等,具体参见文献[6]。下面给出本应用的51单片机控制程序。

IIC_WRITE: SETB P3.3 ;先使I2C总线

SETB P3.4 ;处于空闲状态

NOP

CLR P3.4 ;开始信号

NOP

CLR P3.3;SCL拉低,避免误传数据

MOV R1,#0FH;准备16字节的循环传送

LOOP: MOV DPTR,#DATA;传送的数据首地址送入数据指针

MOV A,@DPTR;数据送入累加器

LCALL WRITE_BYTE;长调用写一个字节数据的子程序

INC DPTR;数据指针指向下一个传送

DJNZ R1,LOOP;数据循环

CLR P3.3;拉低SCL,停止传送数据

NOP

CLR P3.4;拉低SDA,准备发送结束信号

NOP

SETB P3.3;拉高SCL,准备发送结束信号

NOP

SETB P3.4;结束信号

NOP

SJMP $;停止

WRITE_BYTE:MOV R0,#08H;八位循环控制

GO_ON: NOP

CLR P3.3;准备传送数据

NOP

RLC A;A移位,把待传数据放入C

MOV P3.4,C;放数据到数据线

SETB P3.3;置SCL高,使数据稳定传输

DJNZ R0,GO_ON;循环传送

CLR P3.3;发第九个时钟信号,

NOP;准备接收应答信号。

SETB P3.3

NOP

WAIT: JB P3.4,WAIT;等待应答信号

CLR P3.3;释放SCL

RET

ORG 0D40H;存放数据单元

DATA: DB 0C2H,0CH,80H,9FH,44H,0C0H,24H,0C8H,0D3H,40H,0E3H,5BH,0E3H,0F9H,0F0H,45H

END

2.4 测试结果

测试中选用芯片频率合成器产生的本振频率为1318MHz,把频率为1288MHz的输入射频信号下变频至30MHz的基频信号。采用的测试仪器是HP公司的8566A频谱分析仪。

由于频率合成器产生的本振功率很小(典型值为-60dBm),下变频的幅值也较小,所以该应用主要关注信噪比。经过频谱仪的测量,频率合成器的本振信号和中频输出信号的信噪比都令人满意,均为25dB左右。通过对样机的测试实验,系统其他的主要性能指标,如频率准确度、锁相环的捕获性能、带宽等都达到了设计要求。

ZARLINK公司的ZL10036芯片是一款工作在950~2150MHz频段的高性能高集成的接收机芯片。它直接给出了RF到基带的解决方案,大大简化了接收机的结构设计,缩短了产品开发周期,降低了成本。普通的解调芯片,如MAX2701内部不集成本振模块,本振需要从外部引入,而ZL10036的最大的特点就是把一般需要两片芯片分别实现的射频至基带转换和PLL频率合成功能集成至一片芯片中,不但提高了集成度,也极大地方便了用户。此外,ZL10036内部的可调带宽的基带滤波器和寄存器控制系统也独具特色,目前,在数字卫星系统以及通信系统设备中得到了越来越广泛的应用,尤其与ZARLINK公司的配套芯片(如ZL10313)配合使用可以提供一套完整的数字卫星信号的解调方案。

本文介绍了一种将ZL10036用于基带转换接收机的设计。主要围绕ZL10036的应用技巧介绍了该系统射频模块的硬件和软件设计。对射频至基带转换系统的实测结果也取得了较好的一致性,参数都达到了系统设计的指标要求。

参考文献

[1] ZL10036 Digital satellite tuner with RF bypass data sheet.Zarlink Semiconductor Inc.Copyright.2004-2005.

[2] 张厥盛,郑继禹,万心平.锁相技术.西安:西安电子科技大学出版社,1994.

[3] 陈文焕.电荷泵锁相环的基础研究.成都:电子科技大学硕士学位论文,2005.

[4] 李 多,陈雅琴,冯正和.MAX2701及其在卫星接收机中的应用.电子技术应用,2003,(9).

[5] 陈光东.单片微型计算机原理与接口技术.武汉:华中理工大学出版社,1999.

[6] 凌六一,伍 龙.基于软件模拟的51单片机IIC总线的实现.电子技术,2004,(5).