摘要:针对高速高灵敏度数字信号处理时对于自适应滤波器的数值特性和实时性的要求,在一种自适应格型联合滤波器的基础上提出算法改进,采用驰豫超前流水线技术和时序重构技术,在损失较小滤波性能的情况下,在FPGA中实现算法并可以达到较高的工作频率。

关键词:自适应滤波器;FPGA;梯度格型滤波器;流水线;时序重构

0 引言

在处理微弱信号的时候自适应滤波器所处的环境可能是非平稳的,输入信号的自相关矩阵和互相关向量等算法参量将随时间变化,会对滤波器的收敛跟踪性能造成较大影响。现代通信系统发展到3G,4G后,几十甚至上百兆比特每秒的数据传输速率对自适应处理技术是个极大的挑战。如何在这类高速环境中运用自适应算法处理高灵敏度信号并使算法保持较低的复杂度以利于实现,是工程应用中必须解决的问题。

由Levinson-Durbin递推公式得到的自适应格型结构以其反射系数收敛快,对输入信号自相关矩阵的特征值扩散相对惰性,是解决此类问题的一个优良选择。GALJP(Gradient Adaptive Lattice Joint Processing)是一种梯度自适应格型结构和LMS结构组成的联合滤波器,由格型结构对输入信号进行迅速解耦,用LMS结构进行自适应处理。考虑到实时处理的要求,采用高度并行的FPGA进行算法实现是一个很好的选择。但是由于GALJP的结构相对复杂,导致其在FPGA中实现的工作频率不高。本文以自适应噪声对消为模型,采用流水线技术和时序重构技术对GALJP算法结构进行改进优化,提出一种改进型RD-GALJP结构。在算法性能影响不大的情况下,在FPGA中能实现达到167.53 MHz采样吞吐率,适合于高速自适应应用的场合。

1 梯度自适应联合滤波算法(GALJP)

格型滤波器具有快速解耦的性质,利用这个特性,结合基本LMS算法得到的一种实用的联合处理结构GALJP,如图1所示。这种联合滤波器由多级格型预测器和LMS期望响应估计器组合而成,它可以先将信号输入进行快速Gram-Schmidt正交化,并由后续的自适应期望响应估计器的LMS算法对去耦信号进行自适应滤波,以改善输入信号特征值扩散对传统LMS算法性能的影响。这种结构具有很大的优点,如调节滤波器的阶数十分方便,增减节数不会影响到系统全局的优化,改变某一节不需要对整个系统进行调节。

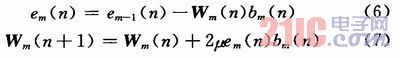

GALJP的基本算法如下:

式中:m=2,3,…,M+1,不同于传统的单个误差e调节各级滤波器权向量更新,上面的GALJP算法是把各节误差信号em(n)的均方值由单节计算,采用多级单LMS结构,并分别指导各级权向量更新。

2 改进型RD-GALJP算法

由于GALJP的算法相对复杂,正常情况下的硬件实现不能达到高速信号处理的要求。在此,结合驰豫超前流水线技术和时序重构技术对算法进行优化改进,以便在对滤波性能没有很大影响的情况下能有效地切割关键路径,提高系统运行频率。

2.1 驰豫超前流水线优化

流水线技术是构造高速运行系统的一种实用技术。在硬件实现中,通过插入流水寄存器,可以斩断系统关键路径的长度,提高系统的运行频率。单向前馈割集表示能够斩断同向信号流,使系统成为完全不相连两个部分的分割形式。本文对于单向前馈割集路径插入一级流水寄存器,这里会使输出增加一个时钟滞后,但可以在不影响系统算法性能的情况下切割路径,提高系统频率。

驰豫技术也是一种可以构造实现流水线的方式,它通过近似的方式改变算法,在系统可以良好稳定运行的情况下得到适合流水实现的拓扑结构。对于GALJP算法,考虑到其中有多个环路迭代计算,无法使用前馈割集插入流水线的方式改进。对此,通过驰豫超前技术,提出的改进部分如下,对于格型预测器有:

式中:m=2,3,…,M+1,对于格型预测器,由于反射系数Km收敛迅速,所以在收敛后由于Km基本不变,故等式(8),式(9)是合理的。稳态性能则基本不变。

考虑收敛时段的式(10),令:

当系统处于收敛时段,恰当选取较小的β值时,式(15)的递推也是合理的,对比改变前的式(14),只是更新部分数值变大。这里可以看到,对于反射系数的驰豫,其算法收敛步长的区间将变得相对严格。类似的,对于期望响应估计器,对bm和Wm的驰豫变换在恰当选取稍小的μ的情况下也是合理的,同样的,会造成步长收敛区间变得相对狭窄。观察改进后的拓扑结构,对于期望响应估计器,改进后的误差更新和权系数更新可以同时流水进行,提高了模块速度,对于格型预测器,虽然改进方案没有使其能够流水线化,不能实质地提高系统频率,但是提供了驰豫寄存器,为后续优化做了准备。在这里,驰豫寄存器m1,m2的个数需要根据要求仔细选取。

2.2 时序重构优化

时序重构又称重定时,是一种在保持系统功能不变的前提下,改变系统的延迟数目和分布的方法。它在同步电路中有许多应用,如缩短系统时钟周期,减少系统寄存器数目,降低系统的功耗和逻辑综合的规模。对于时序不变系统,通过时序重构技术,可以在不改变算法功能的情况下,有效地切割关键路径,从而提高系统工作频率。时序重构的映射等式定义为:

![]()

式中:Wr(e)表示重构映射后的路径e的延时;W(e)表示重构映射前的路径e的延时;r(V)表示路径e的前端处理单元V的重构参数;r(U)代表路径e的后端处理单元U的重构参数。通过合理地选取重构映射参数,可以得到合法的重构映射结构。

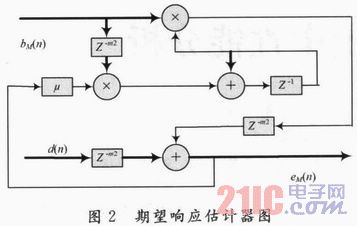

环路边界的定义为t1/wl,其中tl是环路l的运算时间;wl是环路l的延迟数目;迭代边界是环路结构的环路边界的最大值,定义为![]() ,迭代边界反映了一个反馈算法环路部分通过时序重构技术能达到的极限关键路径的大小。在此认为加法器和乘法器都是一个处理时间,考虑期望响应估计器模块的环路部分,如图2所示。

,迭代边界反映了一个反馈算法环路部分通过时序重构技术能达到的极限关键路径的大小。在此认为加法器和乘法器都是一个处理时间,考虑期望响应估计器模块的环路部分,如图2所示。

根据定义可以知道,迭代边界为4/(1+m2),使其迭代边界最小化,等于1,得到驰豫寄存器的数目m2=3。采用时序重构映射,根据式(16)得到重构后的算法结构,重构参数及重构结果如图3所示。

由于重构后每个信号路径上都没有负延时情况,根据时序重构原理的性质,则这个重构映射是合理的,重构后的算法结构是合理的,稳定的。可以看到,合理地选取映射规则对电路进行时序重构,可以合理地斩断关键路径,提高系统运行速度。在这里,重构后的关键路径为一个处理单位。同理,可以对多级格型预测器模块进行时序重构。同样的,重构后格型预测器电路的关键路径也为一个处理单元。这样,整个改进后的RD-GALJP(Retimed Delay-GALJP)系统结构的关键路径就缩短为1个处理单元。

3 基于FPGA的算法的实现与仿真

以自适应噪声对消为模型进行仿真验证,设格型预测器的反射系数收敛因子为0.008,期望响应估计器的收敛因子为0.002。在Matlab中对改进前和改进后的算法进行仿真,测试信号为随机2FSK+高斯白噪声,SNR=-9 dB,得到的收敛曲线如图4所示。

可以看到,改进后的算法在收敛性能和稳态表现都有些许下降,但是降低的幅度很小,在可接受的范围内。利用DSP-builder进行FPGA算法建模,实现4阶16位定点格式的格型滤波结构,并在Modelsim中进行RTL级仿真,得到的改进算法滤波效果如图5所示。

在EP2C70F896C6芯片上进行代码的综合,得到的结果为:改进前系统的最高工作频率为23.99MHz,改进后系统的最高工作频率为167. 53 MHz。显然,系统频率在算法结构改进后有很大的提高。最后,利用DDS技术产生需要的测试信号和噪声(测试频率为100 MHz),将相应的HDL代码综合布线后下载到FPGA芯片中,利用Signaltap内嵌逻辑分析仪进行板级功能测试,结果如图6所示。

实验结果表明,该模块可以很好地运行在100 MHz以上,适用于高速自适应处理的场合。

4 结 语

FPGA以其高效的硬件特性在信号处理方面有着越来越多的应用。本文结合驰豫超前流水线和时序重构技术,提出一种RD-GALJP算法结构,并以自适应噪声对消为模型进行算法仿真。算法仿真的结果表明,改进算法结构相比改进前的算法在滤波性能上只有些许下降,但是却能够很好地切割关键路径,以利于流水实现。最后以4阶16位定点格式为背景在FPGA中对算法进行实现和板级功能测试,综合布线后得到16 7.53 MHz采样吞吐率的运算性能,比较于改进前的23.99 MHz的工作频率表明,工作频率的改善显著。实验结果表明,改进算法结构可以很好地应用于对输入自相关矩阵特征值扩散敏感的高速高灵敏度的自适应信号处理场合。