文献标识码: A

文章编号: 0258-7998(2014)03-0035-03

自适应滤波器在现代数字信号处理中的应用极为广泛,分成系统辨识、逆模型、预测和干扰消除4大类别[1]。对于实时性要求很高的场合,往往需要使用硬件设计自适应滤波器。基于FPGA的自适应滤波器近年来被不断地研究和改进。

使用FPGA中的逻辑单元(LE)很容易实现乘累加(MAC)运算,从而将采用最小均方(LMS)算法的自适应滤波器直观地映射到FPGA上。但是,基于MAC方案的自适应滤波器的时钟频率会很高,功耗会很大。ALLRED D J等人提出了利用双LUT结构的DA方案来实现LMS自适应滤波器[2],虽然提高了吞吐量,降低了功耗,但其控制模块、地址循环设置都比较复杂;Guo Rui等人提出采用单LUT结构的DA方案来实现LMS自适应滤波器[3],尽管节省了近一半的LE,但其处理速度有所下降,并且偏移二进制编码(OBC)的硬件编程颇为复杂。

本文提出了基于双LUT模块的特殊DA方案,旨在将LMS顺序执行算法更高效地映射到FPGA上,充分利用了DA的基本特性以及对LMS算法的改进来达到节省资源、提高速度的目标。

1 自适应滤波器的算法

设x(n)和w(n)分别表示自适应滤波器的输入信号和权值向量,定义:x(n)=[x(n),x(n-1),…,x(n-L+1)]T,w(n)=[w0(n),w1(n),…,wL-1(n)]T,则LMS算法的基本形式如下。

滤波输出:

其中,y(n)是自适应滤波器的输出信号,d(n)是期望信号,e(n)表示误差信号,![}JJTQN]GT1{(L)30B%]IN_R.png }JJTQN]GT1{(L)30B%]IN_R.png](http://files.chinaaet.com/images/2017/01/16/6362017151198453858691880.png) 是收敛因子,L是自适应滤波器的抽头数。虽然LMS算法仅涉及乘法、加减和迭代3种运算,但它是一种严格顺序执行的自适应算法[1]。倘若利用MAC方案直接将LMS自适应滤波器映射到FPGA上,编程虽然简单,但难以发挥FPGA并行处理的优势。

是收敛因子,L是自适应滤波器的抽头数。虽然LMS算法仅涉及乘法、加减和迭代3种运算,但它是一种严格顺序执行的自适应算法[1]。倘若利用MAC方案直接将LMS自适应滤波器映射到FPGA上,编程虽然简单,但难以发挥FPGA并行处理的优势。

延迟最小均方(DLMS)算法是对LMS算法的一种改进,该算法最大的优点就是可以并行执行[4]。本文所使用的DLMS算法的权值更新公式为:

![LS5O@~(7K(NZX]07AO)6)ND.png LS5O@~(7K(NZX]07AO)6)ND.png](http://files.chinaaet.com/images/2017/01/16/6362017152589153855307915.png)

而滤波输出、误差计算公式与LMS算法相同。由式(4)知,对第k个权值wk(n)进行迭代更新时,必须对相应的x(n)延迟k个采样周期,k=0,1,…,L-1。图1给出了DLMS自适应滤波器的模块图。

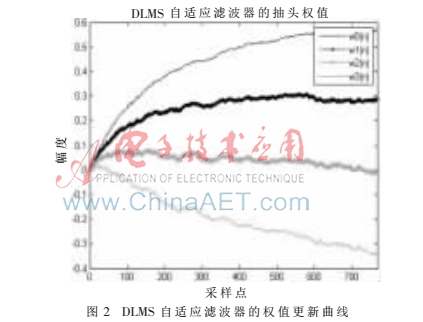

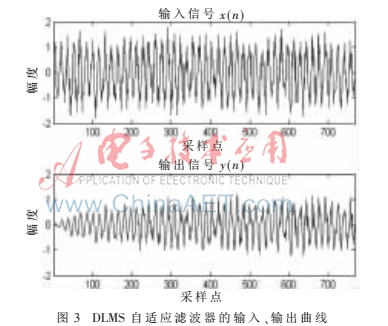

图2、图3分别给出了4抽头DLMS自适应滤波器的抽头权值以及输入、输出信号的Matlab仿真曲线。由图2知,自适应滤波器的4个抽头权值的总体变化趋势渐趋平缓。由图3知,输出信号相对于输入信号而言抖动幅度逐渐变小,而且愈发类似于正弦信号。但由于该自适应滤波器只有4个抽头,输入信号的信噪比只有3 dB,所以自适应滤波器的权值在520个采样点以后才比较平缓,并且输出信号与期望信号之间仍存在较明显的差别。若能提高自适应滤波器的抽头数,或改用信噪比更高的输入信号,则会加快抽头权值的平缓速度,并且输出信号将更加接近正弦信号。

2 特殊DA方案

在使用DA方案优化基于FPGA的权值固定的经典滤波器时,首先把滤波器的权值系数有规律地存储在LUT模块中,然后利用输入信号的二进制形式从最低位到最高位逐一访问LUT模块的存储条目,最后对LUT模块的各个输出量进行移位、累加运算,得到最终的滤波输出结果[5]。而自适应滤波器的权值是不断更新变化的,必须对存储在LUT模块中的权值进行迭代更新,这时可以考虑使用两个LUT模块联合运作。

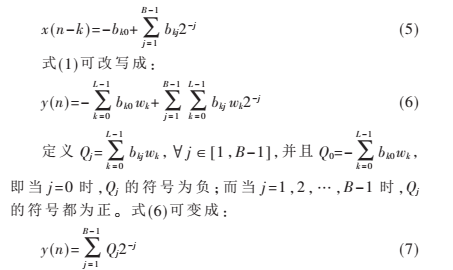

设输入信号x(n)被量化成B bit二进制补码的形式,最左边一位是符号位,则:

Qj存储在LUT模块中时没有正负之别,在LUT模块输出端的后面引入一个符号控制端来判定对Qj做加法还是减法[6]。该LUT模块定义为核心查找表(K-LUT)。

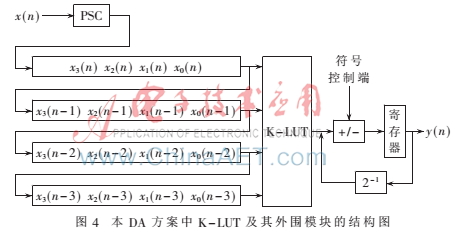

图4给出了L=4、B=4的DLMS自适应滤波器设计中K-LUT及其外围模块的结构图。图中的PSC模块表示并/串转换器,2-1模块表示右移器。

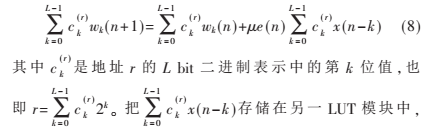

K-LUT的第r个条目的更新式如下:

该LUT模块定义为输入查找表(I-LUT)。当检测到自定义的中间信号clk_data的上升沿时,新的输入信号将被读入,I-LUT的内容随即自动更新。

该LUT模块定义为输入查找表(I-LUT)。当检测到自定义的中间信号clk_data的上升沿时,新的输入信号将被读入,I-LUT的内容随即自动更新。

对于L=4、B=4的情况,由Quartus II集成开发软件的时序仿真结果知,clk_data的周期应设置成为时钟信号clk周期的6倍。第n时刻I-LUT的各个条目存储内容如表1所示。当n+1时刻来临时,x(n)、x(n-1)、x(n-2)、x(n-3)自动变成x(n+1)、x(n)、x(n-1)、x(n-2)。

一旦n时刻I-LUT的内容更新并且y(n)、e(n)、e(n)的计算都已完成,那么K-LUT的内容将被更新。通过设置合适的clk_data周期来保证K-LUT(n)到K-LUT(n+1)的更新在n+1时刻到来之前全部完成。式(8)则变为:

K-LUT(r)(n+1)=K-LUT(r)(n)+?滋e(n)I-LUT(r)(n)(9)

K-LUT的更新步骤如下:(1)读取K-LUT(n)和I-LUT(n)中具有相同存储地址的条目;(2)用![}JJTQN]GT1{(L)30B%]IN_R.png }JJTQN]GT1{(L)30B%]IN_R.png](http://files.chinaaet.com/images/2017/01/16/6362017161705953851564038.png) e(n)乘以I-LUT(n)的输出;(3)将步骤(2)中的乘积与K-LUT(n)的输出进行求和运算;(4)将步骤(3)中的和存储到K-LUT(n+1)中相同存储地址的条目。其中?滋和e(n)相乘是通过对e(n)进行移位运算实现的,

e(n)乘以I-LUT(n)的输出;(3)将步骤(2)中的乘积与K-LUT(n)的输出进行求和运算;(4)将步骤(3)中的和存储到K-LUT(n+1)中相同存储地址的条目。其中?滋和e(n)相乘是通过对e(n)进行移位运算实现的,![}JJTQN]GT1{(L)30B%]IN_R.png }JJTQN]GT1{(L)30B%]IN_R.png](http://files.chinaaet.com/images/2017/01/16/6362017164732953856615751.png) 值选成2的幂。

值选成2的幂。

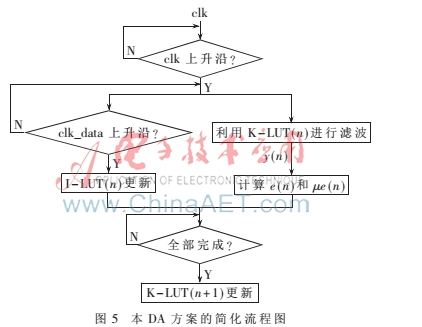

图5为本DA方案的简化流程图,可以看出I-LUT的更新由clk_data控制,而滤波运算、误差计算、![}JJTQN]GT1{(L)30B%]IN_R.png }JJTQN]GT1{(L)30B%]IN_R.png](http://files.chinaaet.com/images/2017/01/16/6362017162895153853960326.png) e(n)的乘积运算都由clk控制。

e(n)的乘积运算都由clk控制。

3 基于FPGA实例验证

由于FPGA中的LUT通常具有4个输入端,共24个存储条目,故本文以设计4阶基于FPGA的DLMS自适应滤波器为例,这样使用两个LUT模块就能实现最基本、最小规模的自适应滤波器。其他的高阶设计都以4阶为基础。

表2给出了分别采用MAC方案和本DA方案设计出的DLMS自适应滤波器的各项性能指标。这里![}JJTQN]GT1{(L)30B%]IN_R.png }JJTQN]GT1{(L)30B%]IN_R.png](http://files.chinaaet.com/images/2017/01/16/6362017164189653854900527.png) 取1/4。必须指出,系统时钟clk的最高频率与系统功耗密切相关,频率越高,功耗越大;用于控制输入信号读取速度的clk_data的最高频率表征了DLMS自适应滤波器的处理速度。

取1/4。必须指出,系统时钟clk的最高频率与系统功耗密切相关,频率越高,功耗越大;用于控制输入信号读取速度的clk_data的最高频率表征了DLMS自适应滤波器的处理速度。

由表2知,本DA方案设计出的DLMS自适应滤波器不但消耗了更少的LE和寄存器数量,而且获得了更低的功耗和更高的处理速度,优势明显。表3给出了同样采用本DA方案但![}JJTQN]GT1{(L)30B%]IN_R.png }JJTQN]GT1{(L)30B%]IN_R.png](http://files.chinaaet.com/images/2017/01/16/6362017169232753852487523.png) 值不同时的DLMS自适应滤波器的性能比较。

值不同时的DLMS自适应滤波器的性能比较。

由表3知,![}JJTQN]GT1{(L)30B%]IN_R.png }JJTQN]GT1{(L)30B%]IN_R.png](http://files.chinaaet.com/images/2017/01/16/6362017165438453859486573.png) 取不同值时采用本DA方案设计DLMS自适应滤波器所消耗的LE和寄存器数目是相同的,所以在保证DLMS算法收敛前提下,

取不同值时采用本DA方案设计DLMS自适应滤波器所消耗的LE和寄存器数目是相同的,所以在保证DLMS算法收敛前提下,![}JJTQN]GT1{(L)30B%]IN_R.png }JJTQN]GT1{(L)30B%]IN_R.png](http://files.chinaaet.com/images/2017/01/16/6362017182170453857220135.png) 的取值不会影响设计自适应滤波器所消耗的硬件资源,但是自适应滤波器的功耗和处理速度会有少许差别。

的取值不会影响设计自适应滤波器所消耗的硬件资源,但是自适应滤波器的功耗和处理速度会有少许差别。

本文提出的特殊DA方案的基本结构主要包含K-LUT和I-LUT模块,重点讨论了4阶DLMS自适应滤波器的设计方案。通过验证,采用本DA方案设计基于FPGA的DLMS自适应滤波器相对于MAC方案具有更高的处理速度和更低的资源消耗。本方案推广到更高阶设计时,总体思路不变,但最好要对K-LUT和I-LUT模块进行分解,具体办法有待进一步探究。

参考文献

[1] HAYKIN S.自适应滤波器原理(第四版)[M].郑宝玉,译.北京:电子工业出版社,2010.

[2] ALLRED D J,HEEJONG Y,KRISHNAN V,et al.A novel high performance distributed arithmetic adaptive filter imple-mentation on FPGA[J].IEEE Signal Processing,2004,5(5):161-165.

[3] Guo Rui,DEBRUNNER L S.A novel adaptive filter imple-mentation scheme using distributed arithmetic[J].IEEE Signals,Systems and Computers,2011,6(11):160-164.

[4] Long Guozhu,Ling Fuyun,PROAKIS J G.The LMS algorithmwith delayed coefficient adaptation[J].IEEE Transactions on Acoustics,Speech and Signal Processing,1989,37(9):1397-1405.

[5] UWE M B.Digital signal processing with field programmablegate arrays[M].Third Edition.Germany Berlin:Springer- Verlag,2007.

[6] ALLRED D J,YOO H,KRISHNAN V,et al.LMS adaptive filters using distributed arithmetic for high throughput[J].IEEE Transactions on Circuits and Systems,2005,52(7):1327-1337.