Lattice向目标不断前行,最新LatticeECP4系列重新定义低成本、低功耗FPGA

2011-11-30

作者:电子技术应用网记者:陈颖莹

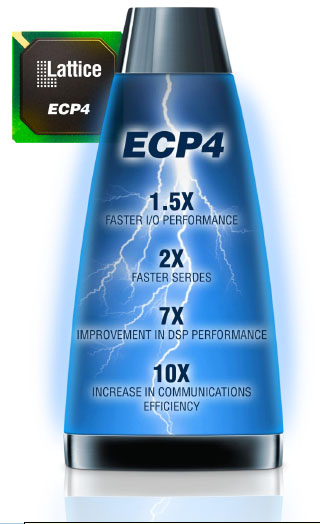

今年6月,莱迪思半导体公司(Lattice)总裁及首席执行官Darin Billerbeck先生在一次活动上谈到了Lattice的发展目标:坚持低功耗、低成本的产品路线,CPLD市场占有率第一,增强IP和软件实力,转型为可编程SoC厂商。Lattice朝着自己的目标不断前行,近日,Lattice副总裁兼业务部总经理Sean Riley与记者分享了Lattice 半年来的成果以及最新产品LatticeECP4 FPGA。

当其他两大FPGA厂商在高端FPGA市场争夺得热火朝天之时,Lattice在中低端市场收获很大,虽然可能用蟹蚌相争渔人得利来形容不是很恰当,但是也有类似之处。Sean介绍到:到今年第三季度,Lattice CPLD的市场份额已经跃居全球第一。虽然今年经济环境不是很好,但是平板电脑等消费电子发展迅速,恰恰让Lattice MachXO2 低密度PLD一展所长,被大量应用在对功耗和成本敏感的市场。LatticeECP3 中端FPGA和MachXO2成了Lattice的明星产品,家喻户晓。说到LatticeECP3,Sean自豪地说:“LatticeECP3是我们Lattice在FPGA系列中增长最快的产品,从去年到今年第三季度,其增长率是84%,增长势头十分强劲。可以说LatticeECP3是我们一个非常伟大的产品。我们的目标就是通过LatticeECP4能够把这个系列做得更好。”

更低的成本

充分的现金流让Lattice即便在市场环境不是很好的情况下也有足够的实力去研发新产品。新推出的LatticeECP4 FPGA重新定义了低成本、低功耗的中档FPGA市场。Sean表示:“采用低成本、高成品率的65 nm工艺是非常理想的选择。当然我们也在关注28 nm的工艺,我们认为在将来的某个时候,28nm的工艺也会有成本下降的趋势。目前65 nm还是成本之王,是最经济的。可能在2015年的时候,28 nm也可能具备这样的成本优势,到时候可能就会发布我们的LatticeECP5了。此外,封装部分往往容易被人忽略,倒装(flip chip)晶片就比wire-bond封装的成本贵2倍。LatticeECP4使用了低成本的wire-bond封装和高性能flip chip封装,使客户能够选择以芯片到芯片或者远距离背板应用的方式应用LatticeECP4。

在内部架构上,Lattice的工程师们也是发挥无限想象力以求降低成本。LatticeECP4具有CDR功能的I/O降低了客户的实现成本;POWER sysDSP大大减少了乘法器和LUT的数量,在小的面积中有高带宽;使用固化的MACO通信引擎减少了10倍的面积。Sean详细描述了LatticeECP4这些特性。

POWER sysDSP 模块

Sean说到:“现在越来越多的客户要求我们提升DSP的性能,但是他们又不愿意承担成本和功耗的增加。新推出的LatticeECP4系列具有强大功能的数字信号处理模块(POWER sysDSP模块),18×18乘法器、宽ALU、加法树,以及用于级联的进位链块。独特的加速逻辑意味着每个LatticeECP4 DSP模块可等于4个LatticeECP3 DSP模块,4倍于LatticeECP3器件的信号处理能力。”灵活的18×18乘法器可以分解成9×9或组合成36×36,以便完美的符合客户的应用需求。此外,多达576个乘法器可以级联在一起构成复杂的滤波器,这让LatticeECP4能以更低的成本和功耗实现主流的多天线系统(4×4 MIMO 40 MHz)以及高性能运动检测与跟踪。

Sean说到:“现在越来越多的客户要求我们提升DSP的性能,但是他们又不愿意承担成本和功耗的增加。新推出的LatticeECP4系列具有强大功能的数字信号处理模块(POWER sysDSP模块),18×18乘法器、宽ALU、加法树,以及用于级联的进位链块。独特的加速逻辑意味着每个LatticeECP4 DSP模块可等于4个LatticeECP3 DSP模块,4倍于LatticeECP3器件的信号处理能力。”灵活的18×18乘法器可以分解成9×9或组合成36×36,以便完美的符合客户的应用需求。此外,多达576个乘法器可以级联在一起构成复杂的滤波器,这让LatticeECP4能以更低的成本和功耗实现主流的多天线系统(4×4 MIMO 40 MHz)以及高性能运动检测与跟踪。

高品质的SERDES和固化的通信引擎

LatticeECP4 FPGA包含多达16个符合CEI标准的6 Gb/s SERDES通道,具有嵌入式物理编码子层(PCS)模块。多功能和可配置的SERDES/PCS可以无缝地与固化的通信引擎相集成,经济地构建完整的高带宽子系统。通信引擎比用类似的FPGA实现减少10倍以上的功耗和成本。LatticeECP4通信引擎组合包括针对PCI Express2.1、多个10千兆以太网MAC和三速以太网MAC,以及串行快速I/O(SRIO)2.1的解决方案。SERDES/PCS和通信引擎的结合是完成基于复杂串行协议的设计的理想选择,具有较低的成本,功耗和小尺寸的特点,同时加快了产品的上市时间。

具有嵌入式CDR的GIGASysIO

LatticeECP4 FPGA的速度比上一代器件快50%,LatticeECP4具有1.25 Gb/s LVDS I/O以及1 066 Mb/s的低成本、高性能DDR3存储器接口,拥有时钟数据恢复模块,能够与高性能ADC/DAC接口和实现SGMII/ GbE链路。多达40个嵌入式CDR,可以直接连接到EMAC MACO通信引擎。在通用的I/O上执行CDR功能为设计人员大大增加了串行I/O的数目,当需要大量的SERDES通道时,甚至可以使用更小的FPGA,大大降低了实现串行以太网接口逻辑的成本。此外,LatticeECP4 系列还有高达10.6 Mbits的嵌入式存储器,逻辑密度从30K LUT~250K LUT,使设计工程师能够在FPGA中构造完整的片上系统。

很多人都想知道Lattice是否会赶潮流,把ARM内核嵌入Lattice的FPGA中。Sean回答道:”我们还是依据自己的路线去发展,把ARM嵌入FPGA中会增加成本,目前我觉得不是很适合Lattice。我们不像其他两家公司一样,想要FPGA取代ASIC和ASSP,反而我们会跟ASIC和ASSP厂商合作(如TI)。我们的产品也会与ARM合作,但是会采用堆叠的方式。”

加强IP核和软件功耗

Lattice提供IP核、开发板和设计软件设计,以便快速启动设计和快速使产品上市。一系列的IP核将包括CPRI、OBSAI、串行RapidIO、XAUI、SGMII/千兆以太网、PCI Express、串行连接SMPTE、FIR滤波器、FFT、Reed-Solomon编码器/解码器、针对DSP功能的CORDIC、CIC、NCO和针对存储器接口和连接的其他几个IP核。

Lattice Diamond设计软件针对高性能、低成本LatticeECP4的POWER sysDSP作了多个改进,还有针对逻辑分析与SERDES控制的Reveal调试器。此外,Lattice Diamond使用更加方便,新的系统规划工具优化了资源的使用,还具有静态和动态的低功耗模式的功耗计算器,基于引脚的同时开关输出噪声计算器和经验证的MAP和PAR FPGA实现算法,有助于确保低成本和低功耗设计的解决方案。

这些也恰好印证了Darin年中所说的增强IP和软件实力的目标。Lattice Diamond也是获得了《电子技术应用》颁发的2011最佳产品奖。

以上这些特点使LatticeECP4 FPGA系列非常适合于大批量的成本和功耗敏感的应用,如无线基础设施、有线接入设备、视频和图像以及计算应用。短短半年时间,Lattice在硬件和软件等各方面不断努力,造就出优秀的产品,希望它继续向目标前行,给我们带来更多惊喜。