SOPC" title="SOPC">SOPC(System On Programmable Chip)技术是美国Altera" title="Altera">Altera公司于2000年最早提出的,并同时推出了相应的开发软件Quartus II。SOPC是基于FPGA解决方案的SOC(System On Chip),构成SOPC的方案也有多种。第一种是基于FPGA嵌入IP硬核的SOPC系统,即在FPGA中事先植入嵌入式系统处理器,目前最常用的嵌入式处理器大多采用了含有ARM的32位知识产权处理器核的器件。第二种是基于FPGA嵌入IP软核的SOPC系统,目前最有代表性的软核处理器分别是Altera公司的Nios II核,以及Xilinx公司的MicroBlaze核。第三种是基于HardCopy技术的SOPC系统,HardCopy就是利用原有的FPGA开发工具,将成功实现于FPGA器件上的SOPC系统通过特定的技术直接向ASIC转化。

1 基于Altera公司NiosⅡ" title="NiosⅡ">NiosⅡ软核处理器的SOPC系统

Altera公司Nios II软核是目前使用最为广泛的一种软核处理器。值得一提的是,利用Matlab和Altera公司的DSP Builder,用户可以为Nios II软核处理器设计各类DSP硬件加速器,并以指令的方式加入Nios II的指令集,从而可以构建自己的DSP处理器系统。

1.1 基于NiosⅡ软核处理器的SOPC系统结构

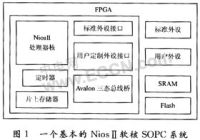

如图1所示的一个基本的基于NiosⅡ软核的SOPC系统,除NiosⅡ核、定时器和片上存储器以外,还需要在FPGA器件中添加一些接口元件。这些元件一方面通过片上的Avolon总线与NiosⅡ软核相连,另外一方面又提供了外设与NiosⅡ软核通信的接口界面。

Altera公司QuartusⅡ软件中的SOPC Builder工具提供了许多常用的外设接口元件,如UART接口元件、PIO接口元件等,通过这些接口元件可以连接诸如RS232、LED、数码管" title="数码管">数码管和按键等输入输出设备。在相对复杂的系统设计当中,还可以通过Avalon三态总线桥外接大容最的SRAM和FLASH,以提供更大的程序和数据存储空间。从图1中,还可以注意到,通过使用系统提供的用户自定制外设接口元件的功能,用户可以在系统中添加一个符合Avalon总线规范的外设接口元件,以连接用户特定功能的外部设备。

1.2 自定制Avalon用户外设接口元件简介

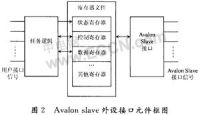

对于自定制的Avalon外设接口元件按照Avalon总线操作的不同可以分为两类:Avalon Slave外设接口元件型的自定制的Avalon Slave外设接口元件框图。从图2中可以看到寄存器的定义是自定制外设接口元件很重要的一部分,必须根据设计的需要确定寄存器的个数和种类。图2中的Avalon Slave接口提供了自定制外设接口元件与NiosⅡ处理器之间数据交换的界面,其接口信号类型也必须根据设计的需要合理地进行选择。常用的Avalon Slave接口信号类型有:clk,chipselect,address,write,writedata,byteenable,reset等。图2中的任务逻辑具体说明了自定制外设接口的功能,并给出了与外设连接的接口信号。

自定制Avalon Slave外设接口元件的方法:可以利用SOPC Builder提供的元件编辑器在图形用户界面下将用硬件描述语言(Verilog或VHDL)描述的用户逻辑封装成一个SOPC Builder元件。相应的硬件描述语言文件给出了自定制外设接口元件的内部寄存器结构,使用到的Avalon Slave接口信号和自定制外设接口的逻辑功能。一旦定制成功后,用户自定制的外设接口就可以象SOPCBuilder中其他元件一样被调用。

2 基于NiosⅡ软核处理器的七段数码管动态显示设计

数字系统设计中,用数码管显示数据结果是常用的一种方法。利用Altera的SOPC Builder工具进行Nios Ⅱ系统设计时,并没有提供专门的数码管显示接口元件,但可以使用PIO元件驱动数码管显示,不足之处是占用器件引脚数目过多。本文当中以自定制Avalon Slave外设接口元件的方式,给出了一种基于NiosⅡ软核的七段数码管动态显示设计方案。该设计可以用来驱动1~8个共阴极(或共阳极)数码管的显示,可以根据需要选择小数点显示的位置,每个数码管可以显示0~F之间的十六进制字符。

图3为自定制的数码管动态显示接口元件逻辑结构图,其中定义了2个寄存器display_data_reg和controlreg。display_data_reg是个一个32位二进制的数据寄存器,其数据每4位可以译码得到1个数码管的七段显示所需的字符码,因此,display_data_reg同时最多可以给出8个数码管所需要的显示数据。control_reg是一个8位二进制的控制寄存器,但只定义了0~2位和第4位的含义。0~2位的数据给出了小数点显示的位置,数值范围在“000”~“111”之间,对应着8个数码管最低位到最高位的小数点的位置。第4位是数码管显示的启动停止位,当该数据位为1时,可使自定制接口元件所驱动的数码管正常显示结果;当该数据位为0时,停止显示,所有被驱动的数码管熄灭。

参数n定义了循环加法计数器的模数,同时也决定了驱动数码管显示的个数,其取值范围在1~8之间。clkdisplay是循环加法计数器的时钟输入,他决定了计数器的计数频率,同时也决定了数码管显示的动态扫描频率。参数pos用于决定驱动数码管的类型,其值可设定为0或1。当其值为0时,seg_out字符码输出高电平有效,bit_control数码管位选控制输出低电平有效,此时输出结果用于驱动共阴极数码管显示;当pos值为1时,seg_out字符码输出低电平有效,bit_control数码管位选控制输出高电平有效,此时输出结果用于驱动共阳极数码管显示。

seg_out为自定制元件的字符码输出,用于驱动数码管显示(包括小数点位)。其中,最高一位seg_out[7]用于驱动对应数码管的小数点显示,低7位seg_out[6..0]用于驱动数码管的七段宁符显示。图3中数码管七段译码器根据循环加法计数器的当前状态值,从display_data_reg寄存器中选择4位二进制数据进行译码。例如,当前驱动的数码管的个数为5个(即n=5),循环加法计数器的当前状态值用count表示,则count在0~4范围内变化;若计数器的当前状态值count为2,则选择寄存器display_data_reg[11..8]的4位二进制数据进行译码,若计数器的当前状态值count为3,则选择寄存器display_data_reg[15..12]的4位二进制数据进行译码,即总是选择寄存器display_data_reg[(count+1)×4-1..count×4]的4位二进制数据进行译码。寄存器control_reg的低3位指明了小数点显示的位置,如control_reg[2..0]的值为“000”,则第0位数码管的小数点点亮,若control_reg[2..0]的值为“010”,则第2位数码管的小数点点亮。因为,循环计数器的状态值count反应了数码管动态显示过程中当前数码管显示的位皆,因此,数码管小数点译码器只要比较control_reg[2..0]与count的值,若两者相等,seg_out[7]输山有效值(共阴极输出为高电平,共阳极输出为低电平)即可驱动对应数码管的小数点点亮。

bit_control为自定制元件的位选控制输出,其数据宽度为n位二进制,与要驱动的数码管的个数是一致的。上面已经提到,循环加法计数器的状态值count反应了当前数码管显示的位置。因此,只要根据count的值,使得bit_control对应位输出有效值即可。例如,n取值为5,pos取值为0(即驱动共阴极数码管),若计数器的当前状态值count为2,则bit_control的输出结果为“11011”,若count为4,则bit_control的输出结果为“01111”。

自定制元件的设计采用的是VHDL语言,其实体描述如下面程序所示:

从上面的程序可以看到:n和pos定义成了类属变量,当完成接口元件的定制以后,类属变量在自定制元件的设置窗口中将以用户参数的形式出现,如图4所示,用户可以设置其值。

实体描述当中除定义了自定制元件与外部设备的接口信号clk_display,seg7_out,bit_control信号以外,还定义了 Avalon Slave接口信号,NiosⅡ软核通过这些信号访问自定制元件中定义的寄存器。前面介绍的两个寄存器display_data_reg和control_reg是在程序的结构体说明部分定义的,具体语句如下:

signal display_data_reg:std_logic_vector(31downto 0);

signal control_reg:std_logic_vector(7 downto 0);

结构体中还完成了所定义的两个寄存器的数据写入操作。图3中所示的模n循环加法计数器、七段译码器、小数点译码器和位译码器也在结构体中按上面所介绍的功能设计完成。

3 实验结果

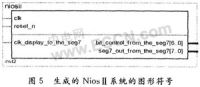

为了验证用于驱动七段数码管动态显示的自定制元件功能,实验中使用SOPC Builder建立了一个最简单的NiosⅡ系统。该NiosⅡ系统添加了3个元件,名称为cpu_0的NiosⅡ软核处理器;名称为seg7的自定制元件,用于完成数码管的显示驱动;名称为onchip_RAM的片上随机存储器,存放调试时的程序代码以及用作程序运行空间。生成的NiosⅡ系统的图形符号如图5所示,clk是系统工作时钟输入;reset_n是系统复位输入,低电平有效;clk_display_to_the_seg7是数码管扫描时钟输入,他决定了数码管动态显示的扫描速度;bit_control_from_the_seg7是位选控制输出,决定了动态过程中哪一个数码进行显示seg7_out_from_the_seg7是数码管显示数据输出,决定了数码管显示的内容。

新建顶层原理图,调用该NiosⅡ系统,为其添加输入输出引脚,并定义引脚号,选择目标器件型号为EP1C6Q240C8,编译生成配置文件,并通过下载电缆下载到目标器件中。接下来利用NiosⅡIDE建立用户程序。

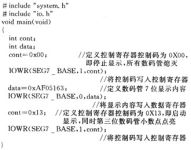

实验建立NiosⅡ系统时,添加驱动七段数码管显示的自定制元件seg7时的参数n和pos(如图4所示)设置成了两种测试情况,分别用来验证其驱动共阴极和共阳极数码管显示的情况。第一种测试情况将n设置成7,pos设置成0,用来驱动7个共阴极数码管显示。NiosⅡIDE建立的用户测试程序如下:

程序编译通过后,可以在硬件中调试运行程序。为了便于观察测试结果,在ModelSim中运行仿真结果,得到仿真波形如图6所示。仿真分析时系统工作时钟(clk)设置为了50 MHz,数码管动态显示扫描频率(clk_display)设置为1 kHz。图6(a)给出了寄存器内容的写入过程,3个write高电平期间完成了 3次寄存器的写入操作。第一次write高电平将0x00写入address为1的寄存器(即控制寄存器,该定义是在自定制元件的硬件描述语言设计中完成的);第二次write高电平将0xAF05163写入address为0的寄存器(即数据寄存器);第三次write高电平将0x13又写入address为1的控制寄存器。当控制寄存器的内容为0x00时,数码管是停止显示的,因此,在共阴极显示的情况下bit_control的输出全为高电平,直到控制寄存器的内容写入0x13后,bit_control才有输出为低电平的情况(如图6所示)。图6(b)给出了写入寄存器内容以后的工作情况,当数据寄存器写入0xAF05163、控制寄存器写入0x13后,bit_control将从1111110到0111111循环变化,同时将数码管显示所需要的字符码从seg7_out输出。如当bit_control为1111110时,seg7_out输出字符码为0x4F,对应显示“3”;当bit_control为1111101时,seg7_out输出字符码为0x7D,对应显示“6”。由于控制寄存器写入的内容为0x13,即第三位数据管的小数点会亮起,因此当bit_control为1110111时,seg7_out输出字符码为0xED(即二进制的“11101101”),数码管对应显示“5”,而最高一位的“1”会让该数码管的小数点点亮。

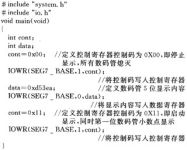

以上是第一种测试情况。第二种测试情况是将seg7的参数n设置成5,pos设置成1,用来驱动5个共阳极数码管显示。NiosⅡ IDE建立的用户测试程序如下:

程序编译通过后,同样在Modelsim中运行仿真结果,得到仿真波形如罔7所示。仿真分析时系统工作时钟(clk)设置为了50 MHz,数码管动态显示扫描频率(clkdisplay)设置为1 kHz。

与第一种共阴极显示情况相比,第二种共阳极显示时的寄存器写入过程是大体一样的。不同之处在于共阳极显示时的bit_control和seg7_out和输出极性正好与共阴极显示时的相反。

通过以上的实验,验证了自定制七段数码管动态显示接口元件功能的正确性。

4 结 语

在用Altera公司的SOPC Builder工具完成NiosⅡ软核SOPC系统设计时,可以用SOPC Builder中提供的元件来构建整个系统。但对于有些外部设备,SOPC Builder并没有提供对应的接口元件,此时,就可以使用SOPC Build-er工具的自定制用户元件功能来创建特定功能的接口元件。在本文中,针对数码管的显示,定制了一个七段数码管动态显示接口元件,可以用来驱动1~8个共阴极(或共阳极)数码管的显示,可以根据需要选择小数点显示的位置,每个数码管可以显示0~F之间的十六进制字符,并通过实验验证了其功能的正确性。