全方位解析Qsys系统集成工具——帮您解决三大尖锐问题

2012-04-11

作者:电子技术应用记者:陈颖莹

在采用FPGA进行设计时,您的设计团队规模是不是越来越大?您是否花费很多时间来尝试重新使用其他人的设计?您是否花费大量的时间来进行验证?如果是,那您一定要集中精力,接下来Altera亚太区产品市场经理谢晓东将介绍Altera如何帮助您解决这三个尖锐问题。

Altera亚太区产品市场经理谢晓东

您只需做定制逻辑——解决设计规模难题

随着各种应用对精度及速度等方面的需求越来越苛刻,芯片复杂度和规模在不断增加。以Altera高端FPGA Stratix系列为例,其规模(逻辑密度)从2002年到2010年增长了13倍。虽然这能让系统性能大大提升,但设计的工作量和复杂度也成倍增长,即使可以适当地增加人手,但毕竟设计团队的规模还是有限的,在设计工具一定的条件下,加上公司对于产品上市时间的压力越来越大,要按计划完成项目将会困难重重。

如何提高设计效能呢?提高设计抽象级是一个很实用的方法。从门级到寄存器传送级(RTL)再到IP级,现在很多设计其实都是一个搭积木的过程,用不同的IP拼成一个系统。但是即使到了IP级别,随着器件容量的增长、设计复杂度的增加,以及一些全球化的企业要在部门之间、项目之间分享一些子系统的需求不断增加,现有工具(SOPC Builder)就有待提升。谢晓东经理展示了没有采用Qsys和采用Qsys所需要做的设计工作对比图,如图1所示。可见,Altera系统级集成工具Qsys能帮助设计者把标准内核(存储、标准接口、处理器等)和胶合逻辑(用来做仲裁、中断控制、拓扑结构、带宽匹配、互联、桥接等)做好,大大减轻了工作量。Qsys让设计者把精力集中在定制逻辑上,这也是客户最关心的部分,用来做差异化,实现产品价值。

图1 没有采用Qsys和采用Qsys所需要做的设计工作对比图

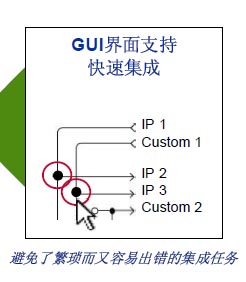

针对标准内核,Altera提供100多种Qsys兼容IP,如接口协议IP(PCIe、TSE)、存储器IP(DDR、DDR2、DDR3)、视频和图像处理IP、嵌入式IP(JTAG、UART、SPI、RS232)以及处理器IP。Qsys还自动完成繁琐、容易出错的集成任务,并且提供GUI界面支持快速集成。谢经理特别提到:“Altera致力于一个工具能支持所有的处理器。Altera自己拥有两种:带ARM Cortex-A9内核的双核SoC FPGA以及Nios II 软核处理器。此外还有Altera嵌入式联盟所支持的软核处理器(用FPGA模拟CPU),如MIPS、MIPS32、ARM Cortex-M1(ARM的策略就是希望把Cortex-M1放在FPGA上)、Nios II SC DO-254(对鲁棒性要求很高的应用,如军事)和Freescale Coldfire V1,如果希望用Nios II去做ASIC,Synopsys也提供License。

在胶合逻辑方面,Qsys自动完成繁琐、容易出错的集成任务。Qsys有图形化界面,接口(如时钟、复位,中断、抑制)能在GUI界面上快速集成,设计者只要把鼠标放在两个IP之间的接口,一点就可以了,操作十分简单,如图2所示。

图2 Qsys图形化界面

NoC和子系统级的设计重用——解决设计重用难题

设计者常常需要对原先成熟的设计进行更新和改进,也要使用别人设计的IP,会遇到设计重用带来的问题:一般需要重新设计接口以及需对各种修改过的设计提供支持。而Qsys提供Avalon总线接口(FPGA的)以及ARM的AMBA AXI3、AXI4标准总线接口,Qsys的芯片网络(NoC)体系结构可以帮助做FPGA与ARM之间的高性能互联,例如,对于Altera新推出的集成了ARM Cortex-A9处理器的SoC FPGA,Qsys将会发挥很大的作用。

Qsys还提供组件编辑器工具,可以把自己设计的RTL引入Qsys中,封装成一个IP来用。而且操作也是很简单的图形化界面。

Qsys在设计重用上的最大特色就是能做到子系统级别的设计重用。在设计一个超大系统时, 由于IP很多,用SOPC Builder时的界面会非常长,如果出现问题(如互联),要找前面的IP非常难,而Qsys可以做子系统的打包,把某一些IP打包成一个子系统(留一些接口出来),这样的层次化设计将会极大地方便设计人员。特别是一些国际化公司要在全球范围内共享设计,例如PCIe 的子系统,其中有PCIe 的IP、DMA 以及其他逻辑,可以通过Qsys把这部分打包之后重用,这是之前IP级设计工具做不到的。这也是一些国际化的客户选择Altera的原因。

定制GUI系统控制台——解决验证难题

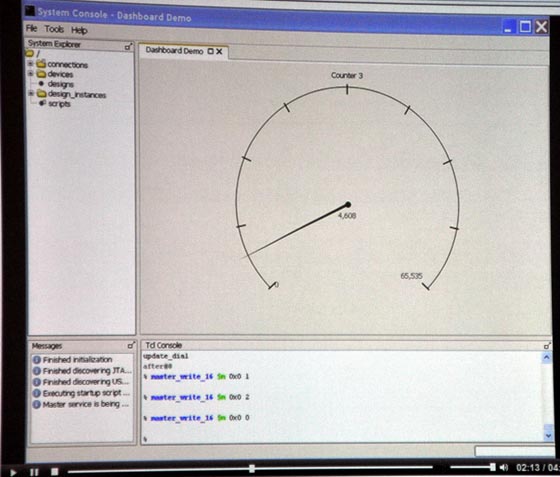

很多FPGA设计者都反馈:设计虽然很快的,但是系统验证和调试是很痛苦的过程。业界很多调试工具都是基于寄存器的调试,如果出问题要自己去分析问题大概出现在设计的哪一部分,再用SignalTap工具逐个寄存器进行读写操作,这使得工作量非常大,也存着许多不确定性。Qsys中有一个系统级调试工具——系统控制台,它提高了调试的抽象级,把设计看成不同的子模块,通过在总线上对地址进行读写操作,锁定问题出现在哪个模块,再用SignalTap去调试,从而大幅度缩短了验证时间。谢晓东表示:“其实,Altera很多调试工具,如收发器、外部存储器接口工具等,就是基于系统控制台开发出来的。”

很多时候调试都是很枯燥的命令行,而系统控制台的另一大特点就解决了这个问题,它提供定制图形用户界面,让客户定制自己喜欢的界面,使调试变得简单和享受。

图3 Qsys定制GUI系统控制台

Qsys巡回研讨会正在进行中

为了让更多的工程师切身体会Qsys的优势,Altera将在亚太区15个主要城市举办Qsys研讨会。研讨会的形式不单是演说,主要是可以让工程师们实际操作。他们可以使用Qsys开发一个嵌入式设计,并且通过实验看到在Qsys中使用PCIe的优势,让工程师在半小时之内开发一个基于PCIe的设计。谢晓东也特别让记者体验了一下Qsys的PCIe和DDR3参考设计。此外,Qsys的培训资料都是中文版的。

需要提醒广大使用Altera SOPC Builder的工程师们,虽然在老设计上还是可以用SOPC Builder去设计,但是Altera今后不会再更新SOPC Builder 的IP和支持器件,新的IP和器件都是放在Qsys上,Altera将为客户从SOPC Builder转到Qsys提供很多支持,如设计案例、文档和培训等。打开以前的SOPC Builder,就会提示是否转到Qsys,系统会帮你自动转换,当然有些地方需要少许修改,但不会花很长时间。Qsys代替SOPC Builder是必然的,所以赶紧开始使用吧!

图4 给工程师培训时用的开发板,由Altera合作伙伴友晶科技Terasic.提供的