从零开始走进FPGA——边沿检测技术

2015-02-04

一、为什么要讲边沿检测

也许,没有那么一本教科书,会说到这个重要的思想;也许,学了很久的你,有可能不知道这个重要的思想吧。很惭愧,我也是在当年学了1年后才领悟到这个思想的。

说实话,我的成长很艰辛,没有人能给我系统的指导,而我得撑起这一片蓝天,于是乎无数个漏洞,我一直在修补我的不足。我没能对自己满足过,不是 说我“贪得无厌”,而是,我不够“完美”。人可以不完美,但不可以不追求完美;或许终点永远达不到,但努力的过程,你一直在靠近完美;有方向感地奋斗,让 你永远立于不败之地。

也许我看的书不够多,但学校暑假那边关于的FPGA的书,我都翻过一遍了;特权的《深入浅出玩转FPGA》是我所看过的书中,唯一一本涉及到这个重要思想的书,也许这就是有过项目实战的人出的书,和官方理论教材的区别吧。

说起边沿检测,还有过一个故事:

话说七哥当年,去一家FPGA公司面试。考官给他一支笔,让他用逻辑门画出边沿检测电路。话音刚落,七哥持笔挥霍,数秒钟内画出了边沿检测的电路图,并且给出了完美的解释。瞬间思维的展现与重要应用的说明,让考官目瞪口呆。据说,七哥赢了,这之后,七哥便被那家公司录用了,一路牛逼,到了今天,证明了自己,取得了很大的成绩。

二、什么是边沿检测

所谓边沿检测,就是检测输入信号,或者FPGA内部逻辑信号的跳变,即上升沿或者下降沿的检测。这在FPGA电路设计中相当的广泛,几乎我每一个稍微完善的工程都会应用到这个思想;后续章节的讲解,也不少这个思维的应用。

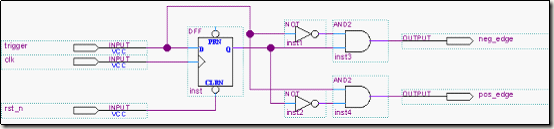

以下是七哥当年用决定自己工作的一张图,Bingo在Quartus II Block中用逻辑门画了出来:

如上图5个信号:

正常工作,没有复位的情况下,工作流程如下:

(1)D触发器经过时钟clk的触发,输出trigger信号,保存了t0时刻的信号。

(2)同时由trigger通过非门输出信号,保留了当前时刻t1的触发信号

(3)经过与门输出信号pos_edge,neg_edge

a) 只有t0时刻为高,且t1时候为低的时候,与门输出高,此时为下降沿。

b) 只有to时候为低,且t1时候为高的时候,与门输出高,此时为上升沿。

当然,在复位的时刻,DFF被复位,无法检测触发信号。

三、实现边沿检测的最优化

1. Block或Verilog实现

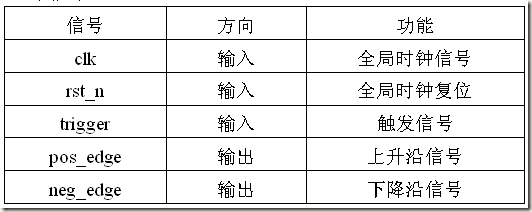

一般为了防止触发信号的波动,加几级触发器,消除抖动,使得信号更稳定。

此例程中,相对于上图多了触发器。其用触发器对信号打慢两拍,使得触发信号然后在进行相关的处理;再来检测边沿的上升沿,下降沿。

(1)用Block画图实现

(2)用verilog代码实现

edge_tech_design.v代码如下所示:

/*****************************************************

* Module Name : edge_tech_design.v

* Engineer : Crazy Bingo

* Target Device : EP2C8Q208C8

* Tool versions : Quartus II 11.0

* Create Date : 2011-6-25

* Revision : v1.0

* Description :

*****************************************************/

module edge_tech_design

(

input clk,

input rst_n,

input trigger,

output pos_edge,

output neg_edge

);

//Capture the rising_endge & falling_edge

reg trigger_r0,trigger_r1,trigger_r2;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

trigger_r0 <= 1'b0;

trigger_r1 <= 1'b0;

trigger_r2 <= 1'b0;

end

else

begin

trigger_r0 <= trigger;

trigger_r1 <= trigger_r0;

trigger_r2 <= trigger_r1;

end

end

assign pos_edge = trigger_r1 & ~trigger_r2;

assign neg_edge = ~trigger_r1 & trigger_r2;

endmodule

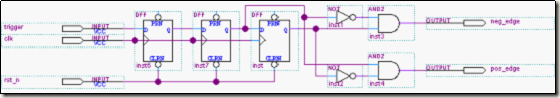

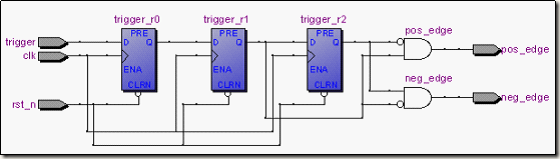

编译后,分析Quartus II RTL图,如下所示,与Bingo在Block用逻辑门设计的一样,说明了代码的正确性。

(3)Modelsim-Altera仿真图如下所示,在上升沿(下降沿)到来的时候,时序能够及时准确的检测到。

2. 边沿检测应用

边沿检测技术在项目应用中,非常低广泛。如要有效捕获信号跳变沿,边沿检测技术的应用是必不可少的。Bingo大致归纳了一下,有如下几个方面

(1)将时钟边沿使能转换为边沿检测使能,使时钟同步化。

(2)捕获信号的突变(UART,SPI等信号使能突变)

(3)逻辑分析仪中信号的边沿检测。

3. 实现指标及存在缺陷

没有十全十美的东西,也没有十全十美的电路、代码;本章节中所介绍的边沿检测技术亦如此。有如下缺陷:

(1)增大CLK信号可以增强边沿检测的效率,但不能滤去跳变的杂波。

(2)减少CLK可以有效滤去跳变的杂波,但不能及时检测到边沿跳变。

(3)增加DFF能更好的滤除杂波,寄存信号,但同时检测延时大。