文献标识码: A

DOI:10.16157/j.issn.0258-7998.2015.10.017

中文引用格式: 温杰,李锦明. 基于FPGA的实时图像边沿检测系统的实现[J].电子技术应用,2015,41(10):65-67.

英文引用格式: Wen Jie,Li Jinming. Realization of real time image edge detection system based on FPGA[J].Application of Electronic Technique,2015,41(10):65-67.

0 引言

边缘检测是图像处理、图像分析、模式识别、计算机视觉以及人类视觉的基本步骤之一,目的是为了发现图像中关于形状和反射或透射比的信息,目前已广泛应用于目标识别、机器视觉和运动目标跟踪等领域。在实时图像处理中,由于系统对实时性要求较高,单纯依靠软件来实现图像处理已无法满足实际工程的需求,所以目前较多采用FPGA或DSP等硬件设备来实现图像的实时处理。然而由于DSP只是对某些固定的运算提供硬件优化,其体系仍是串行指令执行系统,这些都使它在运行速度、吞吐量方面颇受约束,且不利于系统的扩展。而FPGA具有强大的并行处理能力和丰富的逻辑资源,能够实现硬件并行和流水线技术,在图像处理方面具有明显的优势,所以越来越受到人们的青睐。

本文采用FPGA作为控制处理器设计并实现了一种实时图像边沿检测系统。该系统具有处理速率快,稳定性强且易于扩展等优势,为更深层次的图像处理提供了便利。

1 实时图像边沿检测系统的总体方案

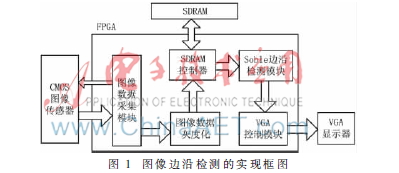

基于FPGA的实时图像边沿检测系统主要由图像数据采集模块、数据灰度化模块、SDRAM模块、Sobel边沿检测模块和VGA模块五部分组成,具体实现框图如图1所示。图像采集模块实现初始化相机并接收图像数据的功能;数据灰度化模块能够把采集到的图像转换为灰度图像;SDRAM模块控制对图像数据的缓存;Sobel模块实现像素梯度值的计算确定图像边沿并最终通过VGA模块进行显示。

2 实时边沿检测系统的实现

图像采集模块是系统的前端,包括相机配置模块和数据捕捉模块。系统上电后,系统配置模块通过SCCB(IIC)总线实现对相机的配置。配置采用三相写数据的方式实现:首先写入CMOS传感器的物理地址,然后写入需要配置的寄存器地址,最后再写入数据即可完成该寄存器的配置。根据以上方法,依次对相应的寄存器进行配置,CMOS传感器就可以正常地采集图像并通过相机接口传回到FPGA的图像捕获模块中。图像捕获模块根据像素时钟同步信号,确定哪些时段中数据有效,产生数据有效信号DVAL,并把图像数据传到下一模块进行进一步处理。

2.1 图像灰度化处理

由于相机采集到图像为RGB模式的彩色图像,而边沿检测系统是检测图像中灰度变化剧烈的像素点,所以有必要对图像进行灰度化处理。图像灰度化处理不仅能够减少图像处理的运算量,而且不会影响边沿检测的效果。常用的灰度化方式有加权平均法、平均值法和最大值法。系统采用加权平均法对图像进行灰度化处理,该方法从人体生理学角度出发,对RGB三分量进行加权平均,从而得到较为合理的灰度图像。其数学表达式如式(1)所示:

Gary=0.299R+0.587G+0.114B(1)

在实际应用中,由于浮点型运算实现较为困难,所以需要进行整数转换。系统采用7位精度的转换公式对图像进行灰度处理,其转换精度与8位的转换公式相同,但转换速度更快。具体的实现公式如式(2)所示:

Gary=(38R+75G+15B)>>7(2)

图像灰度化的实现过程采用QuartusII中的乘加器实现,顶层文件如下所示:

MAC_3 q0(.dataa_0(ired),

.dataa_1(igreen),

.dataa_2(iblue),

.datab_0(7’d38),

.datab_1(7’d75),

.datab_2(7’d15),

.result(wMono),

.clock0(iclk));

其中:dataa_0~2分别代表一个像素点的RGB分量,datab为以7为精度的加权系数,result右移7位即为输出的像素灰度值。

2.2 图像缓冲模块设计

在图像处理系统,由于数据的输入速度与系统的处理速度往往不匹配,需要一个大容量存储器作为图像数据的缓存。根据图像数据的特点,设计者常常采用SRAM或SDRAM对图像数据进行缓存。然而由于SRAM的容量与价格的限制,不利于系统的扩展,本系统采用SDRAM芯片MT48LC8M32作为系统的缓存模块。该芯片单片容量为256 MB,配置为2 M×32×4bank,刷新计数为4 K。接口连接情况如图2所示。

SDRAM控制器包括缓冲模块和SDRAM控制模块。缓冲模块采用2个异步FIFO(Wr_FIFO和Rd_FIFO)作为图像数据的输入输出缓存,实现了从低频数据输入到高频数据写入SDRAM,以及高频数据读取到低频数据输出的转换。虽然SDRAM在同一时间段只能进行读或写操作,但系统采用的SDRAM控制模块的工作时钟为108 MHz,高于数据输入输出时钟的2倍,所以从外部看,SDRAM能够支持同时读写操作。FIFO控制模块主要包括以下内容:(1)当有外部图像数据输入请求时,数据写入Wr_FIFO中。(2)当有外部图像数据输出请求时,输出Rd_FIFO中的数据。(3)当Wr_FIFO中数据个数大于256时,请求写入SDRAM,响应后开始突发写入数据。(4)当Rd_FIFO中数据个数小于256时,请求读取SDRAM,响应后开始突发读取SDRAM数据。

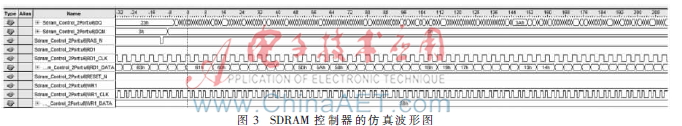

SDRAM控制模块包含control_interface、command、sdr_data_path 三个功能子模块。Command命令接口模块与顶层进行信息交互,并对接收的信息进行译码,产生读、写、预充电等命令与访问地址等信息;control_interface控制接口模块根据command的命令与参数实现对SDRAM的控制;sdr_data_path数据位宽控制模块根据外部DQM信号选择数据读写的宽度。系统采用SignalTapII对SDRAM控制器进行了验证。图3为SignalTapII采集到的数据波形图,结果符合预期要求。

2.3 Sobel边沿检测的实现

Sobel边沿检测算法是一种基于梯度的图像边沿检测的方式,该算法容易在硬件上实现,且能够平滑一定的噪声,边沿检测效果较好。Sobel 算子的边缘检测是在图像空间内利用 2 个方向模板与图像进行邻域卷积来完成的。这两个方向模板,一个检测水平边缘,另一个检测垂直边缘。它们的方向梯度算子模板如下:

水平方向梯度模板 垂直方向梯度模板

以模板内的数字为权重系数,与图像平面对应的像素值相乘可以求出水平梯度PX与垂直梯度PY。然后根据梯度计算公式 , 求出梯度值|G|,并与预先设定的阈值进行比较从而确定图像的边沿。

, 求出梯度值|G|,并与预先设定的阈值进行比较从而确定图像的边沿。

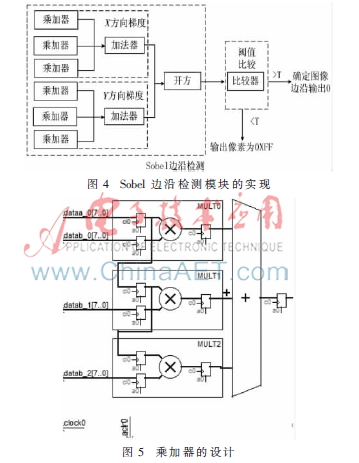

根据以上分析,系统利用QUARTUS中的IP核模块并结合硬件语言编程实现了Sobel边沿检测模块的设计,具体实现过程如图4所示,其中乘加器是计算像素梯度值的主要模块。一个乘加器中包括3个乘法运算模块和1个加法运算模块,分布情况如图5所示,其中dataa为输入的行像素,datab为方向模板的权重系数。一个乘法器模块可以实现一行像素与其对应的模板系数的卷积运算。边沿检测模块需要6个乘加器来实现X方向和Y方向的梯度值运算。开方模块结合X方向与Y方向的梯度,确定该点的像素梯度值。然后再将得到的梯度值与阈值进行比较,从而确定图像的边沿。

3 实验结果与分析

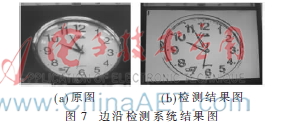

为了验证系统的正确性,采用SignalTapII对边沿检测结果进行了仿真,结果如图6所示。其中边沿检测模块选取的阈值为0X5B,sqrt0|q为Sobel边沿检测模块得到的像素梯度值。如果梯度值大于阈值,则oDATA输出0X00h,反之则输出0XFFh。仿真结果与实际相同。系统采用VGA显示器作为图像显示的终端,通过设计VGA控制器,边沿检测的结果以640*480@60Hz的格式进行显示,得到如图7所示结果。通过对比图7中的两幅图可以看出,该系统的检测效果较好,能够有效地识别图像的边沿。

4 结论

本文基于FPGA设计了一种实时图像边沿检测系统,搭建了以FPGA和SDRAM为核心的硬件平台,并通过硬件语言编程与调用可编程宏模块在硬件上实现了实时图像的边沿检测功能。结果表明,该系统检测效果较好,能够满足系统对于实时性的需求,可以作为后续图像处理,如运动目标跟踪等研究的重要支撑。

参考文献

[1] 朱秀昌,刘峰.数字图像处理与图像通信[M].北京:北京邮电大学出版社,2014.

[2] 王建庄.基于FPGA的高速图像处理算法研究及系统实现[D].武汉:华中科技大学,2011:5-10.

[3] 齐榕,齐敏.数字图像边缘检测的FPGA实现[J].电子设计工程,2013,21(19):178-179.

[4] 王德胜,康令州.基于FPGA的实时图像采集与预处理[J].电视技术,2011,35(3):32-33.

[5] 杨新华,寇为刚.基于FPGA的Soble算子图像边缘检测算法[J].仪表技术与传感器,2013(1):102-104.