文献标识码: A

文章编号: 0258-7998(2014)08-0017-03

PowerPC具有外设丰富、处理能力强以及便于移植Linux等操作系统的特点,而现场可编辑逻辑门阵列FPGA具有处理能力强、在线可编程等特点。因此,在复杂工业控制、路由器等诸多领域,采用PowerPC+FPGA的架构得到了广泛的使用。众所周知,FPGA多采用静态随机存取存储器SRAM(Static Random-Access Memory)工艺,掉电后配置数据将丢失。因此,系统每次上电后都必须进行数据配置。此外,随着FPGA规模越来越大,配置数据已达到几十甚至上百兆比特,常用的串行配置边界扫描(JTAG)等方式在很多场合下已无法满足需求。若设计中需要对多片FPGA进行配置,则更为复杂,耗费时间更长。目前,主流PowerPC具有丰富的通用输入/输出口GPIO(General Purpose I/O),自带位宽达32 bit的本地总线(Local Bus),且在其上移植Linux等操作系统方便快捷。因此,可以利用PowerPC本地总线对多片FPGA进行快速并行配置。

1 FPGA配置方式

1.1 常用的配置方式及特点

目前主流的FPGA厂家有Xilinx、Altera等公司。虽然不同厂家、不同系列的FPGA芯片配置方式或多或少存在一些差异,但是大体来说配置方式包括JTAG模式、主动模式以及被动模式[1-2]。不同模式之间通过模式选择控制引脚进行选择,具体设置方式由相应的芯片资料给出。

JTAG模式使用最方便,使用下载器就可以很方便地将计算机生成的配置数据下载到FPGA中。但是这种模式没有存储芯片,掉电后需重新通过计算机下载,所以这种配置方式多用于调试阶段;主动模式下FPGA作为控制器,产生配置时钟和控制时序,从配置器件等外部设备中读取配置数据,进而将数据下载至FPGA。根据数据采用的是串行还是并行模式,又分为主动串行模式和主动并行模式。被动模式是由外部配置器件产生时钟和控制时序控制整个配置过程,FPGA只是被动地接收配置数据。同样根据数据采用的是串行还是并行模式(对应Xilinx FPGA的SelectMAP模式),又分为被动串行和被动并行模式[3-4]。当然,根据数据是同步还是异步的,还可以进一步细分。

串行(主串或从串)模式具有配置信号少、配置电路简单等优点。但是FPGA 在配置时钟的1个上升沿只能接收1 位配置数据,显然该配置方式速度较慢;并行模式配置信号线比较多,但是配置速度较快,在高密度的FPGA系统中,更适合采用并行模式。并行模式除了采用专用配置芯片外,还可以采用微处理器或者CPLD控制Flash等存储器对FPGA进行配置。由于主流PowerPC具有丰富的GPIO口和32位总线,若运行Linux系统,则可以进一步扩展CF卡或者SD卡,将配置文件存放在CF卡或者SD卡中,而不用Flash芯片。在精简系统设计的同时,使得程序升级维护更方便,在工程实践中更具有实际意义。

1.2 FPGA配置文件

以Xilinx FPGA芯片为例,其配置文件可由集成开发环境ISE生成。常用的配置文件格式(后缀名)包括:.bit、.rbt、.bin、.mcs以及.hex等格式。其中.bin和.bit文件都是直接向FPGA配置的文件。.bit文件除包含有真正的配置数据外,还在文件开头添加了头部冗余信息,包含当前ISE工程的名字、器件型号、编译时间等信息,主要用于JTAG下载;.bin文件只包含了原始配置数据的二进制文件,实质上就是去除了头部冗余信息的.bit文件。.bin文件也由文件头和配置数据组成,其中文件头主要包括位宽检测和同步字等,第二部分才是真正写入FPGA的配置文件,这种格式常用于利用微处理器对FPGA进行并行下载。.rbt格式为.bit文件的ASCII格式;.mcs文件包括地址和校验信息,主要用于专用配置芯片进行程序烧写;.hex文件只包含FPGA的配置数据,也是给用户使用的。显然,利用PowerPC对FPGA进行配置时要选择.bin格式文件。本文采用被动SelectMAP模式对Xinlix Virtex-6 FPGA进行配置。

2 硬件设计与实现

2.1 并行配置的相关时序

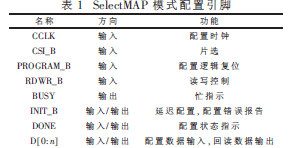

Xilinx SelectMAP模式实质上就是并行配置模式,它以字节为单位将配置数据写入FPGA。在从SelectMAP模式下,外部数据源向FPGA提供时钟(CCLK)、编程(PROGRAM_B)、片选(CSI_B)、读/写(RDWR_B)、初始化(INIT_B)以及数据信号D[0:n](在8 bit、16 bit、32 bit模式下,n分别对应7、

15、31)。表 1给出了SelectMAP模式下的配置引脚功能。其中信号方向是相对于FPGA而言的。

各控制信号的具体含义如下[5]:

(1)PROGRAM_B:编程复位信号。在上电过程中为边沿敏感,上电后为低电平有效。该信号拉低完成芯片的复位,低电平保持时间为0.5 ?滋s乘以配置文件的帧数。对Virtex-6芯片,大概几十毫秒(经实测在1 ms以内)。复位完成后,内部INIT_B抬高。

(2)INIT_B:初始化信号。为双向信号,在重启或者编程初始化(PROGRAM_B=0)过程中,用来指示FPGA是否已经完成配置初始化。作为输入信号,将INIT_B拉低来推迟对FPGA的配置。一般情况下,只需在PROGRAM_B=0后等待一定时间即可完成初始化。为了简化设计,在本设计中INIT_B只用于输入。

(3)CSI_B:片选信号。低电平有效,CSI_B=0表示总线允许。

(4)RDWR_B:读写控制信号。RDWR_B=0表示总线写入,RDWR_B=10表示总线读出。需要注意的是,拉低RDWR_B信号之前,必须确认CSI_B=0,否则可能会导致数据丢失。

(5)BUSY:握手信号。当配置时钟频率超过50 MHz时,利用本信号控制写入或者读出速度。

(6)DONE:配置状态指示信号。数据正确配置后,DONE=1。

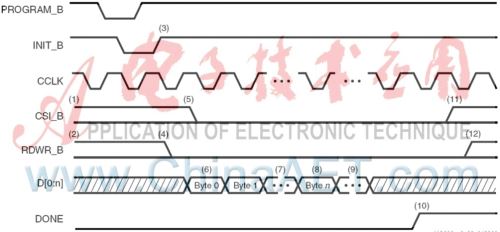

图 1给出了连续并行配置的时序图。

图1 SelectMAP 模式连续配置时序图

2.2 基本思想与硬件设计原理

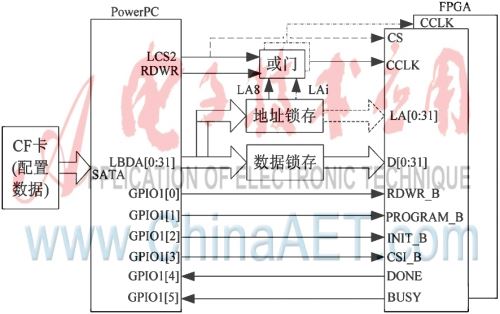

由表1和图1可以看出,FPGA在CSI_B、PROGRAM_B、RDWR_B以及INIT_B的控制下,在时钟CCLK的上升沿时刻将配置数据写入FPGA。以上4个控制信号可以利用PowerPC的GPIO口生成,虽然CCLK也可以用GPIO生成,但是由于GPIO口输出的数据和总线数据都要经过锁存、电平转换等,在高速设计中,可能会产生意想不到的结果,或者为了保证时序的正确性而牺牲效率。考虑到PowerPC总线进行写操作时,其对应的片选信号LCS以及RDWR信号都为低电平,而进行其他操作时,RDWR为高电平。此外,通过对PowerPC的总线控制寄存器进行设置,可以使LCS信号滞后于RDWR拉高。因此可以将LCS与RDWR进行“或操作”产生配置时钟CCLK。写命令发出后,由于LCS滞后于RDWR信号,可以保证数据能够被正确写入FPGA。

基于以上时序分析的结果,设计了图2所示的原理框图。通过SATA接口相连的CF卡用来存放配置数据,当然也可以用SD卡。CF卡或者SD卡可以很方便地从卡座上拔下,使得程序维护升级非常方便,甚至非专业人员都能完成程序的升级。在调试过程中,数据可以直接存放在调试计算机中,利用NFS协议调试,方便快捷。为了能够区分多片FPGA,可以将不同的地址线与LCS、RDWR一起进行或运算,实现片选。地址线为高电平时,时钟始终为高电平,对应FPGA芯片不被选中(芯片较多的情况下,也可采用译码器来实现片选)。向相应的地址写入数据,就实现了片选。需要注意的是,在FPGA配置过程中,无需对地址进行操作,地址仅仅是作为片选信号使用。此外,图中的数据总线不仅在配置期间使用,在访问FPGA时也要使用。为了更好地利用同一条总线实现对FPGA的配置和访问,LCS2同时连接至多片FPGA的片选,在配置期间与其他信号一起产生配置时钟,在访问期间起到片选的作用。图中的虚线表示在PowerPC访问FPGA时采用的信号线,在配置期间不使用。

图2 PowerPC并行配置FPGA原理框图

3 软件设计与实现

3.1 软件设计要点

针对PowerPC、Linux操作系统以及FPGA的特点,在软件设计过程中,应注意以下几点:

(1)利用内存映射函数替代驱动程序设计。通常情况下,Linux内核通过驱动程序来实现对外部设备的输入/输出操作。利用PowerPC对FPGA进行并行配置,当然也可以利用驱动程序来实现。不过由于驱动程序编写比较繁琐,使用起来也不够灵活,所以可以利用Linux内存映射函数mmap[6],将包括系统配置寄存器等相关寄存器在内的一块内核空间映射到用户空间的一段内存区域。映射成功后,用户对这段内存区域的操作可以直接反映到内核空间。具体来说,经过映射后,用户可以通过对相应的内存地址进行操作,实现对系统配置寄存器、GPIO寄存器、本地总线控制器寄存器等的配置和访问,而无需利用驱动程序,使得配置程序得以简化。

(2)妥善处理字节序和比特序问题。在FPGA配置过程中,因涉及到众多软硬件,要特别注意接口过程中的字节序和比特序问题。以MPC8377 PowerPC为例,其为大端、最低有效位LSB(Least Significant Bit)在前模式,而Virtex-6系列FPGA为小端、LSB在前模式。大端模式是在写内存时在内存低地址处存放数据的高位字节,高地址处存放低位字节;而读内存时,将内存的高位地址视为目标数据的低字节,将低位地址视为高字节。小端模式正好相反。ISE生成的.bin文件与FPGA一致,也为小端模式。因此通过PowerPC将数据下载至FPGA时必须要进行大小端转换,即字节序转换。因PowerPC和FPGA均为LSB在前模式,因此无需作比特序的转换。也就是说,利用ISE生成.bin文件时不需做bit swap处理。

(3)正确配置寄存器。使用本地总线首先必须要正确配置本地总线的本地访问窗口基址寄存器、本地访问窗口属性寄存器、本地总线控制基寄存器和可选寄存器。若片选信号为LCS2,则这4个寄存器分别为:LBLAWBAR2、LBLAWAR2、BR2和OR2。其中,LBLAWBAR2就是本地访问窗口的基址,可以直接设置为LCS2对应的地址;LBLAWAR2是本地访问窗口属性寄存器,这个寄存器主要定义了允许访问窗口的大小,主要由需要配置的FPGA片选对应的地址空间决定;BR2主要是对总线的位宽进行设置,位宽有8 bit、16 bit以及32 bit 3种选择;OR2也比较重要,决定了外部存储器写访问期间LCS2 和LWE 何时无效。举例来说,在bit21 22=00的情况下,对bit20置位,可使LWE提前总线1/4个周期。这样可以确保在LCS2拉高前,数据能够被正确写入FPGA。当然,也可以对bit21 22通过设置其他的值,实现LCS2的不同延时。

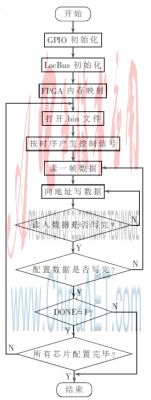

3.2 软件流程

按照上述思想,给出了软件流程如图3所示。

4 调试要点

(1)注意大小端问题。利用MPC8377对FPGA进行配置时,总线宽度可以是8 bit、16 bit、32 bit之一。8 bit模式下不用关心字节序,16 bit和32 bit必须进行大小端转换。关注同步字即可确定字节序和比特序。在实际的调试过程中,应抓住一点,对于FPGA,其引脚上的同步字为D[31..0]=0x5599AA66。若FPGA和PowerPC的引脚是顺序对应的(即D0对D0,D31对D31),那么对于PowerPC,需要在总线上传输的数据应该是0x665599AA。所以需要将.bin配置文件中的同步字0xAA995566进行大小端转换后变为0x665599AA,然后通过PowerPC传送到FPGA对应的引脚上即可。

(2)善于利用JTAG口。FPGA的JTAG既可以用来下载数据,也可以借助它来查看FPGA配置状态寄存器的值,其中包括总线宽度、配置模式等参数。在利用PowerPC对FPGA进行配置的过程中,关注配置寄存器的相关状态,可以得到对应的信息。比如配置模式在INIT信号由低变高时被采样,总线宽度是在检测到位宽信号后被采样。若位宽显示正常,说明配置数据已能被正确写入FPGA;若配置还是错误,就应该检查字节序、配置文件等是否正确。

(3)利用NFS协议调试。调试过程中,可以将程序放在本地计算机中进行编译,通过NFS协议,PowerPC可以运行存放在主机中的文件。等调试完毕后,可将应用程序、配置文件一并存入外接的CF卡中,以提高调试效率。

此外,在调试阶段可以将PROGRAM、INIT等信号间隔适当拉大,调整OR寄存器的值,适当降低配置速率,等配置成功后,再对相关值进行调整和优化,以提高配置速度。

本文给出了一种利用PowerPC对多片FPGA进行并行配置的简单方法。经实测,配置1片Virtex-6 XC6VS-

X475T芯片,若采用JTAG模式,需要48 s,而采用文中给出的并行配置方案,可将配置时间缩短至1 s左右,极大地缩短了配置时间。该方法也同样适用于Xilinx其他系列的芯片以及Altera系列芯片。

参考文献

[1] Altera.Device configuration schemes[EB/OL].(2013-10-08) [2014-03-30].http://www.altera.com.cn/support/devices/configuration/schemes/cfg-matrix.html.

[2] Xilinx.Configuration for Virtex-6 FPGA[EB/OL].(2013-08-25)[2014-03-30].http://www.xilinx.com/products/design_resources/config_sol/v6/config_v6.htm.

[3] 葛飞,何辅云,夏玉宝.FPGA被动并行配置控制器的研究与实现[J].合肥工业大学学报(自然科学版),2008,30(4):39-41.

[4] 赵勇,孟李林,李小龙.Cyclone IV系列FPGA的配置方式及其工程应用[J].微型机与应用,2013,32(19):25-28.

[5] Xilinx.UG360 Virtex-6 FPGA configuration user guide[EB/OL].(2013-11-27)[2014-03-30].http://www.xilinx.com/support/documentation/user_guides/ug360.pdf.

[6] 韩超,魏治宇,廖文江.嵌入式Linux上的C语言编程实践[M].北京:电子工业出版社,2009.

(收稿日期:2014-04-22)