摘 要:提出一种基于SOPC的数据发生系统及其PCI接口的设计方案,详细介绍了系统主要模块的硬件设计方法,实现SOPC系统中定制用户自定义主从外设及其通过相应的主从端口与Avalon。总线的连接,并在EDA工具QuartusⅡ和ModelSim平台上用硬件描述语言VHDL语言对该方案中的基本模块,如数据产生,乒乓结构和PCI9054接口逻辑进行了逻辑综合及功能仿真。可以在本系统的基础上,通过软件的完善,实现复杂的非常规类型数据的产生,提高了系统的适应性和灵活性,有利于参数的修改和系统升级。

关键词:SOPC;Avalon总线;乒乓结构;PCI9054

0 引 言

可编程片上系统(SOPC)是一种特殊的嵌入式系统,因为SOPC是片上系统(SoC),即由单个芯片完成整个系统的主要逻辑功能;SOPC是可编程系统,具有灵活的设计方式,可裁减,可扩充,可升级,并具备软硬件在系统可编程的功能;SOPC结合了SoC和FPGA的优点,涵盖了嵌入式系统设计技术的全部内容;SOPC涉及目前已引起普遍关注的软硬件协同设计技术。

现以数据发生系统为例,介绍采用SOPC技术,以硬件描述语言为主要手段,产生伪随机序列的设计方案。研究了伪随机序列的产生,两片SRAM乒乓结构存储以及通过PCI9054芯片与PC机之间数据传递等模块的硬件实现问题。

1 基本原理和系统的整体结构

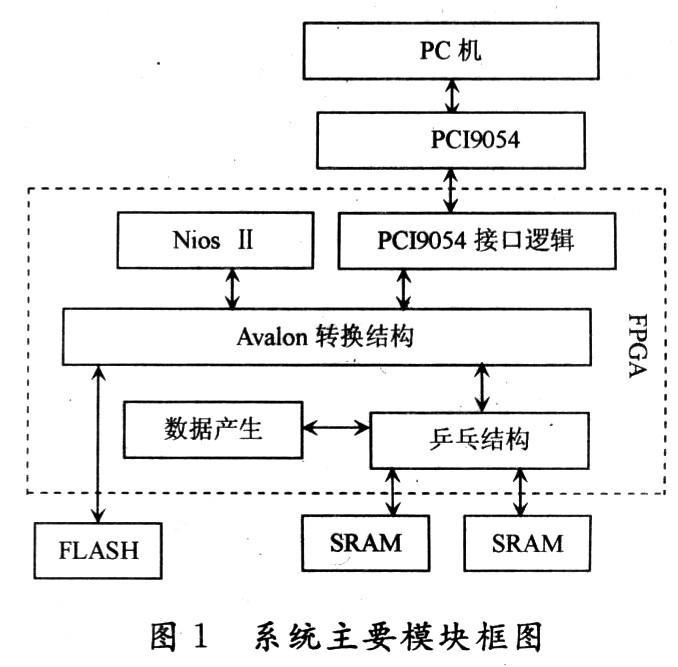

本系统的主要模块框图如图1所示,SOPC系统采用Altera的CycloneⅡ系列的芯片。系统包括NiosⅡ软核处理器,扩展的程序存储器FLASH,数据存储器SRAM,以及用户自定义逻辑如PCI9054接口逻辑模块、数据产生模块、乒乓结构模块等,并通过Avalon总线连接起来。数据产生模块产生伪随机序列,该数据存储到两片片外扩展的SRAM中,PCI9054接口逻辑将数据从SRAM中读出后通过PCI9054接口芯片传输到PC机中,其中SRAM中数据的写入和读出是通过乒乓结构模块控制的。

由于PCI总线协议比较复杂,该系统采用PCI接口专用芯片PCI9054,用于PCI总线的控制。为了实现数据的高速传输,采用了DMA传输模式。在该模式中,PCI9054既是PCI总线的控制器又是本地总线的控制器,所以其与FPGA之间的接口逻辑模块设置为AvaIon主外设,控制SRAM的读操作。

FPGA的片上资源很宝贵,所以数据的存储采用了片外扩展SRAM。由于数据为16 b,而且为实现数据的高速传输,采用了两片256K x 16 b的SRAM(IDT71V416)构成乒乓结构,以用作系统的数据存储器。为保证整个系统高速运行以及以后升级的需要,选用了存取时间为10 ns的IDT71V416。

2 系统主要硬件设计

2.1 数据产生模块

该模块的逻辑功能由VHDL语言设计实现,可以通过修改该模块的设计产生所需要的数据,本系统产生的数据为伪随机序列。模块的逻辑功能是:先产生8 b的伪随机数,再将所产生的数据通过D触发器组合成16 b的数据。该系统采用了非线性反馈的移位寄存器,即全状态移位计数器来产生所需要的伪随机数。这种计数器利用了移位寄存器的所有状态,能够自启动,不需要额外输入。这种伪随机序列发生器,可大大简化结构,提高可靠性,易于实现。

全状态移位计数器的状态变化规律有两个特点:状态的最高位由反馈函数确定;余下的各位由原态移位得到。该系统采用的反馈函数为:

![]()

式中:Qi(i=1,…,8)为电路的现态。

2.2 乒乓结构模块

2.2.1 乒乓结构的硬件实现

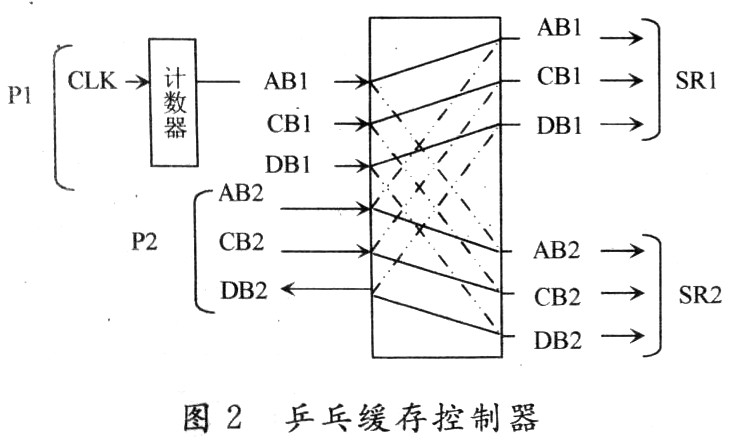

为了提高系统的传输速率,两片SRAM构成了乒乓缓存结构,即在一片执行写操作的同时,另一片在执行读操作。乒乓结构模块的原理如图2所示,P1口与数据产生模块相连接,仅具有写入功能,P2口设计为Avalon从端口,与Avalon总线相连仅具有读出功能。

对于数据产生模块而言,由于仅具有并行数据的输出,没有地址和控制信号端口,故它无法直接对SRAM进行写操作,因而要求乒乓结构模块有地址产生功能。P1口的CLK作为计数器的脉冲源,计数器的输出作为SRAM的地址。DBl连接数据产生模块的输出端。CBl为控制信号,因为P1口只有写入功能,所以其we_n恒接低,oe_n恒接高。

P2口为只有读出功能的Avalon从端口,所以AB2为从端口的地址线address;DB2为数据线readdata;CB2中的we_n为读信号线read,oe_n恒接低。由于两片SRAM始终处于工作状态,所以相应的片选信号chip_select_n恒接低。

两片SRAM在P1口和P2口之间的切换的控制信号即chipselect,由计数器产生。当计数值小于262 144时,chipselect接低,SR1与P1口相接,SR2与P2口相接;当计数值在262 144~524 288之间时,chipselecl接高,SR1与P2口相接,SR2与P1口相接。当计数值到达524 288时,计数器清零。

2.2.2 Avalon从外设的端口信号设计

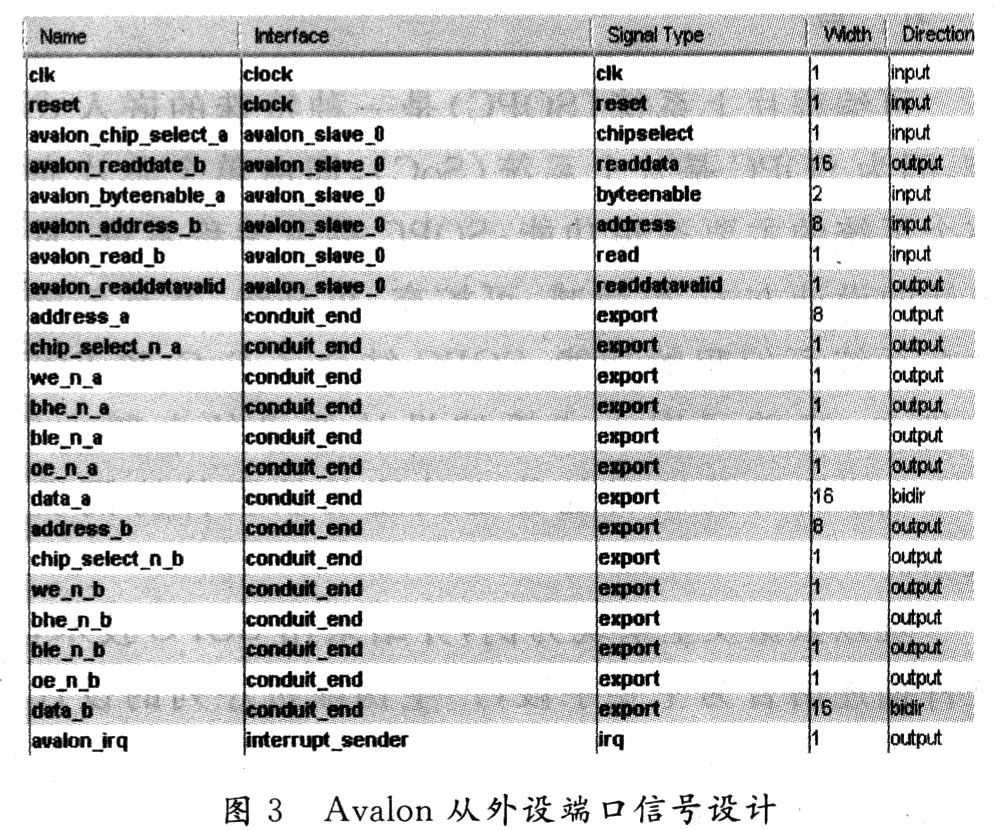

系统中,数据产生模块与乒乓结构模块结合为一个模块,通过P2口挂在Avalon总线上。该模块的信号列表如图3所示。其中,avalon_slave_O接口类型的信号与Avalon总线相连接,而conduit_end接口类型的信号与SRAM相连接。图3中的Avalon从端口即为P2口,采用了流水线读传输的模式,这种模式能在前一次传输返回readdata前开始一次新的传输,增加了带宽。

2.2.3 动态地址对齐及其时许设计

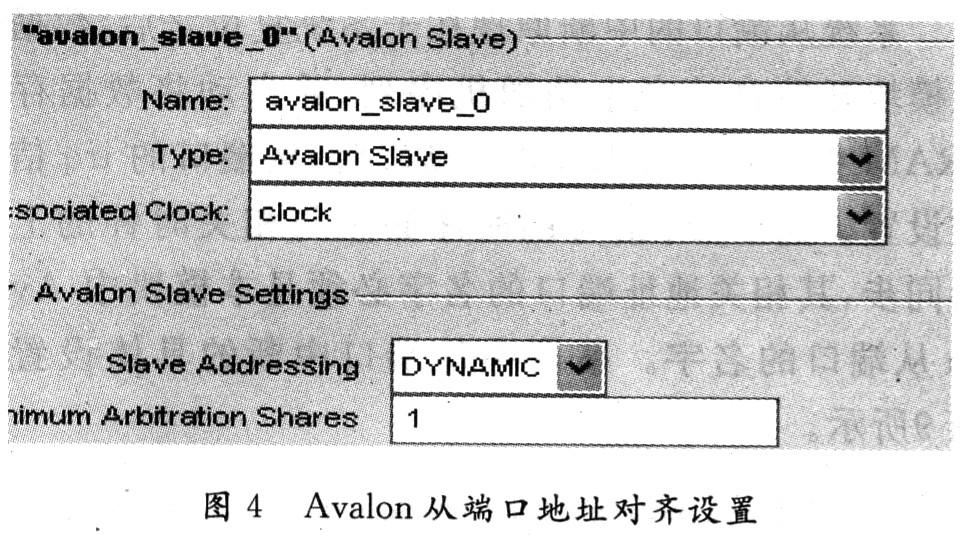

Avalon总线模块能够适应主从外设的不同宽度和不匹配的数据宽度。当系统中村子不匹配的存储口时,要考虑地址对齐问题。对于存储器类型的外设,采用动态地址对齐方式。IDT71V416型SRAM是静态RAM,属于存储器型外设,所以该Aalon从端口采用动态地址对齐方式,如图4所示。选用动态地址对齐方式,使得主端口能连续地对从外设进行读写,并使系统将外设认作存储器型外设。

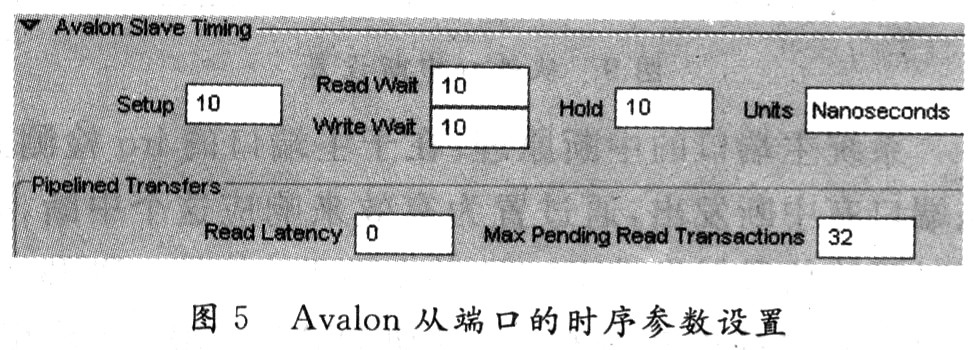

根据IDT71V416型SRAM手册中读写时序的各时间参数值设定set up,read wait,write wait及holdtime的时间均为10 ns,使该端口既符合Avalon总线读写时序的要求,又符合IDT71V416型SRAM的读写时序的要求,如图5所示。

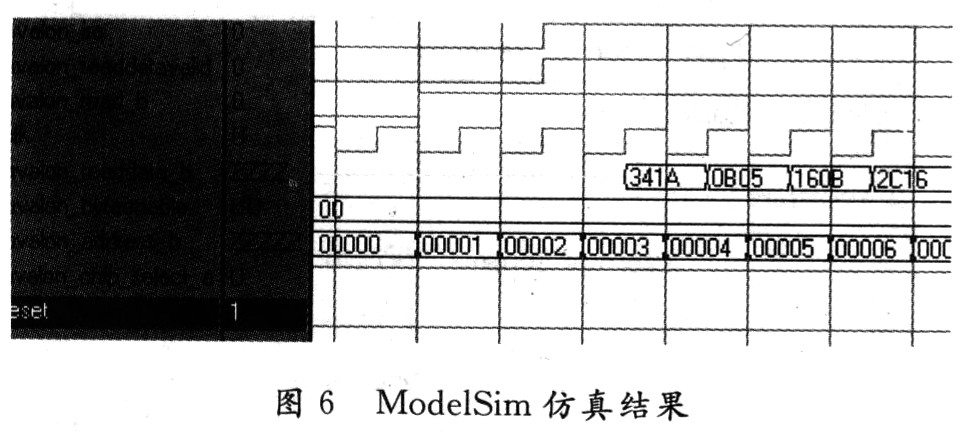

数据产生,乒乓结构和两片SRAM三部分的组合在ModelSim中的仿真结果如图6所示。avalon_ad-dress_b不变时是在执行第一次写操作,此时没有数据读出,所以avalon_readdata_b值为高阻;avalon_ad-dress_b开始变化时,表示一片SRAM已经写满,正在执行该片的读操作,而另一片在执行写操作,avalon_readdata_b为系统生成的数据。

2.3 PCI9054接口逻辑模块

PCI总线作为PC机与外部设备之间重要的连接总线,具有数据传输稳定灵活,传输速度快,即插即用和良好的扩展性等特点,被广泛地用在各种与PC机互联的设备中。该系统采用的PCI9054芯片口可以将复杂的PCI总线接口转换为相对简单的用户接口,大大缩短了设计周期。

2.3.1 本地总线状态机设计

由于PCI9054的DMA传输方式只适宜于做单次传输,故该系统采用了DMA结合中断的方式传输数据。由于数据的存储采用了乒乓结构,可以在一片SRAM执行DMA传输的同时执行另一片写操作,这样不会造成数据丢失,状态也比较容易控制。

系统复位后,数据产生模块开始产生伪随机序列,产生的数据直接存入SRAM中。此时,计数器同步计数,当计数值每一次达到262 144时,也就是一片SRAM已经存满时,SOPC系统就会触发PCI9054中断请求信号LINT#,CPU响应中断,发出读命令、要读取的字节数、地址信号等。PCI9054:先通过LHOLD申请本地总线的控制权,SOPC系统通过LHOLDA响应,使PCI9054.获得本地总线的控制权。PCI9054将PCI地址空间映射到本地地址空间,接着启动本地总线的DMA传输。

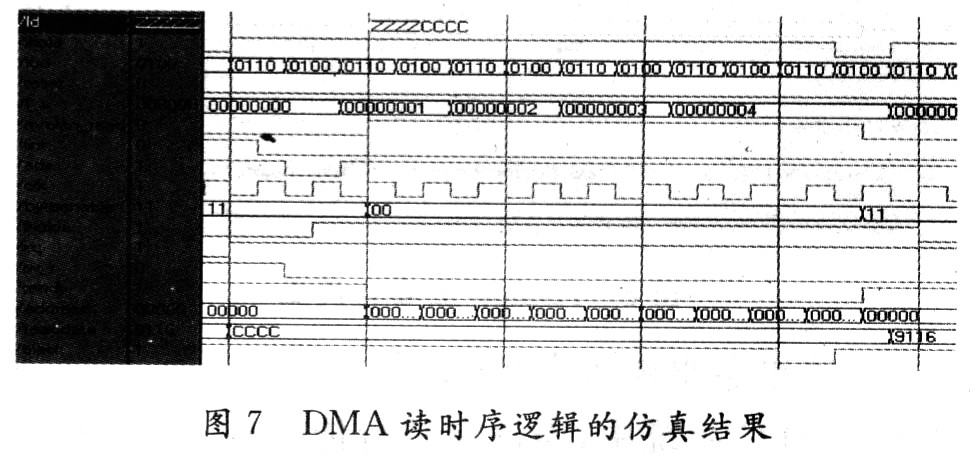

该系统采用VHDL语言,实现了DMA读传输本地端的时序控制状态机设计。状态0为空闲状态(i-dle),若LHOLD信号被置1,则转到状态1,否则留在状态0。状态1为总线保持状态(hold),在此状态下应将LHOLDA信号置l。如果信号ADs为O且LW_R为0,则转到状态2。状态2为DMA读状态(DMA_read),在此状态下应将READY信号和模块内部信号avaIon_read置l,从而使AvaIon主端口的master_read置1,表示Avalon主外设发起读传输。如果BLAST为1,则表明此次DMA读取还没有完成,继续留在状态2;如果BLAsT为0,则表明此次DMA读取完成,转到状态3。状态3为DMA读操作完成状态(end cycle),当LHOLD被置0时,表示PCI9054不再请求本地总线,则转到状态0;当BLAST为0且LHOLD为1时,则表明PCI9054还要进行DMA读操作,则转到状态1继续。其中的DMA读操作的时序逻辑的ModelSim仿真结果如图7所示。

2.3.2 Avalon主外设的端口信号设计

该系统中,PCI9054控制数据从本地总线上读出,先到PCI9054的FIFO中,再将FIFO中的数据传输到PCI总线上。因此SOPC系统中的PCI9054接口逻辑模块为Avalon主外设,主端口通过address,read,wait-request等信号发起Avalon总线上的读操作,从而控制Avalon从外设即乒乓结构模块的读操作。

由于本系统定制的从外设采用了流水线读的传输模式,为了使端口传输模式匹配,主外设也采用流水线读的传输模式。流水线主端口一个必须的信号为readdatavalid,Avalon交换结构向主端口发出readdat-avalid,以表示readdata信号正在提供有效的数据。

本系统定制的Avalon主外设构成模块主要由5部分构成,其中Read Master Logic提供了符合Aval-on接口规范的主端口信号;Control Logic是ReadMaster Logic与PCI9054 Local Bus Logic控制信号和状态信号转换的桥梁;FIFO是数据由Read MasterLogic向PCI9054传输的缓冲区。这三部分通过主端口流水线读传输时序逻辑联系在一起,提供了Avalon主外设的主端口接口界面。PCI9054 Local Bus Logic即VHDL语言设计的本地总线状态机,它将PCI9054本地端的信号通过状态机逻辑转换为与Control Logic和FIFO相对应的信号;Clock/Reset提供了主外设的clk和reset信号。

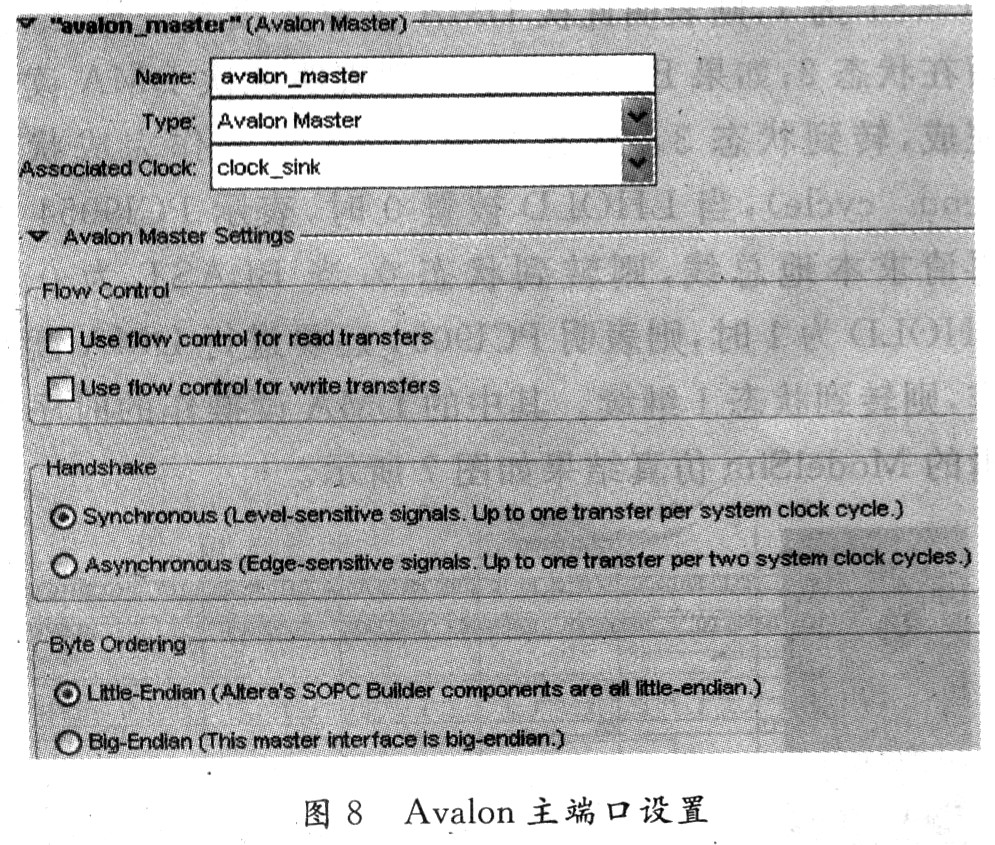

利用SOPC Builder中的new cormponent edit设计PCI9054接口逻辑模块的接口。在new component ed-it的signal中设置模块的各信号线以及相应的总线型号类型;在interface中设置各信号线对应的端口类型及其相应的参数。图8为Avalon主端口的参数设置。

2.4 系统中各中断的实现

在SOPC系统中,当没有进行传输时,Avalon交换结构忽略来自主端口所有与传输相关的输出信号,并且主端口也忽略来自Avalon交换结构所有与传输相关的输入信号。但是Avalon总线接口提供控制信号来实现中断请求等功能,这些信号不直接与数据传输相关。Avalon中断请求信号允许从端口发出一个IRQ,表明它需要主外设来服务。系统中,PCI9054采用了DMA加中断的方式来传输数据,而且DMA传输中的主控制器PCI9054芯片也要通过中断信号LINT#来触发,所以中断的实现是本系统功能实现的关键。

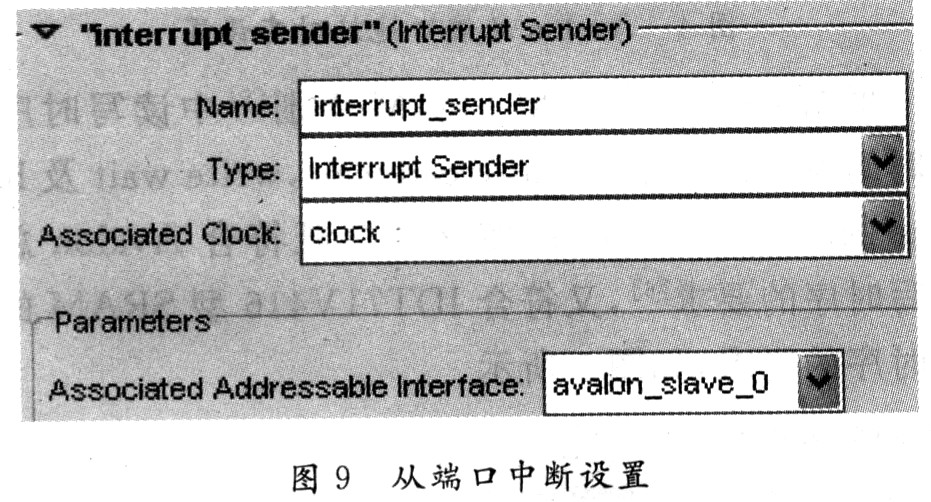

系统从端口的中断原理在于系统复位之后,数据产生模块开始自动产生伪随机序列,并自动将数据存入SRAM中,当一片SRAM存满之后,从端口的irq信号被设置。这个irq信号的时序必须与相关时钟的上升沿同步,其相关地址端口的名字必须是本模块中Aval-on从端口的名字。系统中从端口中断的具体设置如图9所示。

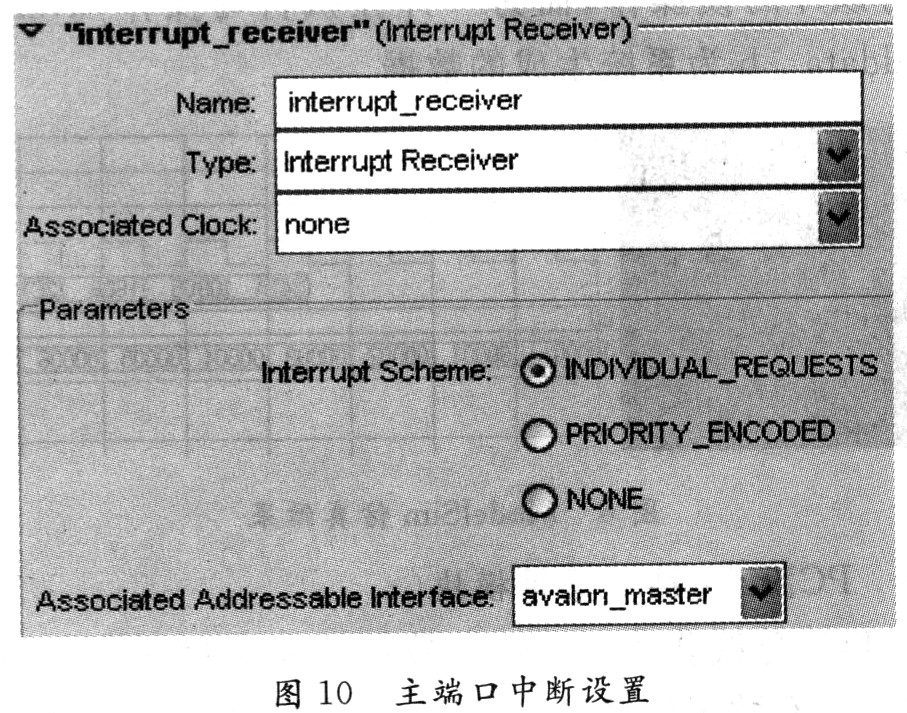

系统主端口的中断原理:在于主端口的irq检测到从端口有中断发出,通过置为有效来响应这个中断,并同时用该信号触发PCI9054的LINT#信号。PCI9054获得本地总线的控制权,并启动DMA传输,向SOPC:系统中的主外设即PCI9054接口逻辑模块发送地址和传输的字节长度,开始DMA传输。当字节长度减为O,另一片SRAM存满时,再次触发PCI9054的LINT#信号,使得PCI9054启动下一次DMA传输。主端口中断的设置如图10所示。

3 结 语

图10 主端口中断设置详细介绍了基于SOPC设计的数据发生系统中PCI接口的开发过程。对其中的关键技术,如设计添加在SOPC系统中的用户自定义主外设和从外设;PCI9054本地总线状态机的设计,乒乓结构的存储模块的设计,以及系统中各中断的实现等主要部分做了分析和研究,给出了基于SOPC的硬件实现方案。系统的主要部分由VHDL语言设计实现,有利于参数修改和系统升级。