1引言

IEEE1394是一种高速串行总线,它最初是由Apple公司与20世纪80年代中期开发的FireWire总线。1995年,IEEE制定并颁布了IEEE 1394-1995标准,并在2000年推出了IEEE 1394a标准,可以支持100Mbps、200Mbps和400Mbps的传输速率。在最新的IEEE1394B标准中,支持的传输速率提高到了800Mbps、1.6Gbps和3.2Gbps。IEEE1394总线以其高传输速率的特点已经在视频传输、网络互联及计算机外设等领域有了广泛的应用[1]。目前在航空[2]及航天应用中对大量数据的高速实时传输要求不断提高,IEEE1394具有数据传输速率高、支持等时传输等特点,因而成为未来星载数据总线的选择之一。

在星载应用中,由于任务的多样性,对星载总线接口的需求多种多样。譬如部分载荷本身没有集成1394接口却需要用1394总线来传输数据;或者几个载荷需要共用一个1394总线接口;或者是载荷自身没有带微控制器等控制单元。并且各种载荷对外的数据接口也是各不相同的。这时就需要一种体积小,简单并且易于扩充接口能的智能终端配合载荷一起工作。由于IEEE1394总线协议比较复杂,实际应用中大多数采用专用的1394总线芯片,面向专用系统的1394芯片都支持微处理器接口。常见的1394总线设计采用的是微处理器加上1394总线芯片及外围逻辑芯片,这种设计方案需要的芯片数量多,接口设备体积大,扩充接口功能实现起来比较复杂。

针对IEEE1394星载应用的实际需要,本文基于MC8051软核,提出一种简单、低功耗、小型化和易于扩展的IEEE1394智能终端设计方案,克服了以往1394总线接口硬件电路复杂、使用芯片多、体积大等缺点,并且可以很方便地扩展接口的其他功能。

2 系统实现方案

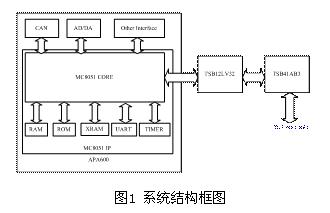

整个1934接口系统的框图如图1所示。采用的是Actel公司基于FLASH技术的ProASIC Plus系列FPGA芯片APA600。它具有单芯片上电即用、高性能和低功耗等特点[2]。由于上电即用,减小了电路板体积,有助于简化电路设计。在方案试验中使用的是TI公司的链路层芯片TSB12LV32[3]和物理层芯片TSB41AB[4]。TSB12LV32是一款高性能的通用IEEE1394a链路层芯片,用于在主控制器和1394物理层芯片以及连接到链路层DM口的外部设备之间的数据传输。它兼容IEEE1394-1995和P1394a标准,支持400、200和100Mbps的传输速率。提供可选的具有多种操作模式的8位/16位微控制器接口,最大支持60MHz。芯片内部分别内置了2K字节大小的通用接口FIFO和异步传输FIFO,用于微控制器接口和物理层接口之间的数据包传送,8位/16位数据移动端口支持25MHZ下的等时、异步和数据流包的发送和接收。TSB41AB3是一款三端口兼容IEEE 1394-1995和P1394a标准400Mbps的物理层芯片.

在FPGA中整合了开源的兼容标准8051的微控制器IP核MC8051,将程序存储器、程序存储器、外部数据存储器以及UART和定时器都集成在一片FPGA中。可以根据任务需要很方便地在FPGA内定制其他所需要的接口和逻辑单元,譬如AD/DA控制,CAN总线等。

通过上述三个部分可以构成面向特定应用的完整的1394总线接口系统。

3 基于MC8051 IP的1394总线接口设计

3.1 Oregano Systems MC8051 IP Core¬[5]

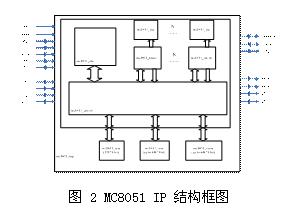

Oregano Systems公司发布的MC8051 IP Core是一个基于GUN LGPL的开源IP Core。它完全兼容标准的8051控制器,并且对其体系结构作了改进,在使用相同时钟频率情况下,将指令的执行时间下降到1到4个时钟周期,因此速度得到了十几倍的提升,并且降低了功耗。MC8051模型是可综合RTL风格,完全的同步设计,具有单一时钟网络,通过调整和修改VHDL代码可以轻松地扩展其功能。具有128字节的片内RAM,最高可以支持64K的ROM和RAM,并且集成了UART、定时器、中断和4组8位的I/O口。

3.2 MC8051设计要点

3.2.1 MC8051参数配置

MC8051提供了参数化设计,通过修改VHDL中的参数值可以很轻易的修改内部模型,例如UART个数,Timer个数,选择乘法器等。在本应用系统中不需要涉及乘除法运算,因此在配置文件mc8051_p.vhd中将常数C_IMPL_MUL, C_IMPL_DIV以及C_IMPL_DA的设置为0。

3.2.2时钟和RAM设计

MC8051 IP核在Actel的APA600上综合得到的最高时钟频率为15MHZ左右,为了使用于调试的串口波特率误差最小,用Actel Libero内的SmartGen产生11.0592MHz的时钟作为系统时钟。

MC8051所需要的内部RAM和RAM都应该调用器件的底层单元来实现。以128字节的内部RAM为例。用SmartGen产生一个128*8大小的双口RAM ram128_8.vhd,然后在mc8051_ram.vhd中例化。

3.2.3 ROM设计

MC8051完全兼容标准8051芯片,可采用KEIL uVision开发环境,建立工程文件时候Select Device选择 Oregano Systems的8051 IP Core, 然后编译写好的51程序,产生HEX文件。需要从HEX文件中得到程序数据,这里简单介绍一下HEX文件格式。HEX文件是由任意数量的十六进制记录组成的,每个记录包含5个域,他们以下面的格式排列[6]:

:llaaaatt[dd…]cc

HEX文件都是由冒号开头的,ll是数据长度域,表示记录中数据字节的个数;aaaa为地址域,标识记录中数据字节的开始地址;tt是记录类型域,51程序产生的hex文件只有两种记录类型,包括数据记录(00)和文件结束记录(01);dd是数据域,表示一个字节的数据

选用的Actel APA系列FPGA没有底层的ROM单元,因此用VHDL设计实现ROM。通过了解了HEX文件的格式,编写了从HEX文件读取数据和地址信息,然后生成mc8051_rom.vhd文件,其中程序数据以常数的形式存在数组文件中。

3.2.4 MC8051与TSB32LV32之间的接口

链路层芯片微处理器接口包括16位宽的数据总线以及7位宽的地址总线。可以通过设置链路层芯片的COLDFIRE,M8BIT_SIZ0,MCMODE_SIZE这三个端口的状态,可以得到微处理器接口的各种不同操作模式,本设计中设置成16位MCS-MCA握手模式。

在系统顶层文件中对MC8051_top进行例化,连接MC8051与1394链路层芯片TSB12LV32。

MC8051的4组I/O口都是将输入和输出分开的,所以每组都可以配置成输入和输出。我们通过MCS和MWR来控制DM 和P1、P2口的连接。

3.3 基于MC8051的1394总线控制实现

MC8051通过TSB12LV32的微控制器接口实现对链路层和物理层内部寄存器的读取和设置,其中对链路层芯片的寄存器读写直接通过微控制器接口操作,而对物理层芯片寄存器读写是通过对链路层24H的Phy Access Register读写实现。

1394芯片部分内部寄存器需要在系统上电的时候初始化或者在运行时候进行设置,一些则需要在运行时被监视以决定系统状态,而链路层内部的异步发送FIFO和通用接收FIFO也是通过读写寄存器来访问的。因此正确读写寄存器是1394接口实现中非常重要的一步。

通过正确设置控制寄存器,DM口控制器寄存器等内部寄存器便可以实现1394总线的各种传输模式的收发。

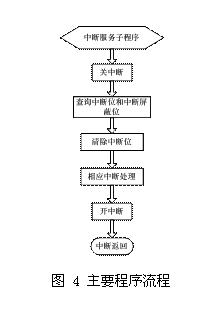

对1394芯片的控制另外一个主要部分是对中断的响应和处理。将TSB12LV32芯片的INT管脚与MC8051的int0相连,通过int0的下跳沿检测中断发生。TSB12LV32芯片中有两个寄存器是和中断相关的。设置10H的中断屏蔽寄存器中相应的某一位为1,则的0CH中断寄存器响应位便跳变为高电平,同时产生相应的中断。当有中断发生的时候,INT管脚变低电平,而清除中断则需要往中断寄存器相应位写入1。因此我们在中断发生时候,可以通过读取中断寄存器的值查看发生了哪种中断,然后做出正确的响应。

主要程序的流程图如下:

4 结论

我们根据本文介绍的方案,设计和研制了基于mc8051的1394总线接口。经过测试,1394总线系统工作正常。该总线接口具有集成度高,体积小,传输速率高等特点,同时可以根据实际任务需要很方便的扩充接口功能。本文介绍的方案对与1394总线接口的研究开发具有借鉴意义。

本文作者创新点:将MC8051软核应用与星载智能1394终端设计。