随着半导体技术以及计算机软硬件技术的飞速发展,对于图像的显示的控制技术也呈现出越来越多的方式。本文介绍了一种基于NIOS II软核处理器实现对LCD-LQ057Q3DC02控制的新方法。在设计中利用FPGA的Altera的SOPC Builder定制NIOS II软核处理器及其与显示功能相关的“软” 硬件模块来协同实现显示控制的软硬件设计。利用SOPC技术,将NIOS II CPU和LCD控制器放在同一片FPGA中,解决了通常情况下必须使用LCD 控制专用芯片才能解决LCD显示的问题。

1 LCD选型及主要特性

本文所采用的LCD是SHARP公司的5.7英寸的LCD-LQ057Q3DC02。它能显示320×240×3点像素,输入信号有:18位色度信号(R,G,B各6位)的数据信号,4个时钟信号(CLK,Hsync,Vsync,Enable)以及实现水平显示模式,垂直显示模式的R/L、U/D和VGA/QVGA模式选择信号线。

事实上,LCD-LQ057Q3DC02是一个逐行扫描设备,它总是从屏幕的左上方开始扫描,先水平扫描完一行(320像素点)到最右边,然后再回到最左边,换下一行,继续扫描。直到扫描到屏幕的最下方(共240行),这样就扫描完一帧图像,然后再回到最左边,开始下一帧的扫描。

2 Avalon流模式LCD控制器设计

文中实现的LCD 实时图像显示控制方式采用的是DMA数据传输方式。设计时,利用DMA控制器在流模式LCD控制器和SDRAM 之间建立一条DMA传送通道,让硬件来完成像素信息的自动读取,而NIOS II处理器仅通过操作SDRAM 中相应的区块就能实现LCD 图像的更新。

2.1 Avalon流模式控制器的组成

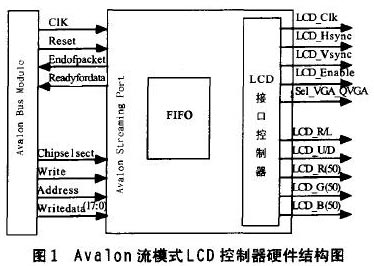

设计Avalon流模式外设时需要遵循Avalon总线规范。在实际设计时,笔者设计的Avalon流模式LCD控制器的硬件结构如图1。该控制器由如下3部分构成:LCD接口控制器、FIFO存储器和Avalon Streaming Port接口。

2.2 LCD显示控制流程

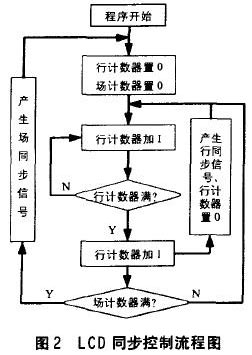

对LCD-LQ057Q3DC02而言,要实现LCD的正常显示就必须对相应的控制信号正确配置,特别是行同步(LCD_Hsync)、场同步(LCD_Vsync)必须与从SDRAM 存储器中取出的图像数据同步,否则,图像将不能正常再现。实现LCD控制的行同步、场同步的控制时序流程如图2。

2.3 LCD控制器文件组成及部分代码

与LCD控制器硬件相对应的是3个模块文件,分别是:LCD_interface.vhd,LCD_pixel_fifo.v以及LCD_controller_stream.v。其中LCD_controller_stream.v是顶层模块,其内部也包含了Avalon Streaming Port接口时序部分,LCD_pixel_fifo.v可通过QuartusII中的宏模块直接生成。当生成了上述3个文件后,可选择SOPC Builder中的System->Add Interface to User Logic命令打开Interface to User Logic对话框,选择总线类型为Avalon Memory Slave,因为工作于流模式的LCD控制器可看成一个存储器(FIFO类型),可通过添加DMA控制器来实现存储器(FIFO)到存储器(SDRAM)的DMA设置。下面给出LCD接口部分程序。

ENTITY LCD_interface IS

PORT(

reset :IN std_logic;

lcd_clk :IN std_logic;

Wrdata :IN std_logic_vector(17 downto 0);

hsync :OUT std_logic;

vsync :OUT std_logic;

enable :OUT std_logic;

lcd_R/L :OUT std_logic;

lcd_U/D :OUT std_logic;

sel_VGA_QVGA :OUT std_logic;

RGB :OUT std_logic_vector(17 downto 0);

end_of_picture :OUT std_logic);

END LCD_interface;

ARCHITECTURE trans OF LCD_interface IS

process(lcd_clk) begin

if(rising_edge(lcd_clk)) then

if(hcnt<400) then

hcnt<=hcnt+1;

else

hcnt<=(others=>0);

end if;

end if;

end process;--行计数器模块

process(lcd_clk) begin

if(rising_edge(lcd_clk)) then

if(hcnt=320) then

if(vcnt<262) then

vcnt<= vcnt+1;

else

vcnt<=(others=>0);

end if;

end if;

end if;

end process;--场计数器模块

process(lcd_clk) begin

if(rising_edge(lcd_clk)) then

if((hcnt>= 320+20+20 ) and (hcnt<320+20+20+40)) then

hs<=0;

else

hs<=1;

end if;

end if;

end process;--产生水平同步脉冲

process(vcnt)begin

if((vcnt>=240+6+6)and(vcnt<240+6+6+10)) then

VS<=0;

else

vs<=1;

end if;

end process;--产生场同步脉冲

process(lcd_clk) begin

if(rising_edge(lcd_clk)) then

if(hcnt<320 and vcnt<240)and(hcnt>20 and vcnt>6) then

en<=1;

else

en<=0;

end if;

end if;

end process;--产生显示使能控制信号

process(led_clk)begin

if(rising_edge(lcd_clk))then

if(hcnt<320 and vcnt<240)then

RGB<=Wdata;

else

RGB<=(others=>0);

end if;

end if;

end process;--像素输出及消隐

process(lcd_clk)begin

if(rising_edge(lcd_clk))then

if((vcnt=320+1)and(hcnt=0))then

end_of_picture<=1;

else

end_of_picture<=0;

end if;

end if;

end process;--一帧传输完毕

END ARCHITECTURE trans;

3 DMA控制流程及实验结论

3.1 DMA传输方式下的程序流程

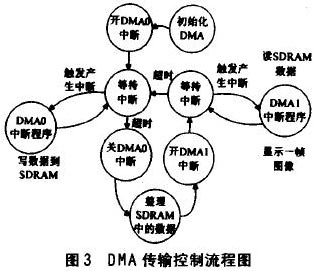

利用该方案实现LCD的显示已在某面阵CCD采集系统中得到验证。在实际的系统中,该部分主要实现所采集的面阵CCD图像传感器图像数据的动态显示。在实际的采集控制系统中选用了2个DMA,一个用于图像数据的采集,一个用于采集后图像的再现。在文中仅介绍了显示DMA传输控制方式下的相应模块。实际系统中,图像数据从面阵CCD图像传感器以DMA控制方式将图像数据采集到SDRAM,所采集后的图像数据从SDRAM到LCD显示。实际系统中的DMA控制流程如图3。

3.2实验结论

根据图3所采集到的面阵CCD的图像数据保存在SDRAM中,按一定比例抽取的图像数据在SDRAM中合成18位的RGB图像信号,而后在NIOS II处理器以及显示DMA的控制下,将一帧完整的图像显示在LCD上,实际控制的显示结果如图4。

4 结束语

利用NIOS II作为FPGA嵌入式处理器控制LCD的解决方案,能较容易地实现图像数据的DMA传输与控制,系统中可根据实际需求有选择的定制相应模块,使系统具有较强的灵活性。同时由于采用“软”硬件实现LCD的控制,调试过程中通过不断更改“软件”就可达到改进硬件功能的目的。