文献标识码: A

文章编号: 0258-7998(2015)04-0043-03

0 引言

近年来,快速发展的CMOS图像传感器因具有高集成、功耗低、工艺简单和开发周期短等优点,已被广泛应用在工业、监控、航空和航天等众多领域[1-2]。目前我国航天领域中摄像设备的分辨率普遍不高,画面质量有待提高,严重制约着我国空间可视监控技术的进一步发展[3],因此研究以CMOS图像传感器作为光电转换器件的数字高清遥感成像技术,在航天领域具有较高的实际应用价值。

1 硬件平台及基本工作原理

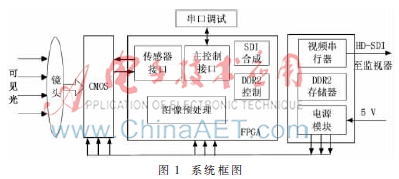

本文主要采用了CMOS图像传感器、可编程逻辑门阵列FPGA、第二代双倍速率同步动态随机存储器(Double Date Rate Synchronous Dynamic Random Access,DDR2)、视频串行器等,搭建了一个可实现图像实时采集、预处理及传输功能的高清成像系统,如图1所示。本文采用的传感器是APTINA公司的MT9M034,它集成了模拟图像采样和模数转换及在片自动曝光等功能,并支持720p60的高清视频,具有重量轻、体积小、功耗低、动态范围宽等优点,适合航天的应用场景。

FPGA作为系统主处理器,主要完成对传感器的初始化和接口控制,并对传感器输出的图像数据进行采集和预处理,以提高图像质量并供显示,这些处理主要包括时序调整、图像类型转换、图像预处理、数据存储、高清数字分量串行接口(High Definition Serial Digital Interface,HD-SDI)视频合成等。本文FPGA选用的是Xilinx公司的 XC6SLX75t,它内部具有丰富的逻辑、存储资源及用户接口。

为了将图像传输至监视器上呈现出来,本系统选用了National Semiconductor公司的芯片LHM0340作为数字视频串行器,它对接收到的亮度和色差信号的并行数据进行并串转换,输出HD-SDI数据流并送往监视器。

2 FPGA设计

根据模块化的设计思路,将FPGA的功能分为主控制接口、传感器接口、图像预处理等6个子模块来实现,如图2所示。

2.1 时钟管理模块

时钟管理模块接收外部晶振输入的74.25 MHz时钟,再利用FPGA的时钟管理资源和全局时钟资源产生74.25 MHz和148.5 MHz的全局时钟。其中,除DDR2控制模块和数字视频合成模块使用了两个全局时钟外,其他模块均使用74.25 MHz全局时钟。

2.2 主控制接口模块

如图2所示,该模块连接其他各模块并控制它们的运作,产生其他各模块的复位信号并通过对寄存器读写的方式产生系统控制信号;另外,主控接口模块还支持通过异步串口连接上位机进行通信和控制。

2.3 传感器接口模块

传感器接口模块的主要功能是对CMOS传感器进行复位及内部寄存器的配置、采集传感器输出的Bayer模式图像数据并输出符合格式要求的图像数据。该模块与传感器通过I2C接口进行通信,由于传感器的分辨率是1 280×960,为符合数字高清的标准,需对其稍作调整,转换为1 280×720的分辨率。

2.4 图像预处理模块

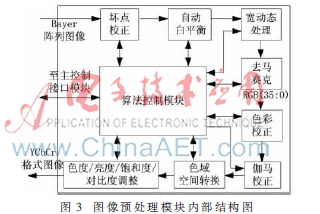

由于航天应用场景中存在多种光照环境,且遥感画面动态范围较大,为了使获得的图像在各种光照环境下都能呈现最佳的效果,图像预处理模块采用了多种算法对传感器输出的图像信号进行处理,这些处理包括坏点校正、去马赛克、自动白平衡、色彩校正、伽马校正、色度空间转换、宽动态处理以及色度/亮度/饱和度/对比度调整。在FPGA设计时,将该模块分割为8个算法子模块和一个控制子模块,如图3所示。

各模块的输入参数均通过主控模块配置。其中,宽动态处理、色彩校正和色度空间转换均采用了Xilinx公司的IP核予以实现,色度/亮度/饱和度/对比度调整则采用Lattice公司的IP核,对其他几个模块介绍如下。

2.4.1 坏点校正模块

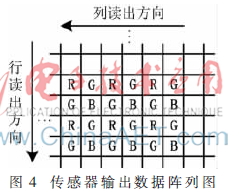

本模块接收到的Bayer阵列型图像数据,其特点如图4所示,对任一像素而言,若其为坏点,则可利用同一行中其左右相邻同分量的两个像素值来纠正。

为得到3个相邻的同类型分量像素,需得到5个连续的像素。因此将模块的输入图像数据作4级延迟,与当前输入的数据一起组成5个像素。对于这5个像素的中心像素,计算出其左右相邻两个同分量像素的平均值,再分别乘上1.25、1.5和2的系数构成3种阈值以供不同场景使用。

根据主控制接口模块的指示,从3种阈值中选择一种作为当前阈值,对中心像素进行判断,若超出该阈值则判为坏点,用已计算出的其相邻同分量的平均值代替该像素的值,否则保持不变。利用FPGA来设计这一算法,可实现流水线式的坏点检测与校正功能。

2.4.2 自动白平衡

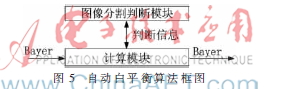

自动白平衡算法有很多,其中应用极为广泛的是基于灰度世界理论:对于任一幅图像,当它有足够的色彩变化时,则它的RGB分量的均值会趋于相等。

相对于其他算法而言,该算法简单可靠且便于硬件实现,本文采用的即是这种基于灰度世界假设的算法[4],如图5所示。

图像分割判断模块首先把图像分块,对每一块计算其像素的标准差(即颜色变化的情况),判断是否是大色块,是否是过亮块、过暗块。对于标准差越大的图像块,说明其颜色越丰富,越符合灰度世界理论的假设,权重越大;而标准差越小的块则权重越小。

计算模块根据图像分割模块提供的信息,进行全局的块选取,并按照灰度世界的假设进行计算,得到矫正过的图像数据。

2.4.3 去马赛克

去马赛克算法的目的是将Bayer格式的图像信号通过插值处理去马赛克,转化成完整的RGB信号。本模块选用的是改进的线性插值法[5]。

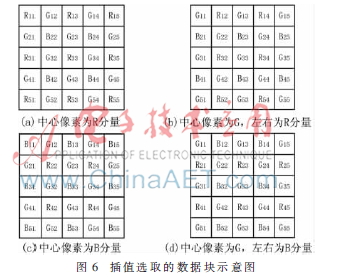

本模块设有4个行缓存,用于接收输入的图像数据。将当前输入的图像数据以及从4个行缓存中读出的数据分别进行5级延迟,则可得到5×5的Bayer数据块。按照数据块中心像素为R/G/B何种分量以及与其领域各像素相对关系的不同,可总结出4种情况,分别如图6所示,中心像素点的坐标为(3,3)。对待插值像素(中心像素)的5×5邻域内数据块在不同情况下通过不同的公式进行插值运算即可得出中心像素点R、G、B三分量的值。

2.4.4 伽马校正

大多数的显示设备的输入电压与显示的彩色图像强度成非线性的关系,为了使显示图像和真实图像相符,得到更加自然、真实、悦目的画面,有必要对因为显示器特性造成的非线性误差进行伽马校正。

本模块通过预先设定伽马校正数据表,通过上位机经过异步串口写入FPGA,存入只读存储器中,再进行查表获取伽马校正后的数据。

2.5 DDR2控制模块

DDR2控制模块通过管理DDR2存储芯片将图像预处理模块输出的YCbCr格式数据进行缓存并输出。其功能通过3个子模块来实现,如图7所示。子模块1将接收到的16 bit并行数据进行缓存;子模块2为Xilinx公司的DDR2控制器IP核,它将子模块1中的缓存数据以32位写入DDR2,同样以32位读出发送至子模块3再次进行缓存,最终恢复成16 bit并行数据输出。

2.6 数字视频合成模块

数字视频合成模块按照HD-SDI格式将数据合成为并行数据,并送入串行器进行并串转换。该模块的功能通过3个子模块来实现,分别是打包子模块、编码子模块、串行器接口子模块。

打包子模块接收DDR2控制模块输出的图像数据,通过对Y分量和C分量分别低位填零扩展至20 bit并行,再根据2.2节所述主控制接口模块的指示,在图像数据中插入HD-SDI格式所需的时间基准信号及消隐,打包输出至编码子模块。

编码子模块为Xilinx公司的IP核,它通过检测输入的视频数据流,提取时间基准并进行CRC校验,再进行HD-SDI编码,以20 bit并行输出至串行器接口子模块。

串行器接口子模块将输入的20 bit并行数据用148.5 MHz时钟进行高速采样,再利用FPGA的ODDR2资源双沿发送将数据提速,拆分成5 bit并行数据,最后用OBUFDS资源将其转换为差分信号发送至串行器。

3 系统验证

本文通过ISE14.1开发环境进行了FPGA代码设计和仿真验证。图8是HD-SDI合成模块的仿真结果,图9是本文成像系统在监视器上的显示结果对比,其中(a)是未启动白平衡算法和伽马校正的原始图像,(b)是经过白平衡算法和伽马校正等预处理后的图像,从两者对比可以看出,未经过预处理的图像颜色失真,而经本文预处理后的图像画面逼真,质量更高。

4 结论

本文设计了一种基于FPGA的数字高清CMOS遥感成像系统,以FPGA为主处理器,经过对传感器控制、图像采集与图像预处理,得到了高质量的遥感图像。通过软件仿真和硬件测试,验证了该设计方案的正确性和有效性。

参考文献

[1] 范铁道.基于FPGA的数字高清CCD摄像机技术研究[D].西安:中国科学院研究生院(西安光学精密机械研究所),2009.

[2] 赵鹏,沈庭芝,单宝堂.基于CMOS图像传感器的微型无人机遥感系统设计[J].光子学报,2008,37(8):1657-1661.

[3] 刘海英.基于CMOS图像传感器的数字高清成像技术研究[D].西安:中国科学院研究生院(西安光学精密机械研究所),2008.

[4] 谷元保,付守卓.一种基于灰度世界模型自动白平衡方法[J].计算机仿真,2005,22(9):185-188.

[5] MALVAR H S,He Liwei,CUTLER R.High-quality linear interpolation for demosaicing of Bayer-patterned color im-ages[C].IEEE International Conference on Acoustics,Speechand Signal Processing.Montreal:IEEE,Piscataway,NJ,2004.