文献标识码: A

文章编号: 0258-7998(2015)04-0116-03

中文引用格式:彭海,高俊雄,王耘波.一种应用于生物识别领域的AES算法[J].电子技术应用,2015,41(04):116-118

0 引言

生物识别技术方便、快捷、安全可靠,已被广泛应用于部队、政府机关、高档小区等对安全系数要求较高的场合,并且呈快速发展的趋势。然而随着生物识别技术的大量应用,人们对生物识别技术的安全性和隐私问题的关注也越来越多[1]。生物识别技术一般对生物特征(如指纹、虹膜等)进行取样,提取其唯一特征并且转化为特征模板,根据特征模板进行匹配。特征模板就像生物识别技术里的“钥匙”,一旦被修改将直接影响其识别结果。因此,采集模板时利用AES加密算法对模板数据进行加密,进行识别时取出加密后的模板并将其解密。这种以AES算法实现对模板数据的加密可大大提高生物识别的安全性。生物识别系统在识别时往往要遍历所有模板,而由于用户基数庞大,数据库中一般存在大量的特征模板,因此系统对解密的速度要求非常高。

AES加密算法由美国国家标准与技术研究所(NIST)在2002年建立,它可以使用128 bit、192 bit或256 bit密钥,并用128 bit(16 B)分组加密和解密数据。现阶段AES加密主要通过软件编程或硬件逻辑实现。采用软件编程实现的方法具有成本低、灵活的特点,但软件实现的AES易被修改,且速度较慢;采用硬件逻辑实现的AES加密算法除了高效和安全外,还保证了很高的速度,所以在生物识别领域十分适用。本文主要论述了在FPGA硬件平台下实现的一种大吞吐量256 bit密钥的AES算法,因AES加密与解密的过程基本相同,故主要论述了AES算法的解密过程在FPGA上的实现。

1 AES算法简介

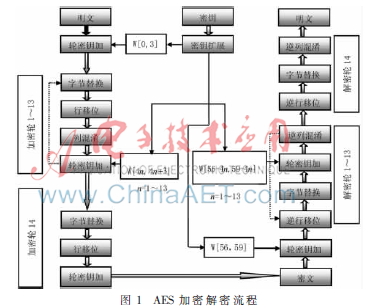

AES算法是基于置换和代替的。置换是指数据的重新排列,而代替是用一个单元数据替换另一个。图1显示了AES(256 bit)加密解密的完整流程。

AES加密算法把输入的128 bit数据看成是一个名为State状态矩阵的4×4的字节矩阵。加密过程就是对State状态矩阵进行多轮操作[2]。算法开始前首先构造用于加密的两个表,一个是用于字节替换的S-box表,另一个是用于产生轮密钥的密钥调度表。算法首先进行AddRoundKey(轮密钥加),即用密钥调度表中的前4行对State矩阵进行异或操作。然后是AES加密算法的主循环,循环的次数由输入密钥的长度决定,如密钥位数为256 bit,则循环总轮数为14轮。AES算法的加密主循环每轮对State状态矩阵执行4个不同的操作,分别是SubBytes(字节替换)、ShiftRows(行移位变换)、MixColums(列混淆变换)和AddRoundKey(轮密钥加),其中最后一轮不进行ShiftRows(行移位变换)。字节替换是指通过S盒对状态矩阵进行替换,行移位变换是指状态矩阵的每一行进行循环移位,列混淆变换主要用到了GF28域上的乘法和加法运算,而轮密钥加是简单的异或运算。AES解密主循环是加密循环的逆过程,解密主循环中也有对应的逆变换:Inv_SubBytes(逆字节替换)、Inv_ShiftRows(逆行移位变换)、Inv_MixColumns(逆列混淆变换),这些变换均可看成加密主循环中4个变换的逆变换。

2 AES算法的FPGA实现

2.1 FPGA技术简介

现场可编程门阵列FPGA(Field Programmable Gate Array)是美国Xilinx公司于1984年首次开发的一种通用型用户可编程器件。FPGA既具有门阵列器件的高集成度和通用性,又有可编程逻辑器件的灵活性。

FPGA结构灵活,其逻辑单元、可编程内部连线和I/O单元都可由用户编程,可实现任何逻辑功能,满足各种设计需求。其速度快、功耗低、通用性强的特点适用于复杂系统的设计[3]。FPGA技术还可以实现动态配置、在线系统重构(可以在系统运行的不同时刻,按需要改变电路的功能,使系统具备多种空间相关或时间相关的任务)及硬件软化、软件硬化等功能。

2.2 使用FPGA实现AES算法

2.2.1 系统的总体结构

根据AES算法轮操作的特点,本文采取基本迭代与串行缓存相结合的方法,系统总体实现框图如图2所示。通过14个AES解密模块并行使用,大大提高了吞吐率,其中每个AES解密模块采用基本迭代的方法,即所有轮次复用一个轮函数,每个时钟周期完成一次轮操作,14个时钟周期完成一个分组运算。

解密数据时,首先让密文数据依次进入串行缓存,串行缓存的深度与AES算法的轮数相同(为14),进入串行缓存的数据依次进入AES解密模块进行解密。第一个时钟周期,让密文数据进入Data_buffer1,然后启动第一个AES解密模块AES1;第二个时钟周期,让新的密文数据进入Data_buffer2,然后启动第二个AES解密模块AES2;依此类推,往复循环。14个AES解密模块的启动顺序如图3所示。

每经过14个时钟周期,将每个AES解密模块的结果依次移位输出。采用这种结构实现的AES解密算法虽然消耗了不少FPGA的内部资源,但数据无需等待,可以源源不断地进入解密模块,整个解密过程的速度仅仅取决于单个AES解密模块的工作频率与数据输入的速率,使得系统的吞吐率大大提高。考虑到FPGA内部资源丰富,可以牺牲部分资源来换取速度。

2.2.2 AES解密模块的实现

AES解密前,首先要进行密钥扩展。密钥扩展是将初始密钥作为种子密钥,经过字节代换、字节移位、轮常数计算、字节异或等过程,计算产生14轮迭代所需的轮密钥。密钥扩展实现框图如图4。有文献提出计算密钥时密钥扩展和加密过程同步执行,这样做会节约FPGA的存储器资源。但考虑到密钥不需要经常更换,而且FPGA存储器资源丰富,有足够的空间存放子密钥,所以本文决定在解密前先进行密钥扩展,然后将产生子密钥存放在RAM中,根据使用需要从RAM中读取密钥。这种方法易于实现,且灵活性强,产生好的密钥调度表在种子密钥不变的情况下都可以供其他模块使用。

密钥扩展完成后,就可以开始进行解密。256 bit的AES解密过程总共需要14轮,除最后一轮外每轮需要进行字节替换、逆行移位、轮密钥加、逆列混淆等4个操作,最后一轮不需要进行轮密钥加。其实现框图如图5所示。

逆行移位(Inv_ShiftRow)采用简单的组合逻辑即可实现;逆字节替换(Inv_SubBytes)利用FPGA内部的分布式RAM实现,将逆S_BOX的值预先存入到RAM中,在进行逆字节替换时,以字节的高4位和低4位作为地址即可读出要替换的值,这样既避免了复杂的组合逻辑,又提高了系统的运行频率;轮密钥加(AddKey)为简单的异或运算;逆列混淆(Inv_MixCol)的实现采用了将复杂的GF28域乘法逐次分解为基础的GF28域乘法的方法,使整个过程易于在FPGA中实现。

3 实验结果

本设计在Xilinx公司的XC7A200T-2芯片上进行验证,图6给出了系统的在Isim仿真环境下的仿真图。

输入密文为16进制数8960494b9049fceabf456751cab-7a28e,密钥为16进制数1f1e1d1c1b1a1918171615141312-

11100f0e0d0c0b0a09080706050403020100,14个周期后输出解密后的明文为16进制数ffeeddccbbaa998877665544-33221100。经验证,该解密过程完全正确。

在ISE13.6环境下代码在综合后频率可达到236.9 MHz,由于采用串行缓存的方法,数据可以持续加密,无需等待上一个数据加密完。经计算理论吞吐量可以达到30.3 Gb/s,完全适用于各个应用场合的需要。

4 结论

采用FPGA实现AES算法可以大幅度提高加密解密速度,并且具有开发周期短、易于实现的特点;采用本方法实现的AES算法虽然占用了较多的FPGA资源,但加密解密速度得到大大的提高,吞吐量可达到30.3 Gb/s,完全满足现行生物识别技术的要求,能广泛应用于虹膜识别技术及指纹识别技术等领域,应用前景广阔。

参考文献

[1] 赵洋.生物识别系统中的模板安全分析[J].中国安防,2012,3(3):99-104.

[2] DANMEN J,RIIJMEN V.AES proposal:rijndael.AES algo-rithm submission.[EB/OL](1999-09-03)[2014-12-23].http://www.nist.gov/aes.

[3] Clive Max Maxfield.FPGA设计指南:器件、工具和流程[M].北京:人民邮电出版社,2007.