摘 要: 多用户接入单元(Multiple Dwelling Unit,MDU)是FTTB中的核心设备。随着人们对宽带速率增长的需求,传统的DSL网络已经无法满足人们对带宽的需求,光纤接入FTTH(光纤到户)、FTTB(光纤到楼)带宽大、扩展性好,可以满足用户现在及未来对带宽的需求。然而FTTH(光纤到户)业务的部署成本太高,无法利用电信网络目前存在的铜线资源。FTTB(光纤到楼)+Lan或FTTB+DSL不仅可以满足用户的带宽需求,同时又可以利用现有铜线资源,降低部署成本。本文研究的MDU就是FTTB的核心设备。本文主要研究了MDU设备主控系统的硬件实现。

0 引言

MDU 在网络中的位置如图1所示,它是最靠近用户端的设备,对用户可以提供VDSL 、ADSL 、FE 和语音POTS接入。可以上连GPON、EPON、10GEPON、 XGGPON或者GE(Optical and Electric)。

1 MDU主控系统架构

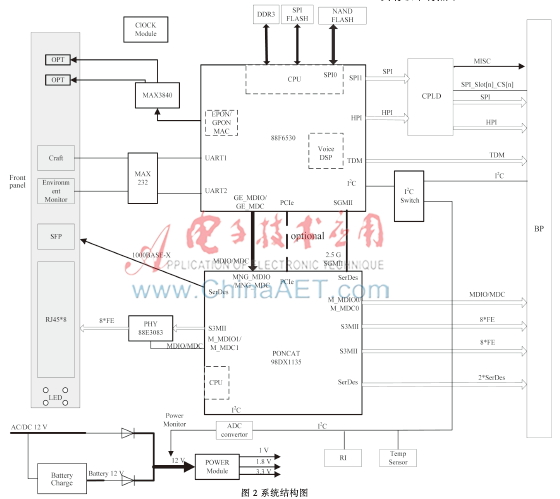

根据要求和应用场景不同,MDU 有1U 和2U两种。2U 通常是有主控板、一个上连卡、背板和4个槽位的LT 板。1U有一个主控板、一个上连卡和一个LT板,通过背板将这几个部分连接在一起。本系统是基于1U 的设计,将上连和主控部分集成在一块板卡上,通过一个芯片88F6530来实现。主控板的系统实现框图如图2所示。

在此设计中88F6530做为主控芯片,上行可以是GPON也可以是EPON ,通过88F6530一个芯片实现,不需要硬件设计的改变,只需改变软件即可实现,节省了开发周期。用户接口有24FE和32POTS两种。88F6530内部集成了一个语音处理DSP核,外部不需要语音处理芯片DSP,节省了成本。POTS用户板的TDM 信号直接与88F6530的TDM 接口连接。POTS用户板的管理接口由88F6530的HPI 接口通过CPLD 来控制。24FE 接口由Marvell 的Poncat 芯片98DX1135来实现。98DX1135有3组S3MII接口,通过外接PHY可以实现 24FE ,其中8个FE 由主板实现,另外16FE 由LT 来实现。

从图2可以看出主控系统可以分为4部分:

⑴主控芯片88F6530 及其外围包括DDR、Flash和RI 温度传感器;

⑵上行接口EPON 或者GPON;

⑶用户接口POTS、FE 接口及其控制接口;

⑷电源部分。

下面分别对这几个部分详细论述其具体实现。

2 主控芯片88F6530及其外围

2.1 主控芯片88F6530

88F6530是Marvell AVAVTA 系列产品中的一款,主要应用在MDU产品中。88F6530 MDU ONU设备提供Universal PON(UPON) MAC ,兼容EPON 和GPON,基于IPV6和IPV4包处理器线速可达到2.5 Gb/s,还有32通道的语音引擎。由于其具有高集成度、低功耗、高性能的特点,88F6530为运营商提供了一种低成本部署光纤宽带的选择,可以为用户提供视频、界面和云等体验。88F6530具有以下特点:

⑴ 完全兼容EPON、GPON和P2P以太网MAC;

⑵2.5 G 的Switch接口;

⑶VoIP和控制处理器:1.6 GHz的CPU,有16 KB的一级Caches和256 KB的二级Caches;

⑷32通道的VoIP DSP 支持G.729和G.723;

⑸TDM接口支持标准的SLIC/SLAC设备;

⑹支持 DDR2/DDR3设备,DDR2支持400 MHz,DDR3支持533 MHz,集成了4个DRAM片选;

⑺支持NAND、NOR 和SPI Flash;

⑻两个PCIe接口;

⑼I2C 接口;

⑽中断处理器;

⑾两个UART接口。

88F6530内部结构如图3所示。

通过以上特性的介绍和88F6530内部结构可以看出,88F6530可以作为此系统的主控芯片完成大部分功能,同时可以节省开发成本。

2.2 88F6530外围电路

2.2.1 DDR和Flash

88F6530支持16 bit的DDR2接口和DDR3接口, 本系统采用了1 G的16 bit DDR2 (HY5PS1G163)。DDR2最大频率可达到400 MHz。同时使用了512 MB的NAND Flash(NAND04GW3B2DN6E)和128 MB的SPI Flash(M25P128)。SPI Flash是启动时Boot所用的,NAND Flash为存取数据所用。

2.2.2 系统时钟

本系统采用25 MHz的外部时钟作为系统时钟,为内部PLL 提供参考时钟。

2.2.3 I2C设备 RI和温感

88F6530只有一组I2C接口,无法满足本系统的要求。在本系统中有RI和温度传感器,还有检测LT子卡的I2C接口,因此至少需要3个I2C接口。I2C Switch 芯片PCA9544A 有4组I2C接口,可以满足本设计的需求,一组为RI,一组为温感,另外一组通往背板供LT使用。8k×8bit的E2PROM作为RI 设备。TI的TMP432作为检测温度。此温感芯片是一个可远端监测温度和本地监测温度的传感器。远端温度检测可以通过外接一个NPN或者PNP三极管来实现。在此系统中将一路远端用于检测电源部分的温度,另外一个远端用于检测PONCAT 98DX1135,TMP432芯片本身来检测主控芯片88F6530的温度。根据系统预设的初始值,在外界温度超过此值时芯片会告警。

3 上行接口EPON GPON

88F6530 内部集成了EPON 、GPON MAC,外围只需接相应的芯片就可以实现GPON或EPON上连。此系统中外部使用了MAX3840,它是一款双路2×2异步矩阵开关,宽带频、全差分信号通路使累积抖动、串扰即信号偏斜最小。每路2×2矩阵开关能够扇出或复用高达2.7 Gb/s的数据和2.7 GHz时钟信号。

4 用户接口 FE 和POTS接口

4.1 FE接口

在此系统中FE接口是使用Marvell的PonCat 98DX1135来实现的。

4.1.1 PonCat 98DX1135

PonCat 98DX1135 是FE Switch PonCat2系列产品中新一代高集成、经济有效的一款芯片。此芯片是Marvell Prestera- DX系列中一款高性能、低功耗的处理器,是一款比较理想的芯片。PonCat系列产品增强了封装散热,超成本优化设计支持最小PCB 布线要求,可以无风扇设计。此款芯片的上行SerDes端口可以支持10/100/1000/2500 的SGMII和1000Base-x,与Marvell外接GPON MAC具有相同的功能。Poncat内部也有CPU,因为此系统以88F6530做为主控芯片,因此这里不使能Poncat内部的CPU。

4.1.2 24FE 的实现

98DX1135 内部有FE MAC,外部只需FE PHY 就可以实现用户的FE接口要求。在本系统中8个FE是由主控板来实现,其余16个FE由LT来实现。主控板将两组S3MII信号连接到背板。在主控板上使用Marvell的PHY 88E3083与98DX1135的S3MII接口相连。88E3083是Marvell为快速以太网设计的第三代基于DSP 的八端口物理层设备。此芯片可以完成MACs和物理媒体的数据转换。88E3083支持1EEE802.3,支持使用双绞线的100BASE-TX 和10BASE-T网络全双工或者半双工的自动协商机制,具有S3MII接口,可以很好地与98DX1135直连,不需要其他转换芯片。对88E3083的控制通过MDIO接口来实现。

4.2 POTS接口

因为88F6530内部集成了32通道的语音处理器,所以在本系统中不需要外接DSP芯片来完成语音信号处理。88F6530 的TDM信号可以直接和SLAC连接。此接口可以作为Master模式提供帧同步信号和时钟信号, 或者也可以作为Slave模式,接收帧同步信号和时钟信号;线性编码支持u率和A率;时钟范围256 kHz ~ 8.192 MHz;此部分提供一个SPI接口,本系统是32POTS,因此有4个SLAC,需要4个CS,为了实现对SLAC的控制和配置,将SPI接口通过CPLD来实现对4个SLAC的控制。在主控系统中,只需提供DX、DR、FS、CLK 和四组SPI信号到背板就可以实现与POTS子板的连接和通信。

5 电源设计

PONCAT 98DX1135需要核电压1.0 V,SDRAM 1.8 V,其余 3.3 V。而88F6530需要核电压1.0 V,CPU 1.1 V、1.5 V、2.5 V还有 3.3 V,因此整个系统需要电压种类多,共需要5种电源,其中3.3 V、1.0 V、1.5 V所需要的电流比较大,用DC-DC来实现转换。此板输入电压为12 V,12 V进入之后先进行滤波,然后经过热拔插保护芯片LTC4210,由LTC4210输出的12 V电压再进行转换,转换为板上所需的3.3 V、2.5 V、1.8 V、1.5 V、1.1 V、1.0 V。LTC4210还可以监测 输入电压12 V,若12 V的抖动超过了系统所允许的范围,则会自动关断12 V。此系统所用的3.3 V 芯片为TI的TPS54550。TPS54550是TI公司的一款DC-DC,输入电压4.5 V~20 V,输出电流可以达到6 A,具有可调节的开关频率。 1.0 V、1.5 V由ADP1829来实现。ADP1829是AD公司的一款双路DC-DC芯片。此芯片开关频率可以工作在300 kHz、600 kHz,有软启动功能、热过载保护及电流过载保护等功能。其余电压用LDO 来实现。系统中所需的电压种类比较多,而且各个电压之间上电和下电之间的时序有一定的要求,只有满足了这些要求,系统才可以正常工作。这些通常可以通过调整电源芯片EN管脚上的电阻、电容来实现。

6 结束语

本文从各个部分详细地论述了MDU主控板的硬件设计,此设计最大的优点就是主控芯片集成了EPON和GPON MACs,节省了开发的硬件和软件成本,同时又满足了用户的需求。

参考文献

[1] Marvell. 88F6530 hardware specifications[Z]. 2010.

[2] Marvell. Prestera PonCat2-FE hardware specificaions[Z]. 2010.

[3] Marvell. 88E3083 integrated 8 Port 10/100 fast ethernet transceiver[Z]. 2002.

[4] Maxim Integraled Products. Max3840 Dual 2X2 Crosspoint Switch(Rev 5)[Z]. 2007.

[5] Texas Instruments Incorporaterd. Tps54550 datasheet[Z]. 2006.