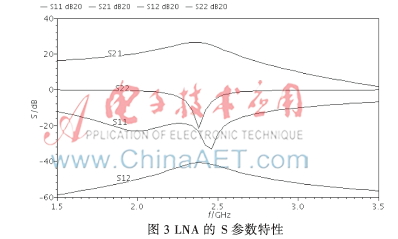

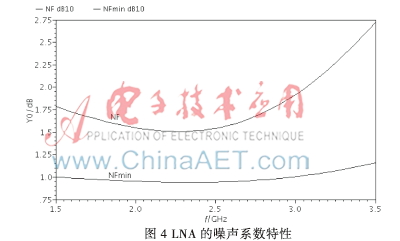

摘 要: 针对低功耗电路设计要求,基于SMIC 0.18 μm CMOS 工艺,设计了一种电流复用两级共源低噪声放大器。仿真结果表明,在2.4 GHz的工作频率下,功率增益为26.26 dB,输入回波损耗S11为-27.14 dB,输出回波损耗S22为-16.54 dB,反向隔离度为-40.91 dB,噪声系数为1.52 dB,在1.5 V的供电电压下,电路的静态功耗为8.6 mW,并且工作稳定。

关键词: CMOS;电流复用;阻抗匹配;低噪声放大器

0 引言

由于具有集成度高、成本低等优势,当前大多数无线射频收发系统的设计都采用CMOS技术[1]。由于低噪声放大器(LNA)处于接收机前端,它对整个无线通信系统射频接收机的性能起着关键性的作用。为了抑制后面各级噪声对系统的影响,LNA要求有较好的噪声性能以及足够的增益。为了保证在较大的信号动态范围内LNA能够正常工作,要求LNA有足够的线性度,同时为了实现最大功率传输或最小噪声系数,应保证LNA的输入阻抗与前端源阻抗实现良好的匹配。在实际设计中,这些性能指标会相互牵制相互影响,所以在设计过程中要对这些性能指标进行折衷处理[2]。

本文基于SMIC 0.18 μm CMOS工艺设计实现了中心频率为2.4 GHz低噪声放大器。文章第1部分分析了电流复用两级共源LNA的电路结构、输入阻抗以及最佳MOS管尺寸的选择;第2部分是电路仿真结果并就此结果进行了详细的分析;最后对全文进行总结。

1 LNA电路设计与优化

1.1 电路结构分析

为了满足整个系统的性能要求,LNA需要足够的增益,所以在LNA的设计中通常采用多级放大器。在多级放大器中,由于每级电路都要消耗电流,导致电路电流随着电路级数增加而增加。为了降低功耗,本文采用CS-CS cascaded电流复用结构,电路如图1所示。LNA的直流偏置电路由M0和R1构成,电源电压、电阻R1与M0的栅极和源极电压决定了M0的工作电流,晶体管M0与M1形成电流镜。为了尽可能地减小偏置电路的附加功耗,M0的栅宽远小于M1栅宽。为了尽可能地减小偏置电路对交流信号通路的影响,电阻R2选择得足够大。电感L1、L2和电容Cex实现输入匹配,电感L4、C4、L5和电容C5实现输出匹配。在直流时,电感L3起到短路的作用,此时第二级和第一级共享偏置电流,这样可以大大降低电路的功耗。在交流时,电容C2交流接地,电感L3起到Rfchock作用,第一级的输出通过耦合电容C3连接到第二级晶体管M2的栅极,构成两级共源结构,从而提高了整个电路的功率增益。

1.2 最佳MOS管宽度选择

多级低噪声放大器的噪声系数的表达式为 [3]:

公式(1)中,NFk为第k级的噪声系数;GA(k-1)为第k-1级的增益。由式(1)可知,NF1和GA1是NFtot取值大小的关键,如果GA1足够大,第2级及后面的放大器的噪声对整体噪声的影响可以忽略,因此电路噪声主要决定于NF1。

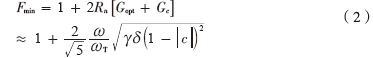

由经典的噪声理论可推导出MOS管的最小噪声系数的表达式为[4]:

其中,ω为LNA的工作频率,ωT为MOS管的截止频率,γ为漏噪声系数,δ为栅噪声系数,c为漏噪声与栅噪声的相关系数。gd0为漏源电压为0时的漏源跨导,

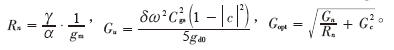

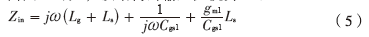

公式(2)的最小噪声系数是在不考虑功耗的情况下得出的,考虑到功耗的限制可以得出使噪声系数最小的最优MOS管的宽度表达式为:

若MOS管的宽度取值为Wopt,则可以计算在功耗约束的范围内取得的噪声系数为:

1.3 输入匹配电路的优化设计

传统的放大器输入匹配通常采用源级电感负反馈结构[5-6],如图2所示。

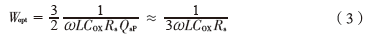

由图2可知,该结构的输入阻抗为[2]:

在一定的偏置和器件尺寸条件下,选取适当的Ls使得输入阻抗为50 ,即可实现输入端的阻抗匹配。但是这种结构需要感值很高的栅极电感,高感值的电感在芯片中会占用很大的面积,而且在射频电路设计中,高感值的电感寄生电阻较大,对应的噪声也较大。

本电路的设计中在晶体管M1的栅源之间并上一个电容Cex,用来调节晶体管M1栅源之间电容的大小,进而减小栅极电感的值。此时LNA的输入阻抗为:

其中

输入电路谐振时,

在LNA处于一定的偏置和器件尺寸的条件下,通过调整电感Ls的大小使得输入阻抗中的实部等于50 ?,即可实现输入端的阻抗匹配,而且此时产生的实部不是一个实际的电阻,因此不用担心由实际电阻而产生的热噪声,所以不会对放大器的噪声性能产生影响。通过调整Lg和Ct的大小使输入阻抗的虚部的感抗和容抗相互抵消,使得输入阻抗的虚部为零。从式(7)可以看出,在晶体管M1的栅极和源极之间并联一个电容Cex后,所需要的栅极电感的值减小。

1.4 电路稳定性分析

电路的稳定性也是LNA设计中需要考虑的一个重要的性能指标。在放大器的设计中,必须保证放大器的稳定性,否则放大器在一定条件的激励下有可能会出现自激现象。通常用稳定因子K描述一个二端口网络的绝对稳定条件[7]:

其中: ![Y0G3~`S9{1K]DOJ]Y$P(JR6.png Y0G3~`S9{1K]DOJ]Y$P(JR6.png](http://files.chinaaet.com/images/2015/09/22/6357855258159000005843640.png)

要使得LNA绝对稳定,必须保证K大于1。

2 电路仿真结果及其分析

采用SMIC 0.18 μm CMOS射频工艺,在Cadence软件环境下完成电路各项性能指标的仿真。工作频率为2.4 GHz,在1.5 V工作电压下,电路的静态功耗为8.6 mW。

电路的S参数如图3所示。在中心频率2.4 GHz处,正向传输增益S21为26.26 dB,具有足够的增益,能有效地减小后级电路对噪声的影响。输入反射系数S11为-27.14 dB,输出反射系数S22为-16.54 dB,说明实现了较好的输入输出阻抗匹配。反向隔离度S12为-40.91 dB。LNA的噪声系数仿真结果如图4所示,从图中可以看出,在2.4 GHz的工作频率处,设计的低噪声放大器的噪声系数并不等于最小噪声系数。若要使电路实现噪声的完全匹配,可以通过增加Cex(但会提高电路的最小噪声系数,降低电路的增益)或增加M1的栅宽 (但会增加功耗)来实现。本文所设计的LNA在功耗和噪声系数之间进行了折衷处理,在较低功耗下实现了较好的噪声性能,此时的NF为1.52 dB。本文对LNA的稳定因子Kf也进行了仿真,仿真结果如图5所示。由仿真结果可以看出Kf始终大于1,所设计的低噪声放大器处于无条件稳定。

3 结论

本文采用电流复用技术设计了一个低功耗高增益的低噪声放大器,通过在输入级晶体管的栅源之间并上一个电容Cex,减小了栅极电感的值,降低了芯片的面积。从电路的仿真可以看出,本文设计的低噪声放大器在工作频率2.4 GHz时具有良好的综合性能指标。

参考文献

[1] Abidi A A. RF CMOS comes of age [J]. IEEE Journal of Solid-State Circuits , 2004 , 39 (4) : 549-561.

[2] Madan A, McPartlin M J, Masse C, et al. A 5 GHz 0.95 dB NF highly linear cascode floating-body LNA in 180 nm SOI CMOS technology [J]. IEEE Microwave and Wireless Components Letters,2012,22(4):200-202.

[3] Gray P R, Meyer R G. Analysis and design of analogintegrated circuit( 4th ed)[M]. New York:John Wiley&Sons, 2001.

[4] Lee T H.CMOS射频集成电路设计[M]. 余志平,译. 北京:电子工业出版社, 2006:258-307.

[5] Fujimoto R, Kojima K, Otake S. A 7 GHz 1.8dB NF CMOS low noise amplifier[J]. IEEE Journal of Solid-State Circuits, 2002,37(7):852- 856.

[6] Paul L, Johan I, Michiel S. A 0.8 dB NF ESD-protected 9mW CMOS LNA operating at 1.23GHz[J]. IEEE Journal of Solid-State Circuits, 2002,37(6):760-765.

[7] Belmas F, Hameau F, Fournier J M. A low power inductorless LNA with double gm enhancement in 130nm CMOS[J].IEEE Journal of Solid-State Circuits,2012,47(5):1094-1103.