文献标识码: A

文章编号: 0258-7998(2014)11-0075-03

0 引言

随着数据存储设备被广泛应用于航空航天系统、医疗卫生、工业自动化等各行各业,对于图像设备采集的控制及实时大容量高速存储要求也越来越高。本文以Micron Flash为存储介质,通过FPGA控制实现Camera Link高速接口通信,传输速率可达到100 MB/s,并设计高速数据的流水线式存储方式,实现大容量高速图像存储与实时显示。

1 总体设计

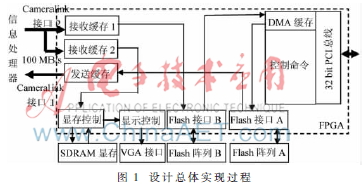

设计的实现过程如图1所示,上位机通过PCI总线下发图像数据并将数据保存在Flash存储阵列A中;上位机指令下发后,FPGA控制Flash A读出存储的数据并通过CameraLink1输出接口发送至信息处理器;待信息处理器处理完数据,再通过CameraLink输入接口2将数据写入到SDRAM显存和Flash存储阵列B中,使能VGA显示后,显示控制循环读取SDRAM中的图像数据进行显示;最后,上位机通过DMA传输将Flash阵列B中保存的数据快速上传至上位机中以作后续处理。

2 高速数据存储管理设计

2.1 Nand Flash

高速存储阵列A/B单元的设计是分别以4片Micron Nand Flash芯片作为存储介质,通过FPGA完成Flash芯片读写时序的控制[1]。Micron Flash MT29F128G08AJAAA内部含有两个CE使能端,每个使能各控制两个相互独立的LUN(4 GB),总容量为16 GB。为便于地址管理,提高数据处理速率,单片MT29F128G08AJAAA内部块操作顺序为(CE1)LUN0、(CE1)LUN1、(CE2)LUN0、(CE2)LUN1,当无效块检测模块检测到坏块时,当前每行4块均认为是无效块,不对其进行操作。

由于Flash芯片每次页编程都需要350 s~560 s的页编程时间,在此期间,不能对当前模块进行操作,这严重制约着持续的数据写入。由此可充分利用每个LUN相互独立操作、互不影响的特点,采用流水线操作方式来复用编程时间,即当前LUN进入页编程操作时,可以对剩下的3个LUN进行写入页寄存器操作,从而提高数据吞吐量[2]。假设Flash的读写周期为20 ns,将数据写入到页寄存器所需的时间为:8 192×20 ns=163.84 s,考虑端口复用写入的地址、命令等时间约为10 s,因此对于单片Flash而言,连续写完4个LUN共需时间为:4×(163.84+10) s=695.36 s,完成一次32 KB数据写入所需总时间最多为695.36 s+560 s=1 255.36 ,即可粗略计算出单片Flash的平均写入速率:32 KB/(1 024×1 255.36 s)=24.9 MB/s。该情况未考虑到第4个LUN写完后,LUN1已经完成了页编程操作,可继续写入,也就是说其持续的写入速度大于24.9 MB/s。

2.2 高速数据的存储

存储器存储的数据来源可分为两类:一类是Camera-

Link2接口输入的高速图像数据,另一类是上位机通过PCI总线下发的图像数据。两类数据的存储方式相同,PCI下发数据速率小于CameraLink2接口输入的图像数据速率,时序上只需要保证CameraLink2输入的数据能写入到Flash B即可满足需求。

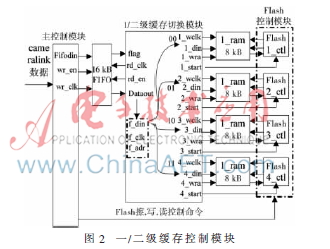

FPGA内部采用两级缓存结构,通过流水线的操作方式实现100 MB/s 图像数据的可靠存储[3]。前一级采用一个16 KB大小FIFO构成的缓存,FIFO为16位,输入时钟为50 MHz;第二级缓存由4个8 KB的双口RAM组成,输入时钟60 MHz,如图2所示为缓存控制模块图。当一/二级缓存切换模块通过flag标志判断16 KB FIFO满足已写入2 000个字,f_adr地址开始累加并以60 MB/s速度从16 KB FIFO连续取出4 096个字,将数据赋给f_din,并模拟产生60 MHz的8 KB RAM写时钟f_clk。而每取完一次4 096个字数据量,f_fifo_adr清零,数据切换标志sw_flag自加1。数据流的方向就是通过sw_flag控制的,当sw_flag为00,01,10,11时,分别将f_din、f_clk、f_adr赋给1_ram 8 kB、2_ram 8 kB、3_ram 8 kB、4_ram 8 kB这4个ram二级缓存。当Flash控制模块判断取数标志1_start~4_start其中之一大于100时,主控制模块控制对应的Flash进入写操作。

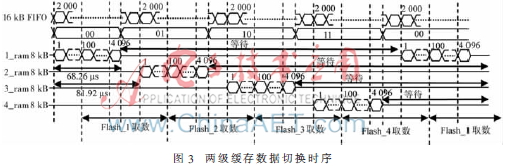

由于一级缓存写入速度50 MB/s,读数速度60 MB/s,写速度小于读速度,不用当心溢出问题。考虑到取数据连续性,避免读空现象出现,合理地选取取数判断标志的大小是关键,而判断标志的大小取决于连续取数的数量大小及写/读数速度。假设数据取空时经历时间为t,取数判断标志大小为flag,则由公式50t+flag-60t=0可知flag=10t。为满足连续取出4 096个字,故t要大于4 096/60=68.26 s,即flag满足大于682.6就可以避免取空现象,考虑留取一定的裕量,选取flag为2 000。同理,当flash1从ram8 kB取数时,由于取数速度50 MB/s小于写数速度60 MB/s,有可能出现溢出现象,通过1_start标志判断1_ram 8 kB满足大于100,Flash1控制模块连续从ram 8 kB中取走4 096字。为保证数据可靠高效的连续性传输,一/二级缓存数据切换的有序配合显得尤为重要,如图3所示为数据切换时序图,从16 KB FIFO到ram数据传输过程为:当16 KB FIFO取数判断标志大于2 000时,从16 KB FIFO以60 MB/s速度连续取出4 096数据存入1_ram 8 kB,需时68.26 s,ram平均取数速度取决于16 KB FIFO写入速度(为50 MB/s,即81.92 s),在ram取数的过程中16 KB FIFO经过81.92 ?滋s之后已经再次写入4 096个数据,16 KB FIFO剩余4 096+

2 000-4 096=2 000个数据量满足取数要求,此时sw_flag自加1指向2_ram 8 kB,以此类推,4个ram循环地写入数据。同理,在ram写入数据的过程中,Flash1控制模块判断ram1取数标志满足100时,连续取出4 096个字,当Flash1取走ram1中4 096个数据时,ram2已经满足取数标志,Flash2开始从ram2中连续取出4 096个字,以此类推,Flash控制单元连续读取4 096字写入到Flash中进行页编程操作,这样就可实现连续的100 MB/s数据写入。

2.3 图像数据的发送

从PCI总线下发存入Flash A的图像数据通过CameraLink1输出接口发送至信息处理器,从Flash取数的过程和写数的方式类似。设置4个8 KB的ram缓存,当接收到开始下发图像指令后,FPGA控制4片Flash完成一次页读取操作,并将数据保存在8 KB缓存中,然后以60 MB/s的时钟读取缓存1中的数据存入16 KB FIFO。当读完缓存1中的8 192 B数据后,依次读取缓存2、3、4中保存的数据,同时以50 MB/s的时钟读取Flash中下一页的数据。Flash以50 MB/s时钟完成一次双平面读数过程所需时间为25 ns+8 192×20 ns+30×20 ns(命令、地址下发时间)=164 885 ns。以100 MB/s的速度读取32 KB数据所需的时间为32×1 024×10 ns=327 680 ns>164 885 ns,也就是说在读完剩下的3个缓存中的数据时候,第一个Flash已完成了一页数据的读取,并将数据存放在缓存1中。因此通过循环读取4个缓存中的数据,即可实现持续的100 MB速度发送图像数据。

3 图像的实时显示

3.1 VGA时序信号产生

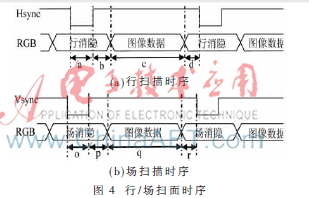

设计VGA图像显示控制需要注意时序的驱动,这是完成设计的关键,时序稍有偏差显示必然不正常甚至会损坏显示器[4]。如表1所示为1 280×1 024×60 Hz图像显示控制各阶段时钟点数,图像时钟频率为108 MHz,其中Hsync信号用来控制“列填充”,可以分为a~d 4个阶段,其中c段1 280点为有效显示区,a段由112个点组成的同步信号负脉冲以及两段行消隐期;Vsync信号用来控制“行扫描”,同样也分为o~r 4个阶段,其中q段1 024行为图像显示行,o段3个时钟为场同步信号负脉冲以及两段场消隐期[5-6]。

对于行同步信号,每行实际像素数为1 688,故行同步信号频率为108 MHz/1 688=63.98 kHz,同理,场同步信号频率为60.02 Hz[7]。如图4所示为行/场扫描时序,结合图4和表1,可以利用FPGA资源构建VGA时序。选取108 MHz的晶振作为脉冲计数器时钟,当像素脉冲计数在小于112脉冲间,Hsync输出低电平,其他时段输出高电平。同时,当像素脉冲计数小于3时,Vsync输出低电平,其他时段输出高电平,对行场同步为低电平的标准,SYNC设计为Hsync和Vsync相与的结果,BLANK信号可做的比SYNC略宽一些。

3.2 显示控制设计

如图1所示,设计中采用高速SDRAM实现对图像数据的高速缓存,从CameraLink接收的图像数据分别存入两个缓存,一个用于高速存储于Flash B阵列中,另一个暂存在SDRAM中,用于实时显示图像。CameraLink接收的图像数据以50 MHz×16 bit的速度存入FIFO1缓存中,当判断FIFO1缓存数据量大于1 280个字时,FPGA控制SDRAM模块以100 MHz×16 bit的速度从FIFO中取出数据存入SDRAM。当接收实时显示图像命令时,SDRAM以165 MB/s速度更新FIFO2中数据,VGA接口以108 MHz速度循环读取SDRAM中所存储的图像数据,对显示器的显示内容进行更新。由于SDRAM写入1 280个字所需时间为12.8 ?滋s,考虑到SDRAM读写操作分时进行,为保证SDRAM在写数期间FIFO2数据不会被读空,FIFO2每次读取1 080字,所需时间20 s,满足SDRAM读写转换及刷新时间,同时VGA显示能以108 MHz速度持续从缓存中读取数据并显示[8]。

4 测试结果与结论

试验结果如图5所示,采用图像模拟器发送一幅1 280×1 024灰度图像的方式对图像存储显示的设计进行验证,并通过DMA方式读取存储在Flash B阵列中的图像数据至上位机中进行画图分析。试验结果表明,高速图像存储卡能实时显示图像,且经过回读数据分析,完整地保存下高速输入的图像数据。利用FPGA控制整个系统的工作时序,通过在内部设置多级缓存结构和流水线操作思想,实现了图像数据在不同时钟域之间的转换,完成了高速图像数据的存储与实时显示功能。本设计可实现持续的100 MB/s数据的实时存储,满足大多数光电设备中CameraLink数据的实时存储要求。

参考文献

[1] 杨柯,范海震.CameraLink接口的高速电子存储系统设计[J].舰船电子工程,2012,32(5):110-118.

[2] 王熙.一个面向航空遥感高速的闪存存储系统设计[D].合肥:中国科学技术大学,2012.

[3] 张海龙,马铁华,谢锐,等.基于双闪存的大容量冲击波超压测试系统[J].电子技术应用,2013,39(11):85-88.

[4] 郑佃好,张红雨,张洪斌.基于ADV7125的嵌入式系统VGA接口设计[J].单片机与嵌入式系统应用,2011,11(8):37-41.

[5] 邓春健,王琦,徐秀知,等.基于FPGA和ADV7123的VGA显示接口的设计和应用[J].电子器件,2006,29(4):37-41.

[6] 廖永清,丁旭昌,付建国,等.基于FPGA的VGA图像动态显示控制器的设计与实现[J].电视技术,2011,35(17):52-54.

[7] 王亮,李正,宁婷婷,等.VGA汉字显示的FPGA设计与实现[J].计算机工程与设计,2009,30(2):275-281.

[8] 周卓然,徐道连,吕凤飞,等.基于FPGA的VGA图像显示系统的设计与实现[J].仪表技术与传感器,2012(7):90-92.